### **CHAPTER 4**

#### **GEOMETRY SUBSYSTEM**

The Geometry Subsystem is responsible for performing the various transformations and lighting computations on world coordinate data received from the host. It then performs any necessary calculations to reduce the subsequent vertex data into points, lines or spans to pass to the Raster Subsystem. It is also responsible for controlling the interface between the host and the other **MGR** Subsystems.

The Geometry Subsystem is the heart of the **MGR** adapter and is responsible for performing the geometry calculations and is also responsible for controlling the operation of the Raster Engine in the Raster Subsystem. The Geometry Engine is a microcode controlled floating point processor that is used to perform the geometry calculations as well as the lighting calculations. The two main components of the Geometry Engine are the microcode sequence controller chip called the HQ chip and the Weitek 3132 Floating Point Data Path chip which does the floating point multiplies and adds. These components along with the other components will be discussed in greater detail in later paragraphs.

The following paragraphs will describe the external interfaces, the major components, the registers, the basic operation and the programming considerations of the Geometry Subsystem.

### **External Interfaces**

The following paragraphs describe the external Interfaces that the Geometry Subsystem has with the Host Interface Subsystem, the Raster Subsystem and the Display Subsystem.

# Host Interface Subsystem Interface

The Geometry Subsystem has an interface with the Host Systemvia the Host Interface Subsystem. The **SGI** Private bus connects these two subsystems and is used to transfer all data to and from the host system. The Geometry Subsystem uses the 10 **Mhz** multi-phase clocks provided by the Host Interface Subsystem for its timing.

# Raster Subsystem Interface

The Geometry Subsystem has a register pointer and a data bus **which** are used to access the Raster Engine in the Raster Subsystem. The Geometry Subsystem also controls the addressing for host accesses of the Cursor Chips in the Raster Subsystem. The Geometry Subsystem controls DMA transfers between the Raster Subsystem, the Geometry Subsystem and the Host System.

# Display Subsystem Interface

The Geometry Subsystem controls the addressing and data transfers between the Host System and the registers in the various components of the Display Subsystem.

# **Major Components**

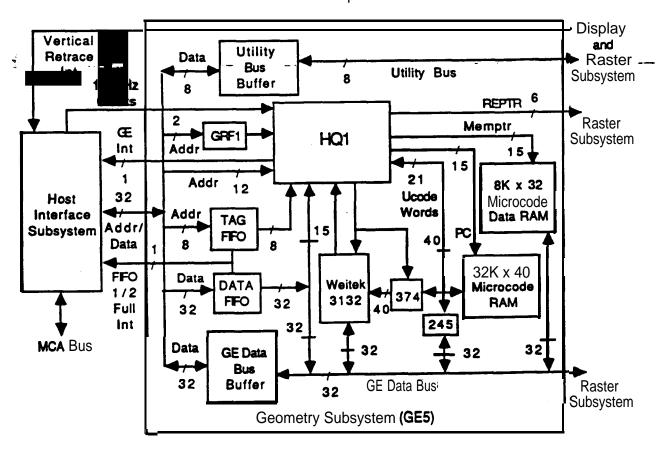

The major components of the Geometry Subsystem are shown in the block diagram of Figure 4.1. The **HQ1** chip controls the address decoding for the host and acts as a microcode sequencer. The Weitek 3132 chip performs the floating point calculations and is controlled by the **HQ1**. The microcode **RAM** holds the microcode, while the microcode data RAM holds constants, data variables and data buffers. These four components form the Geometry Engine **5** (**GE5**) which performs the geometry calculations, lighting calculations and various other functions.

To execute graphics commands the host sends **graphics** command tokens and data to the Geometry Engine. The Tag FIFO and Data FIFO provide a buffer between the host and Geometry Engine speeds. The host can continue to send graphics tokens while the Geometry Engine is still executing previously sent tokens. The Tag FIFO receives the command tokens from the host and passes the command tokens to the **HQ1** chip which uses the token as an index into a microcode branch table. This causes the appropriate microcode routine to be executed for each token. These tokens instruct the microcode to perform the desired operations. The Data FIFO receives the data parameters associated with the various tokens. The microcode executes instructions which read the dataFIFO and transfers the data into either the Weitek 3132 chip or into the GE5 data RAM.

Figure 4.1 Geometry Subsystem Block Diagram

The **GRF1** chip is used to add some additional capabilities to the **HQ1** chip. The GE Data Bus **buffers** and the Utility Bus buffer provide the necessary buffering required for these two databusses. The following paragraphs describe the Geometry Subsystem components.

### **HQ1** Chip

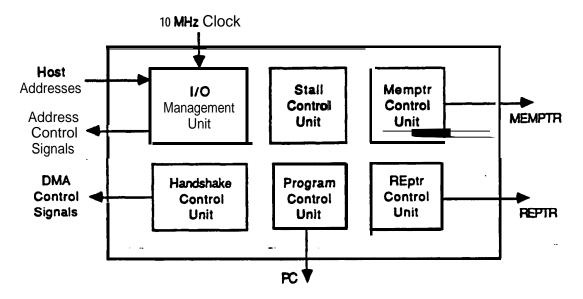

The Head Quarters (HQ1) chip is a proprietary Silicon Graphics design and is the main control element in the Geometry Subsystem. The HQ1 is responsible for controlling the geometry engine and the various data transfers among the MGR hardware components. The HQ1 chip has six functional units as shown in Figure 4.2.

Figure 4.2 HQ1 Functional Block Diagram

The following paragraphs describe these six functional units.

## I/O Management Unit

The **I/O** management unit is responsible for providing the address decoding and bus control for hardware accesses by the Host Interface Subsystem and the Geometry Engine. The host address decoding is shown in Table 4.1. The host can **access** the following hardware components:

- -HQ1 registers

- Tag and Data FIFO

- Microcode Code RAM

- Microcode Data RAM

- 2 Finish Flags

- 2 Cursor Chips

- 5 XMAP2 and 5 Color Maps or 5 XPC1 Chips

- 3 RAMDAC Chips or 1 RGB RAMDAC Chip

- Display Registers

Table 4.1 Host Interface Address Decoding

| ADDRESS RANGE   | HQMMSB | SRC/DEST              | OPERATION | DATA       |

|-----------------|--------|-----------------------|-----------|------------|

| 0x0000 - 0x03FC | 0      | Ucode RAM low 32 bits | FW        | LS 32 bits |

| 0x0000 - 0x03FC | 1      | Ucode RAM high 8 bits | RW        | MS 8 bits  |

| 0x0400 - 0x041C | 1      | XMAP2 channel 0       | RW        | 8 bits     |

| 0x0420 - 0x043C | 1      | XMAP2 channel 1       | ĦW        | 8 bits     |

| 0x0440 - 0x045C | 1      | XMAP2 channel 2       | RW        | 8 bits     |

| 0x0460 - 0x047C | 1      | XMAP2 channel 3       | RW        | 8 bits     |

| 0x0480 - 0x049C | 1      | XMAP2 channel 4       | RW        | 8 bits     |

| 0x04A0 - 0x04BC | 1      | XMAP2 broadcast       | W         | 8 bits     |

| 0x04C0          | 1      | Display Reg 0         | RW        | 8 bits     |

| 0x04E0          | 1      | Display Reg 1         | PW PW     | 8 bits     |

| 0x0500 - 0x050C | 1      | Red DAC               | FW        | 8 bits     |

| 0x0510 - 0x0514 | 1      | XPC1 Channel 0        | RW        | 8 bits     |

| 0x0520 - 0x052C | 1      | Green DAC             | RW        | 8 bits     |

| 0x0530 - 0x0534 | 1      | XPC1 Channel 1        | FIW       | 8 bits     |

| 0x0540 - 0x054C | 1      | Blue DAC              | PW        | 8. bits    |

| 0x0550 - 0x0554 | 1      | XPC1 Channel 2        | PW        | 8 bits     |

| 0x0560 - 0x056C | 1      | Cursor chip 0         | PW        | 8 bits     |

| 0x0570 - 0x0574 | 1      | XPC1 Channel 3        | RW        | 8 bits     |

| 0x0580 - 0x058C | 1      | Cursor chip 1         | FW        | 8 bits     |

| 0x0590 - 0x0594 | 1      | XPC1 Channel 4        | RW        | 8 bits     |

| 0x05A0          | 1      | Display Reg 4         | RW        | 8 bits     |

| 0x05B0 - 0x05B4 | 1      | XPC1 Broadcast        | FW.       | 8 bits     |

| 0x05C0          | 1      | Display Reg 3         | FIW       | 8 bits     |

| 0x05D0 - 0x05DC | 1      | RGB RAMDAC            | PW        | 8 bits     |

| 0x05E0          | 1      | Display Reg 2         | RW        | 8 bits     |

| 0x0640 - 0x780  | 1      | HQ1 Command           | RW        | 15 bits    |

| 0x0800 - 0x0BFC | ×      | FFO                   | RW        | 32 bits    |

| 0x0C00 - 0x0DFC | X      | HQ MAR                | W         | none       |

| 0x0E00 - 0xE04  | ×      | HQ MAR MSB            | W         | none       |

| 0x1400 - 0x17FC | 0      | Ucode Data RAM        | RW        | 32 bits    |

| 0x2000 - 0x2004 | ×      | Finish flags          | PW        | 32 bits    |

The **I/O** management unit uses two registers to help control the **MGR** addressing. The 1 bit **HQ** Middle Address Register Most Significant Bit (HQMMSB) Register is used to control the address

decoding. It is set to either zero or one as shown in Table 4.1. This register's namederives from an earlier implementation when it was bit 7 of the HQ middle address register (MAR). This is no longer the **case**, and the HQMMSB register is addressed independently from the HQ MAR. It can be thought of as the Address Selection Control Register. This register should be set to zero when addressing the low 32 bits of the code RAM or when accessing the data RAM. When accessing the FIFO, the Finish Flags, the HQ MAR register or this register itself the value in the HQMMSB register does not matter. For all other hardware components shown in Table 4.1 the HQMMSB must be set to one before the components can be properly accessed.

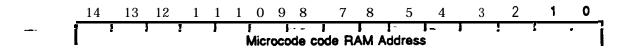

The **HQ1** uses the HQ MAR register as a page selection register when accessing the microcode code and data **RAMs.** The MAR register is used to provide the upper 7 bits of the microcode code or data RAM address. The bwer 8 bits of the microcode code or data RAM address provide the word offset into the page selected by the MAR register. The word offset is obtained from bits 2-9 of the host address. These bits are combined with the page address in the MAR register to form the microcode **code** or data RAM address. The 15 bits **allow** 32K words of microcode code or data RAM to be addressed by the host. The **MGR** adapter has 32K words of code RAM so all 15 bits of the address are valid when addressing the code RAM. The **MGR** adapter has **only** 8K words of data RAM so only 13 bits are valid when addressing the data RAM. This means that only 5 bits in the MAR register are **valid** when addressing the data RAM.

The **VO** management unit decodes the host addresses shown in Table 4.2 and generates the necessary control signals to access the specified Geometry Subsystem components. The host can access the microcode **code** RAM, the microcode data RAM, the HQ Middle Address **Register** (MAR), the HQ MAR Most Significant Bit (HQMMSB) Register and the data and tag FIFO. The host can also issue commands to the **HQ1** to clear the stall condition and to clear the GE interrupt. The host can read the microcode Program Counter (PC) register.

| ADDRESS RANGE   | HOMMSB      | SRC/DEST         | OPERATION    | R/W         | DATA    |

|-----------------|-------------|------------------|--------------|-------------|---------|

| 0x0000 - 0x03   | FC 0        | Ucode RAM low 32 | RW Ucode RAM | FW          | 32 bits |

| 0x0000 - 0x03FC | 1           | UcodeRAMhigh8    | RW Ucode RAM | FW ·        | 8 bits  |

| 0x0840          | 1           | HQ1              | clear stall  | W           | none    |

| 0x0740          | 1           | PC in HO1        | Read HQ PC   | R           | 15 bits |

| 0x0780          | 1           | HQ1              | clear GE int | w           | none    |

| 0x0800 - 0x0BFC | Х           | FIFO             | FIFORW       | RW          | 32 bits |

| 0x0C00 - 0x0DF0 | X           | HO MAR           | Write HQ MA  | R W         | none    |

| 0x0E00 - 0x0E04 | X           | HQ MAR MSB       | Write HQMM   | BB W        | none    |

| 0x1400 - 0x17   | <b>FC</b> 0 | Ucode Data RAM   | RW Data RAM  | RW          | 32 bit: |

| 0x2000          | ΧF          | inish Flag 0     | Read Finish  | 0 <b>FW</b> | 32 bits |

| 0x2004          | Х           | Finish Flag 1 Re | ead Finish 1 | PW          | 32 bit! |

Table 4.2 HQ1 Address Map

Two finish flags are provided to synchronize host accesses to the microcode data RAM with the microcode execution and to synchronize the start of **DMA** operations to or from the adapter. The host **can** read and write the finish flags while the microcode can only write to the finish flags.

The host can only access the GE5 data RAM or code RAM while the microcode is in a stalled state. Finish flag 0 is provided to synchronize the host accesses to the microcode data RAM with the

microcode. The host systems sends a **GE\_FINISHO** token down the FIFO to the microcode to **command** it to set the finish flag when **it** finishes executing the tokens already in the **FIFO**. **The host then** continuously reads address 0x2000 for **finish** flag 0 until finish flag 0 is set by the microcode. When the microcode finishes its current operations and the FIFO **is** empty it sets finish flag **0** and does a fetch from the FIFO which causes it to stall until the host sends another token. The host system can then read or write the microcode data RAM without Interfering with the microcode.

Finish Flag 1 is provided to synchronize the start of DMA operations between the host and the MGR adapter. When the host sends a token to the microcode that will require **DMA** operations the microcode will setup for the DMA and then set Finish F&g 1. The host would poll address **0x2004** until it is set by the microcode and then the host would start the DMA operation. The use of the **finish** flags will be discussed in greater detail later.

#### Handshake Control Unit

The handshake control unit is used to provide the necessary hardware handshake signals between the Host Interface Subsystem, the Raster Engine (RE) in the Raster Subsystem, the microcode code and data RAM and the XMAP2 or **XPC1** chips in the Display Subsystem. It stalls the **GE5** when it is appropriate and passes other handshakes through for accesses such as host to XMAP or host to RE.

The handshake control unit allows two types of transfers between the Host Interface Subsystem and the other MGR Subsystems. These two types of transfers are single word transfers and **DMA transfers**.

The host can access the following components using single word transfers:

- HQ1 PC and HQ1 commands

- tag/data FIFO

- microcode code RAM

- microcode data RAM

- five XMAP2s or five XPC1s

- an RGB RAMDAC or three **RAMDACs**

- five Color Maps

- two cursor chips

- five display registers

The following DMA transfers can occur:

- between the host and the microcode data RAM

- between the host and the Raster Engine

- between the Raster Engine and the microcode data RAM

These data transfers are described in later paragraphs in the appropriate chapters.

#### Stall Control Unit

The stall control unit is responsible for stalling the **GE5** when a condition arises that requires it to be stalled. The full stall keeps the **VO** Management unit in its current state and also keeps the PC, the MEMPTR and the REPTR from changing. The **clock** to the Weitek 3132 is fully suppressed and literally the entire GE5 is stalled. The host can still perform single word transfers as described above.

The following conditions result in a full stall:

**Reset** - Whenever the **HQ1** is reset it goes into a full stall. After the **HQ1** has been reset it needs to be initialized. The host downloads the microcode code and data and then writes to the clear stall address to start the GE5 running. The host software must be aware of this type of stall since it has to issue the clear stall **HQ1** command.

**Burst DMA** transfer • Whenever the **HQ1** detects a host delay, an RE delay or a host burst disable condition it will stall the GE5 until the appropriate handshake conditions exists to continue the DMA transfer. At that time the **HQ1** will clear the full stall and the transfer will continue. This type of stall is transparent to the host software and would only be somewhat evident if the DMA never completed.

**Stall Microinstruction** - The **GE5 microcode** may execute a stall instruction which will put the **HQ1** into a full stall until the host writes to the clear stall address. This can be used to synchronize the microcode with the host for passing data. The host software must be aware of the instances where the microcode would issue a stall microinstruction since it would have to issue the clear **stall HQ1** command.

**Read from Empty FIFO** • When the **GE5** microcode is executing a fetch instruction or a read from data FIFO instruction, the **HQ1** will go into a full stall in the middle of the read or fetch microinstruction if the FIFO is empty. The stall condition will continue until data actually becomes available. This is a stall condition that is frequently encountered and can be used by the host software to access the GE5 data RAM. The **GE\_FINISHO** token is used by the host to guarantee that the microcode has processed all of the data in the FIFO and is stalled at a fetch instruction waiting for the next token to **be** sent by the host software. The host software can then safely **access** the GE5 data RAM **before** sending the next command token.

**Raster Engine** not **ready** - The **HQ1** can load the Raster Engine (RE) registers when the appropriate load enable **signals** are active. If the GE5 microcode attempts to write to an RE register when the load enable signals are not active the **HQ1** will go into a full stall until the load enable signals becomes active. This is a temporary handshake stall between the GE5 and the RE2 and is totally transparent *to* the host software.

#### PC Control Unit

The Program Counter (PC) control unit acts as a microcode sequencer for the **GE5.** The control unit controls the microcode instruction execution sequencing through up to 32K words of microcode. The PC control unit allows branching and conditional jumps. It uses a 15 bit wide PC to access the microcode code RAM. Microcode **instructions** are read from the address pointed to by the PC and are executed by the **HQ1** and the Weitek 3132 chip.

When the host needs to access the **microcode** code RAM it must **access** the bw 32 bits and the upper 8 bits of the 40 bit word separately. The upper 7 bits of the microcode word address are loaded into

the MAR register. The tow 32 bits of the microcode code word are accessed by setting the HQMMSB register to 0. A read or write is then performed and bits 9-2 of the host address are placed in the PC bw byte and the MAR register contents are transferred into the PCs upper 7 bits. The 15 bit PC address is then used to access the bw 32 bits of the microcode code RAM. The same procedure is used to access the upper 8 bits except that the HQMMSB register must be set to 1.

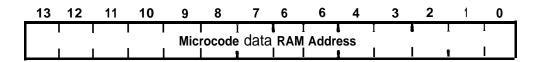

#### MEMPTR Control Unit

The MEMPTR is used as a data pointer for accessing words in the microcode data RAM. The MEMPTR is 14 bits wide allowing a maximum microcode data RAM size of **16K** words. The MGR has only **8K** words of microcode data RAM and each microcode data RAM word is 32 bits wide. The MEMPTR is **loaded** from the microcode **instructions** to perform **microcode** data RAM accesses by the microcode.

When the host wants to access the **microcode** data RAM it sets the HQMMSB to 0. It then loads the MAR register with the upper 6 bits of the microcode data RAM address and does the read or **write** to the appropriate microcode data RAM address. Bits 9-2 of the host address are placed in the MEMPTR tow byte and the MAR register contents are transferred into the **MEMPTRs** upper 6 bits. The 14 bit MEMPTR address is then used to access the microcode data RAM.

#### **REPTR Control Unit**

The REPTR is used as an address pointer to the RE registers. It is used by the **GE5** microcode to load the RE **registers.**—**The** REPTR is not accessible by the host which means that the host cannot directly access the RE registers. A microcode token GE\_LOADRE allows the host to load the RE registers with an assist from the microcode. The host generally does not access the RE register directly and the exceptions will be discussed later.

This concludes our journey inside the **HQ1** chip. We will now continue looking at the other hardware components of the Geometry Subsystem as previously shown in **Figure** 4.1.

#### **FIFO**

The FIFO is used to even the fbw of commands **from** the host and the subsequent command execution by the **GE5**. The FIFO allows the host to continue to send graphics commands and data while the GE5 is still executing a previously received token. The FIFO has space for 512 entries of 40 bits each. The host writes a 32 bit value to a range of FIFO addresses. The 32 bits of data are stored in the Data FIFO and 8 bits from the host FIFO address are stored in the Tag FIFO. Bits 2 through 9 of the host address are placed in the Tag FIFO. The FIFO therefore occupies a **1K** byte range of addresses. The value placed in the Tag FIFO **represents a** command token to the microcode. When the **FIFO** becomes half full an interrupt is generated so that the host can avoid overflowing the FIFO.

### Tag FIFO

The tag FIFO gets host interface address bits 2 through 9 placed in it when the host writes to the FIFO address. The tag FIFO contains the microcode command tokens **which** are used as an index into the microcode command branch table. Sixteen of the 256 possible tokens are **used** to switch to a new graphics context. The other 240 possible tokens are used in conjunction with the FETCH instruction of the microcode to execute microcode commands.

#### Data FIFO

The Data FIFO contains the data parameters passed to the **microcode** for the various command tokens. It can contain 512 words of 32 bits each. When the data FIFO is read, the 32 bit word is placed on the GE5 data bus where it is accessed by the **GE5**.

#### Weitek 3132

· ~

The Weitek 3132 is a floating point data path chip. It provides pipelined floating point multiply and add capability. It also provides 32 working registers to use during the floating point operations. The 3132 is the heart of the **GE5** and is used to perform all geometry and lighting transformations.

#### Microcode Code RAM

The microcode code RAM contains up to 32 K words of microcode. Each word is **40 bits** wide and is **accessed** using the PC in the **HQ1**.

#### Microcode Data Ram

The microcode data RAM contains 8K words of data constants and variables. Each word is 32 bits wide and is accessed using the MEMPTR in the **HQ1**.

## **Utility Bus Buffer**

This is an eight bit transceiver which allows data to pass between the host bus and the utility bus. Only the low byte of the local bus are passed on to the utility bus. The address decoding and control signal generation are handled by**the HQ1.**

#### GE Data Bus Buffer

This is a 32 bit buffer which allows data to **be** passed between the GE5 bus and the host interface. **Single** word transfers use this data path to transfer data between the host and **the** microcode **code** RAM, the microcode data RAM and **the HQ1** PC register. DMA transfers between the host and the microcode data RAM or between**the** host and the Raster Engine **also** us8 this data path.

# **GRF1** Gate Array

This chip is used to provide **the** two finish flags and to correct some other minor design flaws in the **HQ1** chip.

# Registers

The Geometry Subsystem contains the following registers in the HQ1 chip and the Weitek 3132 chip:

- HQ1 Registers

- Middle Address (HQMAR) register

- Middle Address Most Significant Bit (HQMMSB) register

- Program Counter (PC) register

- Previous PC register

- Memptr Register

- Temp Memptr Register

- REptr Register

- DMA Count Register

- Weitek 3132 Registers

- 32 Data Registers

- 3 Temporary Result Registers

These registers are described in the following paragraphs.

## **HQ Middle Address (MAR) Register**

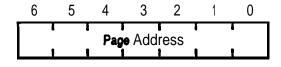

The HQMAR register is the page address register used by the host software to access the 256 word pages of GE5 code and data RAM. The register is 7 bits wide and provides the upper 7 bits of the microcode code and data RAM address. The full address of the word in the code or data RAM is formed by taking the lower 8 bits from bits 2-9 of the host address bus and adding the upper seven bits of the HQMAR register to form the 15 bit address. The us8 of this register wilt be described more completely in the PC and Memptr register diissions later. The HQMAR register can only be written by the host and cannot be read by the host. This means that whenever the host software changes the value in the HQMAR register it must us8 the GE\_HQMSAV token to save the value in the GE5 data RAM location HQMSAV. When a context switch is done this saved HQMAR value is part of the saved context. When the context is later restored the saved value of the HQMAR register is used by the host software to restore the HQMAR register. Figure 4.3 shows the format of the HQMAR register.

\_ Figure 4.3 HQ Middle Address Register \_\_\_\_

Bits 6-O: Page Address (Write Only) - Contains 7 bit page address value used for accessing microcode code or data RAM.

## HQ Middle Address Most Significant Bit (HQMMSB) Register

The HQMMSB register is a 1 bit wide register that is used by the HQ1 chip as an address control bit to control the addressing of the hardware components shown in Table 4.1. The use of this register is shown in Tables 4.1 and 4.2. This register must be set to 0 when accessing the low 32 bits of the GE5 code RAM or the GE5 data RAM. The bit must be set to one when accessing the upper 8 bits of the GE5 code RAM or when issuing an HQ1 command. It must also be set to one when accessing the the hardware components in the Display Subsystem and the Cursor chips in the Raster Subsystem. When accessing the HQMAR register, the HQMMSB register, the FIFO and the Finish Flags the value in the HQMMSB register can be either a zero or a one. The host can only write this register so the host software must make sure it manages the value in this register as needed for each hardware component access. The host software should always clear the HQMMSB register when it is finished accessing a hardware component. The value of this register is determined by the value of the host address bit 2. This means that this register is cleared by writing to address 0xE00 and is set by writing to address 0xE04. The value which is written to these addresses do not affect the clearing or setting of the HQMMSB register.

The name of this register is from an earlier implementation when it was bit 7 of the HQ MAR register. It is now **accessed** independently of the HQ MAR register. The format of the register is shown in Figure 4.4.

Figure 4.4 HQ MAR Most Significant Bit Register

Bit 0: Address Control (AC) Bit (Write Only). Contains a bit used by the **HQ1** in decoding host addresses.

## **HQ Program Counter (PC) Register**

The PC register is a 15 bit wide register which is used by the **HQ1** to access the GE5 microcode code RAM as it sequences through the microinstructions. When the **HQ1** chip is reset as part of the MGR adapter reset the value in the PC register is undefined. The host software &es not have direct write **access** to the PC register but it can load a value into the PC register indirectly by loading a page address into the HQMAR register **and** then reading or writing a word in the code RAM. The tower 8 **bits** of the PC are **loaded** from the host address bits 2-9 and the upper 7 bits of the PC register are **loaded** from the HQMAR register. The HQMMSB register controls whether the bwer 32 bits or the upper 8 bits of the code RAM are accessed. This technique is used by the host software to download the microcode to the adapter.

Once the microcode is downloaded the host bads the HQMAR register with zero and reads code word zero to cause the PC value to be set to zero. The clear stall command can then be issued to cause the microcode to begin executing the microcode hard initialization code. At this point the **HQ1** controls the value in the PC register as it executes the microcode instructions. The host software can read the PC register by issuing the **HQ1** read PC command. The format of the register is shown in Figure 4.5.

Figure 4.5 HQ Program Counter Register

Bits 14-O: Microcode code RAM address. Contains the address of the microcode word which will be accessed by the **HQ1** or by the host system.

## **HQ Previous PC Register**

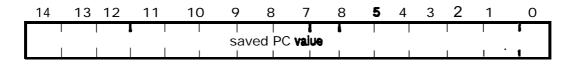

The Previous PC register is a 15 bit wide register which is used by the **HQ1** to save the value int the HO PC register. Normally the use of the previous PC register Is totally transparent to the host software. During the execution of the GE\_CTXO or **GE\_CTX1** tokens the **HQ1** saves the current PC register value. The context switch microcode saves the value In the previous PC register in the GE5 data RAM location PCSAVE. This value is part of the saved context data that is saved **in** the host data RAM. When the host software later restores the saved context **it** uses the value In the PCSAVE **location** while doing the context restore operation. The use of the PCSAVE value will be discussed in the discussion of the **GE\_CTX1** to&en. The format of the register is shown In Pigure 4.6.

Figure 4.6 HQ Previous PC Register

Bits 14-O: Saved PC Value. Contains the saved value from the PC register.

## **HQ** Memptr Register

The Memptr register is a 14 bit wide register **which** is used by the **HQ1** to **access** the GE5 microcode data RAM. When the **HQ1** chip is reset as part of the MGR adapter reset the value in the Memptr register is undefined. The host software does not have the ability to read the Memptr register. The host software also cannot directly **write** to the Memptr register but it **can** load a value into the Memptr register indirectly by loading a page address into the HQMAR register and then reading or writing a word in the data RAM. The lower 8 bits of the Memptr are **loaded** from the host address bits 2-9 and the upper 6 bits of the Memptr register are **loaded** from the HQMAR register. The HQMMSB register must be set to zero while the data RAM is being accessed. Normally the value in the Memptr register is **loaded** by the **microcode** as It executes. The format of the register is shown in Figure 4.7.

Figure 4.7 HQ Memptr Register

Bits 13-O: Microcode data RAM address. Contains the address of the data word which will be accessed by the HQ1 or by the host system.

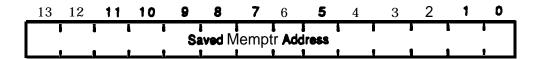

# **HQ Temp Memptr Register**

The Temp Memptr register is a 14 bit wide register which is used by the **HQ1** to temporarily save the Memptr register for a single microcode instruction. The host software does not have the ability to read or write the Temp Memptr register and it is only described here for completeness. The format of the register **is** shown In Figure 4.8.

Figure 4.8 HQ Temp Memptr Register

Bits 13-O: Saved Memptr Value. Contains the saved value from the memptr register.

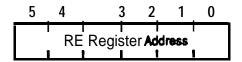

# **HQ REptr Register**

The **Reptr** register is a 6 bit wide register which is used by the **HQ1** to address the registers in the Raster Engine. The host software does not have the ability to read or write the REptr register and it is only described here for completeness. The format of the register is shown in **Figure** 4.9.

Figure 4.9 HQ REptr Register

Bits 5-O: Raster Engine Register Address. Contains the address of an RE2 register to be accessed.

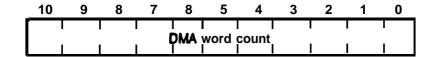

### **HQ DMA** Count Register

The DMA Count register is a 11 bit wide register which is used by the **HQ1** to count the number of words **DMAed** by the **HQ1**. The microcode bads the DMA count into the register and executes a repeatgez instruction which causes the dma transfers to continue while the DMA count register is greater than zero. For each word transfered the **HQ1** decrements **count** in the DMA Count register. The host software does not have the ability to read or write the DMA Count register and it is only described here for completeness. The format of the register is shown **in Figure** 4.10.

Figure 4.10 HQ DMA Count Register

Bits 1 O-O: DMA Word Count. Contains the number of words to be DMAed by the HQ1.

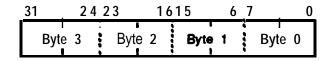

## Weitek Registers

The Weitek chip contains 32 register which are used to store the source data and the results of the floating point multiplies and adds. The chip also contains 3 temporary registers used to hold the results of multiply and add operations. Each of the registers is 32 bits wide and can hold an IEEE format single precision floating point value or a 24 bit sign extended **2's** complement integer value. The host software does not have the ability to read or write the Weitek registers. The format of the register is shown in Flgure 4.11.

Figure 4.11 Weitek Registers

Bits 31-O: Floating Point or Integer Data. Contains the source data and result data of floating point operations by the Weitek.

# Interrupts

The Geometry Subsystem generates two interrupts which can generate an interrupt to the host system. These are the GE interrupt and the FIFO Half-Full interrupt. These interrupts go to the Host interface Subsystem which contains the interrupt mask register and the interrupt status register. Refer to the Host interface Subsystem chapter for a description of these registers and for a description of how a host interrupt is generated.

### FIFO Half-Full Interrupt

The FIFO Half-Full interrupt is generated by the FIFO hardware when it **becomes** half full. The FIFO can hold up to 512 entries and so if 256 entries **are** in the FIFO it generates an interrupt when the next tag/data entry is placed In it. The half full level was chosen to provide adequate time for the host operating system to respond to the interrupt without the FIFO becoming completely full.

### **GE** Interrupt

The GE interrupt is generated by the **HQ1** chip in response to a microcode instruction. **The** microcode causes a GE interrupt to be generated after it completes it's startup **initialization after** the microcode is downloaded. It also generates interrupts during picking and feedback mode each time the **pick/feedback** buffer becomes full. if the GE\_ENDPICK or GE\_ENDFEEDBACK tokens are **sent** the microcode causes a GE interrupt to be generated to tell the host when it can read the final **pick** or feedback data from the buffer.

The **HQ1** latches the GE interrupt and the host must issue a clear GE interrupt HO command to clear the interrupt. This must be done before the interrupt status register GE interrupt bit is cleared to prevent a spurious interrupt to be generated by the Eddy Chip.

# **GE5 Basic Operations**

The Geometry Subsystem contains a single microcoded processor capable of 20 million **floating**-point operations per second (MFLOPS). This processor is referred to as the Geometry Engine (GE) and the **MGR** adapter has the fifth generation version which is referred to as the **GE5**. The basic operation of the GE5 can be viewed at two different levels. The first level is the low level microcode operational level. The second level is the **3D** graphics functional level. The following sections describe these two levels.

### Microcode Operational Level

The GE5 consists of the HQ1, the Weitek 3132, the microcode code RAM, the microcode data RAM and the FIFO. The HQ1 acts the microcode sequencer and uses the PC register to read microcode words from the code RAM. The Weitek 3132 is used to perform the floating point arithmetic needed to perform the 3D graphics operations. The data RAM is holds various constants, variables and data buffers needed by the microcode. The FIFO is used by the microcode *to receive* host command tokens and data parameters. The tokens instruct the microcode to perform the necessary graphics operations.

The microcode instructions are either one or two 40 bit words. The 40 bit microinstruction fields provide control for the Weitek 3132 chip, the PC control unit, the REPTR, the MEMPTR and the various GE5 data paths. Most instructions use only a single 40 bit word format. However, some instructions such as conditional and unconditional branches require a second 40 bit word as part of the microinstruction. This second 40 bit field is used for constants, for target addresses for branches, for values to load in the MEMPTR, for values used to set the interrupt bits and for control values for the DMA channels.

Since the microcode is executed from RAM it must be downloaded by the host into the microcode code RAM. The host reads a file called **ge5\_re2.bin** which contains the microcode code and data constants. Before doing the download the host issues a reset command to the MGR adapter which stalls the GE5 and resets the other hardware components. The host then writes the microcode code into the code RAM and the data constants into the data RAM.

The microcode contains a branch instruction at location zero to an initialization routine. The host reads location zero of the code RAM which causes the PC register to be loaded with zero. The host then clears the **GE5** stall condition. The microcode executes the initialization routine. When the initialization is completed the microcode issues a GE interrupt to the host and does a **stall** instruction. Meanwhile the host polls the interrupt status register waiting for the GE interrupt to occur. Once the GE interrupt occurs the host issues a clear GE interrupt command to the **HQ1** and then issues a clear stall command to cause the microcode to start executing.

The microcode expects the host to send down three parameters at this point. The first parameter informs the microcode if the extended bitplanes are installed. A zero means that the extended bitplanes are not installed and a one means that they are installed. The second parameter indicates if the Z buffer bitplanes are installed. A zero means that they are not installed and a one means that **they** are installed. The third parameter indicates if the VRAM is 256K or 1 Meg chips. A zero indicates 256K and a *one* indicates 1 Meg chips. Refer **to** the Display Subsystem chapter for information on how to read the display registers to determine this infonation. At this point the microcode loads these parameters into the appropriate Raster Engine registers and does a token FETCH instruction from the tag FIFO.

The microcode is organized as a branch table in low memory and the corresponding routines above the table in the microcode code RAM. The microcode does FETCH instructions to get comman**t**bkens

from the tag FIFO. Each FETCH causes the **HQ1** to read an eight bit quantity from the **tag** FIFO. The **HQ1** shifts the token left by one bit to form an index into the branch table and toads the index into the PC. The left shift is necessary because each branch instruction in the table takes **two** 40 bit microcode word locations.

The microcode branch instruct&n is executed by the **HQ1** which causes the corresponding routine higher up in the microcode RAM to be executed. The **HQ1** executes the microcode instructions contained in the routine to perform the desired function. The last instruction in the routine **will** be a FETCH instruction. This causes the **HQ1** to get the next token from the tag FIFO. This sequence is repeated as **long** as the host continues **to** send tokens down the FIFO.

If the command token requires data parameters the appropriate microinstructions are performed to read the 32 bit words from the data FIFO. The microcode can access the microcode data **RAM** as needed for access to constants, **variables** and data buffers. The microcode also accesses the **various** Raster Engine registers as needed to perform drawing operations.

The microcode can also execute jump to subroutine and return from subroutine **instructions to** allow the microcode to contain subroutines of commonly used code. The return address is saved on an 8 level stack in the **HQ1**.

Any further discussion of the operation of the microcode is beyond the scope of this document. The following section describes the **3D** functions implemented by the microcode.

\_.

## 3D Graphics Operations

The MGR adapter provides support for the drawing of a wide range of 3D geometric objects. The objects can be drawn with a variety of attributes and can be solid filled using either flat shading or Gouraud shading. Support is also provided for drawing objects with multiple lighting **sources** with various lighting parameters specified for the surface characteristics of the objects being drawn. The GE5 microcode performs the necessary coordinate transformations from world coordinates to device coordinates and controls how the Raster Engine performs the pixel rendering operations using either RGB or color index pixel formats. The microcode supports a single graphics context and provides the necessary support for switching between multiple graphics contexts.

The GE5 processes a stream of command tokens and data **which** control the operation of the adapter. As each token is executed the microcode performs the various coordinate transformations and pixel rendering operations specified by the tokens and data. The various graphics context parameters in the GE5 data RAM are updated as necessary as the **various** tokens are executed. The appropriate Raster Engine registers are loaded to specify the drawing parameters and then the instruction register is loaded to cause the Raster Engine to perform a drawing operation.

The following functional operations are supported by the MGR adapter:

- Window Management Support

- Graphics Context Support

- Coordinate Transformations

- Drawing of World Coordinate Geometric Objects

- Drawing of Screen Coordinate Objects

- Lighting Support

- Feedback Support

Picking and Selecting Support

Pixel Rendering Support

These functional operations are described'in the following sections.

## **Graphics Resource Management**

The host operating system must provide the necessary operating system software to manage the graphical resources provided by the **MGR** adapter. The graphical resources which need to be managed include:

- On screen windows

- Current graphics context state information

- 2 DMA channels

- . 2 Cursor Chips

- XPC1 or XMAP2 mode registers

- Color map tables

- DAC color palettes

The management of the DMA channels is discussed in the Host Interface Subsystem chapter. The management of the mode registers, the color maps and the DAC color-palettes are discussed in the Display Subsystem chapter. The management of the cursor chips is discussed in the Raster Subsystem chapter. The following paragraphs describe the management of the on screen windows and the graphics context.

## **Window Management**

If the host software wants to provide multiple graphics applications with the ability to simultaneously share the MGR adapter it must provide a window manager which controls multiple on screen windows. The window manager must manage the window creation and manipulation requests of the various graphics processes as they execute. The window manager provides multiple on screen windows by using the Window ID bitplanes and the hardware screen mask to control which bitplanes the graphics applications can write to. The window manager must also provide the user interface for controlling the appearance and location of the on screen windows.

The **MGR** adapter provides 2 **WID** bitplanes on the base adapter and 4 **WID** bitplanes for the enhanced adapter. This means that the base adapter **can** have up to 4 on screen windows and the enhanced adapter can have up to 16 on screen windows. If the fast **Z** clear mode is enabled on the enhanced adapter then the number of on screen windows is limited to 8 since two window **IDs** are used for each window in this mode.

The Window Manager can use the tokens shown in Table 4.3 to control the **WID** bitplanes and the hardware screen mask. The **WID** bitplanes allow a bit by bit control of which pixels can be written into. This allows very complex windows to be managed by the window manager. The hardware screen mask is used to clip all pixel writes outside of the specified rectangular area.

Token

GE\_CURRENTWID

Specifies the current WID to use during window ID checking

GE\_ENABLWID

Used to enable the WID checking of lines

GE\_ENABWID

Used to enable WID checking for other drawing except lines

GE\_FLATMODE

Used to specify the span drawing mode and RE2 DX parameters

GE\_SCRMASK

Used to specify the hardware screen mask rectangular coordinates

GE\_SETPIECES

Used to set a clipping piece list used by GE\_SCREENCLEAR token

Table 4.3 Window Management Tokens --- -

The MGR adapter provides Window ID bitplanes which **can** be used to control pixel writes by the Raster Engine. The Window Manager writes the window ID for each on **screen** window into the **WID** bitplanes at the appropriate locations. The **GE\_CURRENTWID** token is then used to specify which Window ID is currently active. if **WID** checking has been enabled then the current **WID** will be wmpared with the data in the **WID** bitplanes and only those pixels where the current **WID** is the same as the **WID** data will be written. The GE\_ENABWID token controls the **WID** checking for the shaded span and write buffer instructions of the Raster Engine. The GE\_ENABLWID token controls the **WID** checking for the Draw tines instructions of the Raster Engine. These instructions are described in greater detail in the Raster Subsystem chapter.

The GE\_SCRMASK token specifies a rectangle which is loaded into the Raster Engine screen mask registers. The screen mask is used to clip all pixel writes for pixels whose location is outside Of the screen mask rectangle. The screen mask clipping is always enabled for all of the **Raster** Engine instruction which write pixels. If no screen mask clipping is desired then the screen mask rectangle should be set to **the** full screen dimensions.

The **WID** checking operations cause the Raster Engine instructions to draw tokens slower than when **WID** checking is not enabled. **The** use of the screen mask or **WID** checking to perform **pixel** writ8

clipping is dependent on the shape of the currently active window. If the current window is unobscured (a single 1 piece window) then the screen mask can be used to clip pixel writes which are outside of the window. If the window is partially obscured by other windows then the WID checking must be enabled to clip pixel writes.

Since the WID checking performance is most noticeable for screen clear operations a special optimization mechanism is provided by the GE5 microcode. This mechanism consists of the piece list which is set using the GE\_SETPIECES token. This token allows the window manager to specify up to four rectangular clipping masks which are used by the GE SCREENCLEAR and the GE CZCLEAR tokens. If the current window is unobscured or obscured with only 2 to 4 rectangular &es then the piece list is used to control pixel clipping so that only the pieces of the current window are cleared. If the window is divided into more than 4 rectangular pieces or is a non-rectangular shape then WID checking must be used to control the pixel clipping. The SIMPLE flag in the GE5 data RAM controls whether WID checking or the piece list control the screen clear pixel clipping. If the current window contains from one to four rectangular pieces then the SIMPLE flag is set to 1. If the window is divided into more than 4 rectangular pieces or the window is non-rectangular then the SIMPLE flag is set to -1. The discussion below describes how the SIMPLE flag is written into the current context or a saved context.

The GE\_FLATMODE token is used to specify if the flat span instruction or the shaded span instruction is used to draw filled polygons. The flat span instruction is faster than the shaded span instruction but it does not allow window checking operations to be performed. The flat span instruction can not draw shaded spans. The shaded span instruction can be used to draw either shaded or flat spans which can be WID checked. The GE\_ENABWID token can be used to enableWID checking all the time for shaded spans and the GE\_FLATMODE token can be used to specify whether the shaded or flat span token is used to fill polygons. If the GE\_SHADEMODEL token specifies shaded fill mode then GE\_FLATMODE token will be ignored and the shaded span instruction will be used. If the GE\_SHADEMODEL specifies a flat mode then the GE\_FLATMODE token will control whether the flat span or the shaded span will be used to fill the polygon. If the window is obscured and WID checking is needed then the **FLATMODE** parameter of GE FIATMODE will be set to 1 to indicate that the shaded span instruction should be used. In this case the FLATDX parameter will be Set to 0x4000 for the RE2 **DX** register. If the window is unobscured then the **FLATMODE** parameter is set to 2 to indicate that the flat span instruction should be used to fill the polygon. The FLATDX parameter would be set to 0 for this case.

The window manager can use the tokens described **above** only for the current graphics context. However for the other windows whose shapes have changed the window manager can not use the tokens described above to change the window management parameters. These tokens can only be used for the current context if the window manager can guarantee that the graphics application is not in the process of sending a data parameter stream for a token. A better approach would be to update the parameters in the saved context in memory and then have these changes take affect when the context is restored. For the current context this could be done by having the window manager switch out the current context, change the parameters and then switch the context back into the adapter. The parameters which are changed in the saved context are shown in Table 4.4.

The **ENABLWID** parameter Is used to **enable** or disable line WID checking. The shaded span WID checking would always be enabled as described above. The **FLATMODE** and **FLATDX** parameters are used the same as described above. The NEWORG parameter is a flag which instructs the context restore microcode to recalculate the screen mask and **viewport** parameters. If NEWORG is set to 1 the recalculation is performed and if NEWORG is -1 then the recalculations are not performed. The XORG and YORG parameters are used to specify the lower left comer of the window. The SIMPLEflag is used as described above. Finally the last 17 parameters are the piece list count and the specifications for the 4 piece rectangles. The 24 parameters are stored contiguously in the saved context and can be written from an array into the context data area.

Table 4.4 Window Control Parameters in the Context

| Address   | Description                                                                |  |

|-----------|----------------------------------------------------------------------------|--|

| ENABLWID  | Controls whether line WID checking is enabled or disabled                  |  |

| FLATMODE  | Controls polygon fill shade mode (flat fill or shaded fill)                |  |

| FLATDX    | Specifies the RE2 Span parameter specifying the DX value                   |  |

| NEWORG    | Indicates if the viewport or screen mask parameters have changed           |  |

| XORG      | Specifies the lower left x screen coordinate of the current window         |  |

| YORG      | Specifies the lower left y screen coordinate of the current window         |  |

| SIMPLE    | Indicates if the piece list or WID checking is used by screen clear tokens |  |

| NUMPIECES | Indicates the number of pieces into which the window is divided            |  |

| YLEN1     | Specifies the y direction length of the first piece                        |  |

| LLY1      | Specifies the lower left y screen coordinate of the first piece            |  |

| XLEN1     | Specifies the x direction length of the first piece                        |  |

| LLX1      | Specifies the lower left x screen coordinate of the first piece            |  |

| YLENS - V | Specifies the y direction length of the second piece                       |  |

| LLY2      | Specifies the lower left y screen coordinate of the second piece           |  |

| XLEN2     | Specifies the x direction length of the second piece                       |  |

| LLX2      | Specifies the lower left x screen coordinate of the second piece           |  |

| YLEN3     | Specifies the y direction length of the third piece                        |  |

| LLY3      | Specifies the lower left y screen coordinate of the third piece            |  |

| XLEN3     | Specifies the x direction length of the third piece                        |  |

| LLX3      | Specifies the lower left x screen coordinate of the third piece            |  |

| YLEN4     | Specifies the y direction length of the fourth piece                       |  |

| LLY4      | Specifies the lower left y screen coordinate of the fourth piece           |  |

| xLEN4     | Specifies the x direction length of the <b>fourth</b> piece                |  |

| LLX4      | Specifies the lower left x screen coordinate of the fourth piece           |  |

The programming considerations for the  $\overline{\text{WID}}$  bitplanes are described in the Raster  $\overline{\text{Subsystem}}$  chapter.

### **Grap hics Context Management**

The MGR adapter provides hardware and microcode support for only a single graphics contexts of the host operating system supports **multitasking** operations then it must perform a graphics context switch when the current graphics process is made **inactive** and another process is activated. When switching contexts the current graphics context must be saved in the host data RAM and a different context must be loaded into the adapter and made active. The host operating system maintains the appropriate data structures to **allow** the current state information to be saved and a new context switched to. The exact nature of these data structures is beyond the scope of this document and will only be described in terms of the data which must be maintained for the proper operation **of** the adapter.

The graphics context contains various state information which represents the current state of the MGR adapter. The graphics context state information **is** maintained in both the host data RAM and **in** the MGR adapter. The host data RAM contains the state information which describes the window manager state for the various windows be displayed on the adapter and the state of the *Host* Interface and Display Subsystems. The adapter maintains the current state information for the Geometry Engine and the Raster Engine.

The graphics context consists of the following state information:

- 🚅 Host maintained state-. ....

- Current Context

- graphics state maintained by graphics application (such as the SGIgI)

- Window Manager state information

- Host interface Subsystem state

- Display Subsystem state

- Saved context state for each inactive process

- Adapter maintained state for current context

- GE5 operational state

- current contents of the Weitek registers

- current contents of the Raster Engine registers shadowed in **GE5** data RAM

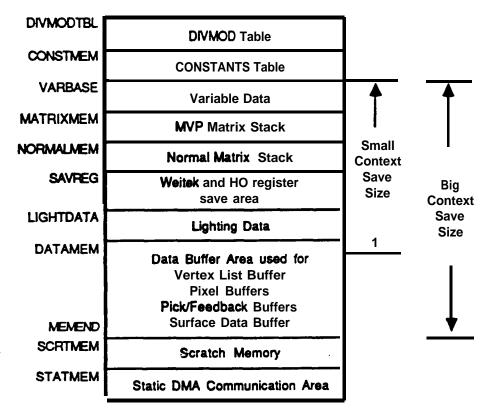

The GE5 data RAM layout is shown **in** Fiiure 4.12 and the symbolic names of the address are defined in the file **ge5\_glob.h.** This header file also defines the **individual** address offsets **in** the variable data area and the other areas. The DIVMOD table is used by the microcode to format the X screen coordinates into the format required by the Raster Engine. The Constants table is used to hold constants information required by the **GE5** microcode as it executes. The DIVMOD and Constants tables are not part of the graphics context since they can be considered as read only constants.

Figure 4.12 GE5 Data RAM Layout

The graphics context area includes the following data:

- the variable data area

- the Modeling/Viewing/Projection matrix stack

- the Normal matrix stack

- the' register save area

- lighting data area

- data buffer area

The **variable** data area contains the state information of the GE5 microcode as it executes the various tokens that it receives. This area contains the following types of data:

- current color data

- current graphics position

- current character position

- current viewport data

- current screen mask data

- shadow RE2 register data

- window manager data (as defined in the previous section)

- various branch and mode flags

The window manager data described in the previous section is one area of the saved context that is manipulated by the host software. The additional data items shown in Table 4.5 are also accessed by the host software. The window manager sets the current **WID** in the saved context by writing to the **CURWID** data location in the context. The other data items are used by the host software which does the context switch. The **use** of these data locations are described in the programming considerations **for** graphics contexts in **the** Programming Considerations section of this chapter.

Table 4.5 Context Data Accessed by the Host

| į  | Address | Description                                                  |

|----|---------|--------------------------------------------------------------|

|    | CURWID  | Contains the current WID data                                |

|    | HQMSAV  | Contains the HQM MAR register value to be restored           |

| 7. | MEMPTR  | Contains the GE5 memory pointer when the context was saved   |

|    | PCSAVE  | Contains the saved microcode Program Counter                 |

|    | REPTR   | Contains the RE2 register pointer when the context was saved |

H

The host software should not change any other data in the saved context besides those described above. **The** host software can access other areas of the GE5 data RAM to get return data from the **microcode** as it executes tokens. These data locations are described for the individual **tokens** and are summarized at the end of the Token Definitions chapter.

**Since** the **MGR** adapter can only contain a single context it is necessary for the host **software** to maintain the appropriate data structures to hold saved contexts for graphics processes which have been switched out of the adapter and saved in the host memory. After the host switches out a context it restores a previously saved context or initializes a new context. The tokenshown in Table 4.6 are used to perform **the** context switching and context initialization.

Table 4.6 Context Switch Tokens

| Address | Description                                                        |  |

|---------|--------------------------------------------------------------------|--|

| GE_CTX0 | Initiates a Context Switch                                         |  |

| GE_CTX1 | Initiates a Context Switch (in case first token is not recognized) |  |

| GE_INIT | Initializes a new context                                          |  |

The **GE\_CTX0** and the GE **CTX1** tokens are used to initiate a context switching operation. The use of **these** tokens is described% the Programming considerations section of this chapter. The **GE\_INIT** token is **used** to initialize a new context. This token causes the microcode to set all of its mode flags to their default conditions and to initialize the various data structures. The **GE\_INIT** token definition defines **the** default settings for **the** various microcode data variables.

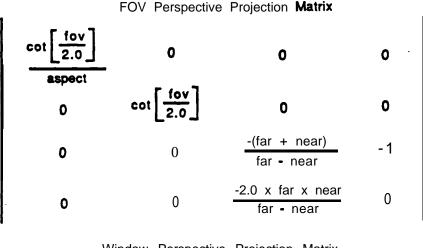

### **Coordinate Transformations**

The **MGR** adapter provides support for three types of coordinate systems which include the world coordinate system, the normalized coordinate system and the device coordinate system. The world coordinates are specified as (x, y, z) triplets with values which **are** appropriate to the objects being drawn. The world coordinates can be specified using either floating point or integer values but the integer values will be converted to floating point by the microcode. The transformations performed on the world coordinates are always done in floating point. The world coordinate system uses **a** right handed system in **which** the positive x axis is to the right, the positive y axis is up and the positive **z** axis toward the viewer.

The GE5 microcode provides support for the necessary matrix transformations to transform 3D world coordinates into device coordinates for use by the Raster Subsystem during the pixel rendering operations. The microcode manages a 16 level 4 x 4 matrix stack which contains the concatenated modeling, viewing and projection matrices which are used to transform the 3D world coordinate data to the 3D normalized coordinates. The normalized coordinates are clipped against a bounding cube which has the dimensions of -1 to +1 along each of the 'x, y and z axis. Once the normalized coordinates have been clipped against the normalized viewing volume they have the perspective division applied to them. The perspective division consists of dividing the transformed x, y and z coordinate values by the transformed w coordinate value. Finally the coordinates are multiplied by the device scaling factors specified by the viewport specification. The viewport advice coordinates.

The **MGR** adapter also provides a corresponding 16 level 3 x 3 matrix stack of normals for lighting surface normal transformations. The use of the normal matrix stack is described in the later section on lighting support.

The tokens shown in Table 4.7 are provided for the coordinate transformations. The **GE\_LOADMATRIX** token Is used to load the initial projection matrix on the Modeling/Viewing/Projection matrix stack. The projection matrix can be either a perspective or orthographic projection matrix. The GE **MULTMATRIX** token is used to concatenate the viewing and modeling matrices with the project&n matrix on the top of the MVP matrix stack. The GE\_PUSHMATRIX token is used to push **the matrices** on the MVP stack down one level. The current top of the matrix stack is left unchanged. The GE\_POPMATRIX token is used to pop the matrices on the MVP stack up one level. The previous current top of the stack matrix is overwritten.

Token

GE\_LOADMATRIX

Loads the initial coordinate transformation matrix

GE\_LOADVIEWP

Loads the viewport device coordinate mapping values

GE\_MMODE

Used to control the transformation matrix stack mode

GE\_MULTMATRIX

Multiplies the current transformation matrix with another matrix

GE\_POPMATRIX

Used to do a pop operation on the matrix stack

GE\_PUSHMATRIX

Used to do a push operation on the matrix stack

Table 4.7 Coordinate Transformation Tokens

The **GE\_MMODE** token is provided to support lighting calculations. When it is set to single mode the MVP stack is not connected in any way to the normal matrix stack. When the matrix mode is set to

viewing or projection mode then the push and pop operations cause both the MVP and normal matrix stacks to be pushed or popped. The use of the **GE\_MMODE** token is described in greater **detail** in the section on lighting support.

The **GE\_LOADVIEWP** token is used to specify the scaling and translation factors applied to the normalized coordinates to transform them to device coordinates. The translation factors are added to the origin of the current window so that the resulting device coordinates are window relative.

The tokens shown in Table 4.8 are provided by the GE3 microcode to assist in the development of a PHIGS graphics package. These tokens are not used by the Graphics Library supplied by Siiiin Graphics. The tokens use the bottom six levels of the MVP matrix stack for their operations. These tokens are defined in the Token Definitions chapter.

Table 4.8 PHIGS Matrix Support Tokens

| Token            | Description                                                       |  |

|------------------|-------------------------------------------------------------------|--|

| GE_COMPOSEMATRIX | Used to concatenate two matrices on PHIGS matrix stack            |  |

| GE_COPYMATRIX    | Used to copy a matrix from one location to another on PHIGS stack |  |

| GE_LOADTOPMATRIX | Used to copy a matrix to the top of the PHIGS matrix stack        |  |

| GE_SETMATRIX     | Used to load a matrix on the PHIGS matrix stack                   |  |

# Drawing World Coordinate 3D Geometric Objects

The GE5 microcode provides support for drawing geometric objects whose coordinates are specified either in world or screen coordinates. The microcode provide support for drawing the following world coordinate geometric objects:

- points

- lines and poiyiines

- closed polyiines

- filled polygons

- triangle meshes

- curves

- NURBS

- screen aligned boxes

- text characters

The following paragraphs describe the world coordinate geometric drawing support provided by the microcode. The screen coordinate drawing support is described in a later section.

## **Current Graphics Position**

The current graphics position **specifies the starting position** where the next line drawing operation begins. After the line drawing operation is **completed** the current graphics position is updated to the **end** of the line position. The point drawing operations also update the current graphics **position to** the specified point position.

## **Point Drawing**

The GE5 microcode supports the drawing of points whose location is specified in world coordinates. The point is one pixel wide and after the point is drawn the current graphics position is updated to the location specified for the point. The tokens shown in Table 4.9 are provided for drawing points.

Table 4.9 Point Drawing Tokens

| Token          | Description                                                 |  |

|----------------|-------------------------------------------------------------|--|

| GE_PNT2        | Draw point at absolute floating point 2D coordinate         |  |

| GE_PNT2I       | Draw point at absolute integer 2D coordinate                |  |

| GE_PNT3        | Draw point at absolute floating point 3D coordinate         |  |

| GE_PNT3I       | Draw point at absolute integer 3D coordinate                |  |

| GE_PNT4        | Draw point at absolute homogeneous coordinate               |  |

| GE_PNT4I       | Draw point at absolute homogeneous coordinate               |  |

| GE_SMOOTHPOINT | Used to enable or disable the drawing of antialiased points |  |

The location of the points- can be specified in either floating point or integer coordinates. The integer coordinates are converted to floating point values by the microcode. The coordinate location is an absolute coordinate which can be specified in **2D**, 3D or homogeneous coordinates. The **2D** coordinate specifies a row vector [x y 0 1] in which the z element is 0 and the w element is 1. The **3D** coordinate specifies a row vector [x y z 1] in which the w element is 1. The homogeneous coordinate specifies a row vector [x y z w] in which the w element is specified by the host software.

The **GE\_SMOOTHPOINT** token is used to enable or disable the drawing of antialiased lines.

## Line and Polyline Drawing

The GE5 microcode provides support for drawing lines and polylines. The line drawing begins by specifying a current graphics position and then issuing one or more line drawing tokens. The tokens shown in Table 4.10 are provided for setting the current graphics position.

Token Description GE MOVE2 Set current graphics position using floating point absolute 2D coordinates GE MOVE21 Set current graphics position using integer absolute 2D coordinates GE MOVE3 Set current graphics position using floating point absolute 3D coordinates GE\_MOVE3! Set current graphics position using integer absolute 3D coordinates GE\_MOVE4 Set current graphics position using floating point homogeneous coordinates GE MOVE41 Set current graphics position using integer homogeneous coordinates GE RMOVE2 Set current graphics position using floating point relative 2D coordinates Set current graphics position using integer relative 2D coordinates GE\_RMOVE2I GE RMOVE3 Set current graphics position using floating point relative 3D coordinates GE RMOVE31 Set current graphics position using integer relative 3D coordinates

Table 4.10 Set Current Graphics Position Tokens

The new current graphics position can be specified in either floating point or integer coordinates. The Integer coordinates are converted to floating point values by the microcode. The new graphics position can be specified as either an absolute coordinate or a relative coordinate. The absolute coordinate replaces the current graphics position with the new coordinate position. The relative coordinate is added to the current graphics position to create the new current graphics position. The coordinates can be specified in 20.30 or homogeneous coordinates. The 2D coordinate specifies a row vector [x y 0 1] in which the z element is 0 and the w element is 1. The 30 coordinate specifies a row vector [x y z 1] in which the w element is 1. The homogeneous coordinate can only be specified in the absolute format and specifies a row vector [x y z w] in which the w element is specified by the host software.

The line drawing tokens are shown in Table 4.11. A single line is drawn by sending one of the draw tokens which causes a line to be drawn from the current graphics position to the coordinate position specified with the draw tokens. After the line is drawn the current graphics position is updated to the end of the line coordinate. To draw **polylines it** is only necessary to set a current graphics position with the move tokens shown above and then send multiple draw tokens. The current graphics position is updated to the end of the last line drawn.

The draw tokens can be specified in either absolute or relative forms using either floating point Or integer coordinates. The coordinate specifying where the line is to be drawn to can be specified in **2D, 3D** or homogeneous coordinates.

The lines can be drawn with many different attributes as shown in Figure 4.12. The GE **ANTIALIASE** token allows the enabling or disabling of the antialiased line drawing mode. The antialiased lines have a smoother appearance but take longer to draw. The **Z** compare hardware in the RE2 can be used to improve the appearance of intersecting antialiased lines. Refer to the **Z** Buffer support section later in this chapter for additional details.

Token Description **GE DRAW2** Draw line from current GPOS to absolute floating point2D coordinates GE\_DRAW2I Draw line from current GPOS to absolute integer 2D coordinates GE DRAW3 Draw line from current GPOS to absolute floating point 3D coordinates GE\_DRAW31 Draw line from current GPOS to absolute integer 3D coordinates GE DRAW4 Draw line from current GPOS to absolute homogeneous coordinates GE\_DRAW41 Draw line from current GPOS to absolute homogeneous coordinates **GE\_RDRAW2** Draw line from current GPOS to relative floating point 2D coordinates GE\_RDRAW2I Draw line from current GPOS to relative integer 2D coordinates GE RDRAW3 Draw line from current GPOS to relative floating point 3D coordinates Draw line from current GPOS to relative integer 3D coordinates **GE RDRAW3**1

Table 4.11 Line Drawing Tokens

The GE\_DEPTHCUE token is used to enable or disable depth cued lines. The GE\_RGBSHADERANGE token is used to set the depth cued shade range for RGB pixels while the **GE\_SHADERANGE** token is used to set the **depth** cued shade range for Color Index pixels.

| Token            | Description                                                         |  |

|------------------|---------------------------------------------------------------------|--|

| GE_ANTIALIASE    | Used to enable or disable antialiase line drawing mode              |  |

| GE_DEPTHOUE      | Used to enable or disable depth cued line drawing                   |  |

| GE_LINESTYLE     | Used to set the line stipple pattern                                |  |

| GE_LINEWIDTH     | Used to set the line width in pixels                                |  |

| GE_LSREPEAT      | Used to set the repeat factor for the bits in the line stipple      |  |

| GE_RESETLS       | Used to cause the line stipple pattern to be reset                  |  |

| GE_RGBSHADERANGE | Used to set the depth cue color shade range for RGB pixels          |  |

| GE_SHADERANGE    | Used to set the depth cue color shade range for Color Index pixels  |  |

| GE_SUBPIXEL      | Used to enable the calculation of sub pixels during antialiase mode |  |

Table 4.12 Line Attribute Tokens

The **GE\_LINEWIDTH** token is used to specify a wide line which covers multiple adjacent pixels. The lines can also be drawn with a stipple pattern applied to them. The **GE\_LINESTYLE** token is used to specify a line stipple pattern and the GE\_LSREPEAT token is used to **specify** a count of **how many** times each pixel in the stipple pattern will be used as the line Is drawn. The **GE\_RESETLS** token is a flag which causes the stipple pattern to be reset for each line drawn. Refer to the Raster **Subsystem** chapter for additional details on the use of stipple patterns in line drawing.

The polylines tokens can be used to draw several higher level unfilledgeometric objects such as:

- circles

- arcs

- ellipses

The circles and arcs can be drawn by **dividing** the circle or arc into a large number of small line segments and then issuing the move and draw tokens. **This** technique can also be used to draw elliptical shapes. The dosed **polyline** tokens **described** in the *next* paragraph automatically save the first coordinate and draw a closing line segment from the end of the last line segment to the beginning of the first line segment. The arc drawing would need to use the open **polylines** since the end line segment does not connect back to the beginning line segment. The drde and ellipse drawing could perhaps be better done **with** the dosed **polylines** but are shown here since this is how the Graphics **Library** draws them.

# Closed PolyLine Drawing

The **GE5** microcode provides a special **form** of the line drawing which causes a closed polyline to be drawn. The tokens which **support closed polylines** are shown in Table 4.13. The polylines are drawn as described above but they are enclosed by the two tokens shown. The **GE\_CLOSEDLINE** token sets a flag in the microcode which causes the microcode to **save the new** current graphics position which is set by the first move token. The draw to&ens then cause the polylines to be drawn and after the fast line segment is drawn the GE\_ENDCLOSEDUNE token causes the microcode to draw one last line segment **to the** saved graphics **position of the beginning of the first line segment.**

**Table 4.13 Closed PolyLine Drawing Tokens**

| Token            | Description                 |

|------------------|-----------------------------|

| GE_CLOSEDUNE     | Starts Pdy Line <b>Mode</b> |

| GE_ENDCLOSEDLINE | Ends Poly Line Mode         |

The line segments which form the closed polyline are drawn with the same attributes **as** described above for line segments. The closed polylines are used to draw unfilled geometric objects which are formed by a closed polyline boundary. The closed polyline tokens can be used to draw the following higher level unfilled geometric objects:

- rectangles

- polygons

The next section describes the mechanism for drawing filled geometric objects.

#### Filled Polygon Drawing

The tokens described in this section are provided to draw closed polylines whose interiors are filled with a specified pattern. The objects being drawn are specified as a sequence of vertices which form a vertex list stored in the GE5 data RAM. The tokens shown in Table 4.14 are used to specify the vertices which are stored in the vertex list which can hold a maximum of 256 vertices.

Token Description GE RVERTEX2 Set vertex using floating point relative 2D coordinates GE RVERTEX21 Set vertex using integer relative 2D coordinates **GE\_RVERTEX3** Set vertex using floating point relative 3D coordinates Set vertex using integer relative 3D coordinates GE RVERTEX3I GE\_VERTEX2 Set vertex using floating point absolute 2D coordinates Set vertex using integer absolute 2D coordinates GE\_VERTEX2I Set vertex using floating point absolute 3D coordinates GE\_VERTEX3 Set vertex using integer absolute 3D coordinates GE\_VERTEX3I GE VERTEX4 Set vertex using floating point homogeneous coordinates GE VERTEX4I Set vertex using integer homogeneous coordinates

Table 4.14 Vertex Tokens

The vertices can be specified in either absolute or relative formats. The relative format causes the specified vertice coordinates to be added to the current graphics position to get the new current graphics position. The vertices **are** specified in world coordinates using either floating point or integer coordinates. The vertices can also be specified in **2D**, 3D or homogeneous coordinates.

To draw a filled polygon the tokens shown in Table 4.15 are used to specify the drawing style. Two **styles** of polygon drawing are supported by the microcode. An older style causes an outlined polygon to be drawn while the newer style causes a point sampled polygon to be drawn.