### Video Graphics Array Clock

Preliminary

**DECEMBER 06, 1989**

T-52-33-49

#### **FEATURES**

- Clock generation for IBM\* compatible

Western Digital Video Graphics Array (WD90C00)

- On-chip generation of six video clock frequencies (25.057, 28.189, 36.242, 16.108, 32.216 and 44.744 MHz) derived from 14.318MHz system clock reference frequency

- Pin selectable video clock among the six internally generated clocks and up to three externally supplied clocks.

- Dynamic frequency scaling control using Phase Lock Loops

- Selectable external clock inputs

- On-chip generation of four (36.242, 41.612, 37.586 and 44.744 MHz) memory clock frequencies

- Pin selectable memory clock among the four internally generated clocks

- CMOS technology

- Available in 20 pin PLCC package

#### DESCRIPTION

The Western Digital Video Graphics Array clock generator (WD90C61) is capable of producing different output frequencies dynamically under firmware control. The video output frequency is derived from 14.318 MHz system clock available in IBM† PC†/XT/AT† and Personal System/2†. It is designed to work with the Western Digital Video Graphics Array (WD90C00) for optimizing video subsystem performance.

† IBM, PC, AT, and Personal System/2 are registered trademarks of International Business Machines Corporation.

T-52-33-49

# Video Graphics Array Clock

Preliminary

#### FUNCTIONAL DESCRIPTION:

The WD90C61 device generates the VCLK output according to the select inputs as shown in Table 1. The SEL0 and SEL1 inputs are latched with the SELEN strobe. VGATTL is an additional select input that selects frequencies suitable for VGA modes when left high and frequencies suitable for TTL modes when pulled low. Select input FCLKSEL overrides internal clock generation and passes through the FCLKIN clock input.

The MCLK output is generated according to the select inputs as shown in Table 2. The various VCLK and MCLK frequencies are achieved by multiplying the 14.318 MHz input frequency by a factor of N/32 (e.g., 44.74 is obtained with N = 100).

The VCLKE and MCLKE inputs can tristate the VCLK and MCLK outputs to facilitate board level testing. External filter components are attached to the MCAP and VCAP pins for the internal phase lock loops.

Table 1. VCLK Selection

| <br>VCLKE                                        | FCLKSEL                                                                    | VGATTL                                                | SEL0                  | SEL1             | VCLK Frequency                                                                                     |

|--------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------|-----------------------|------------------|----------------------------------------------------------------------------------------------------|

| <br>Open<br>Open<br>Open<br>Open<br>Open<br>Open | 1 or Open<br>1 or Open<br>1 or Open<br>1 or Open<br>1 or Open<br>1 or Open | 1 or Open<br>1 or Open<br>1 or Open<br>1 or Open<br>0 | 0<br>0<br>1<br>1<br>0 | 0 1 0 1          | 25.057 MHz<br>28.189 MHz<br>EXTCLK pass-through<br>36.242 MHz<br>REFCLK pass-through<br>16.108 MHz |

| Open<br>Open<br>Open<br>0                        | 1 or Open<br>1 or Open<br>0<br>X                                           | 0<br>0<br>X<br>X                                      | 1<br>1<br>X<br>X      | 0<br>1<br>X<br>X | 32.216 MHz<br>44.744 MHz<br>FCLKIN pass-through<br>DISABLED                                        |

Table 2. MCLK Selection

| MCLKE                             | MCLKS0                                | MCLKS1                        | MCLK Frequency                                                   | Application                            |

|-----------------------------------|---------------------------------------|-------------------------------|------------------------------------------------------------------|----------------------------------------|

| Open<br>Open<br>Open<br>Open<br>0 | 1 or Open<br>1 or Open<br>0<br>0<br>X | 1 or Open<br>0<br>1<br>0<br>X | 44.744 MHz<br>37.585 MHz<br>36.242 MHz<br>41.612 MHz<br>DISABLED | WD90C00<br>WD90C10<br>PVGA1A<br>PVGA1A |

#### T-52-33-49

Preliminary

### Video Graphics Array Clock

**DECEMBER 06, 1989**

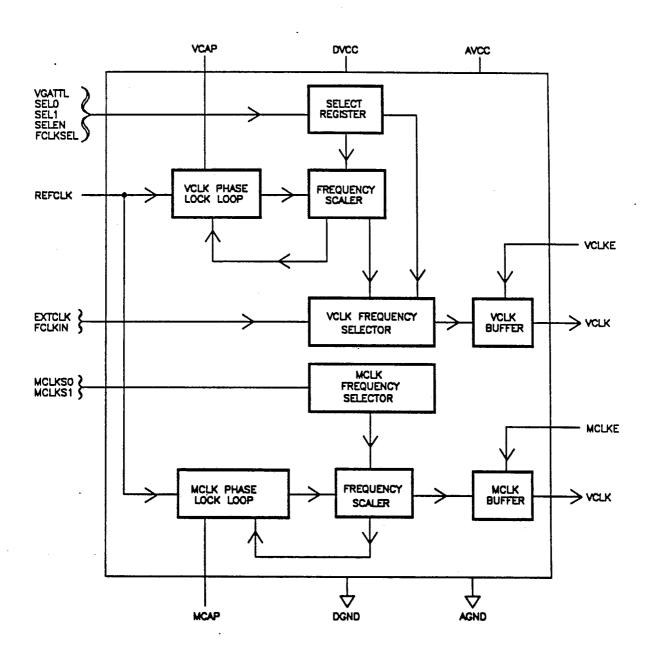

Figure 1. WD90C61 Functional Block Diagram

T-52-33-49

Video Graphics Array Clock

Preliminary

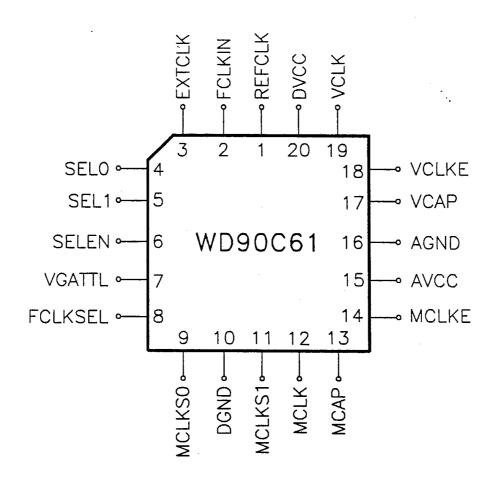

Figure 2. WD90C61 Pin Assignments

# Video Graphics Array Clock

T-52-33-49

Preliminary

**DECEMBER 06, 1989**

Table 3. Pin List and Functions

| REFCLK IN 1 Reference Input Clock from system (14.318MHz)  FCLKIN IN 2 Clock input from Feature Connector EXTCLK IN 3 External Clock input for an additional SEL0 IN 4 Control Input for VCLK selection  SEL1 IN 5 Control Input for VCLK selection  SELEN IN 6 Strobe for latching SEL0 and SEL1  VGATTL IN 7 Select input for VCLK selection - has pullup resistor  FCLKSEL IN 8 Select input for VCLK - has an internation when pulled low, passes through FCl  MCLKS0 IN 9 Select input for MCLK selection - has pullup resistor  MCLKS1 IN 11 Select input for MCLK selection - has pullup resistor  MCLK OUT 12 Memory Clock (MCLK) output  MCAP IN 13 External filter connection for MCLK get  MCLKE IN 14 Enable input for MCLK output - has a pullup resistor. When pulled low, trists  VCAP IN 17 External filter connection for VCLK get                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| EXTCLK IN 3 External Clock input for an additional SEL0 IN 4 Control Input for VCLK selection  SEL1 IN 5 Control Input for VCLK selection  SELEN IN 6 Strobe for latching SEL0 and SEL1  VGATTL IN 7 Select input for VCLK selection - has pullup resistor  FCLKSEL IN 8 Select input for VCLK - has an internation when pulled low, passes through FCl  MCLKS0 IN 9 Select input for MCLK selection - has pullup resistor  MCLKS1 IN 11 Select input for MCLK selection - has pullup resistor  MCLK OUT 12 Memory Clock (MCLK) output  MCAP IN 13 External filter connection for MCLK get  MCLKE IN 14 Enable input for MCLK output - has a pullup resistor. When pulled low, trists  VCAP IN 17 External filter connection for VCLK get                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                         |

| SEL0 IN 4 Control Input for VCLK selection  SEL1 IN 5 Control Input for VCLK selection  SELEN IN 6 Strobe for latching SEL0 and SEL1  VGATTL IN 7 Select input for VCLK selection - has pullup resistor  FCLKSEL IN 8 Select input for VCLK - has an internation when pulled low, passes through FCl  MCLKS0 IN 9 Select input for MCLK selection - has pullup resistor  MCLKS1 IN 11 Select input for MCLK selection - has pullup resistor  MCLK OUT 12 Memory Clock (MCLK) output  MCAP IN 13 External filter connection for MCLK get  MCLKE IN 14 Enable input for MCLK output - has a pullup resistor. When pulled low, trists  VCAP IN 17 External filter connection for VCLK get                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <del></del>             |

| SEL1 IN 5 Control Input for VCLK selection  SELEN IN 6 Strobe for latching SEL0 and SEL1  VGATTL IN 7 Select input for VCLK selection - has pullup resistor  FCLKSEL IN 8 Select input for VCLK - has an internative when pulled low, passes through FCl  MCLKS0 IN 9 Select input for MCLK selection - has pullup resistor  MCLKS1 IN 11 Select input for MCLK selection - has pullup resistor  MCLK OUT 12 Memory Clock (MCLK) output  MCAP IN 13 External filter connection for MCLK get  MCLKE IN 14 Enable input for MCLK output - has a pullup resistor. When pulled low, trists  VCAP IN 17 External filter connection for VCLK get                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | frequency               |

| SELEN IN 6 Strobe for latching SEL0 and SEL1  VGATTL IN 7 Select input for VCLK selection - has pullup resistor  FCLKSEL IN 8 Select input for VCLK - has an internative when pulled low, passes through FCl  MCLKS0 IN 9 Select input for MCLK selection - has pullup resistor  MCLKS1 IN 11 Select input for MCLK selection - has pullup resistor  MCLK OUT 12 Memory Clock (MCLK) output  MCAP IN 13 External filter connection for MCLK get  MCLKE IN 14 Enable input for MCLK output - has a pullup resistor. When pulled low, trists  VCAP IN 17 External filter connection for VCLK get                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <del></del>             |

| VGATTL IN 7 Select input for VCLK selection - has pullup resistor  FCLKSEL IN 8 Select input for VCLK - has an internative when pulled low, passes through FCl MCLKS0 IN 9 Select input for MCLK selection - has pullup resistor  MCLKS1 IN 11 Select input for MCLK selection - has pullup resistor  MCLK OUT 12 Memory Clock (MCLK) output  MCAP IN 13 External filter connection for MCLK get make the pullup resistor. When pulled low, trists over the pullup resistor. When pulled low, trists over the pulled low in the pulled low | <del></del>             |

| FCLKSEL IN 8 Select input for VCLK - has an internation when pulled low, passes through FCl MCLKS0 IN 9 Select input for MCLK selection - has pullup resistor  MCLKS1 IN 11 Select input for MCLK selection - has pullup resistor  MCLK OUT 12 Memory Clock (MCLK) output  MCAP IN 13 External filter connection for MCLK get MCLKE IN 14 Enable input for MCLK output - has a pullup resistor. When pulled low, trists VCAP IN 17 External filter connection for VCLK get MCLKS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <del></del>             |

| MCLKS0 IN 9 Select input for MCLK selection - has pullup resistor  MCLKS1 IN 11 Select input for MCLK selection - has pullup resistor  MCLK OUT 12 Memory Clock (MCLK) output  MCAP IN 13 External filter connection for MCLK get MCLKE IN 14 Enable input for MCLK output - has a pullup resistor. When pulled low, trists VCAP IN 17 External filter connection for VCLK get MCLKE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | an internal             |

| MCLKS1 IN 11 Select input for MCLK selection - has pullup resistor  MCLK OUT 12 Memory Clock (MCLK) output  MCAP IN 13 External filter connection for MCLK get  MCLKE IN 14 Enable input for MCLK output - has a pullup resistor. When pulled low, trists  VCAP IN 17 External filter connection for VCLK get                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | al pullup<br>LKIN       |

| MCLK OUT 12 Memory Clock (MCLK) output  MCAP IN 13 External filter connection for MCLK go  MCLKE IN 14 Enable input for MCLK output - has a pullup resistor. When pulled low, trist:  VCAP IN 17 External filter connection for VCLK go                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | an internal             |

| MCAP IN 13 External filter connection for MCLK government of MCLK government of MCLK output - has a pullup resistor. When pulled low, trists a pullup resistor when pulled low, trists and the management of MCLK government o | an internal             |

| MCLKE IN 14 Enable input for MCLK output - has a pullup resistor. When pulled low, trist:  VCAP IN 17 External filter connection for VCLK get                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <del></del>             |

| vcap IN 17 External filter connection for VCLK ge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | eneration               |

| The state of the s | n internal<br>ates MCLK |

| MOLKE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | neration                |

| VCLKE IN 18 Enable input for VCLK output - has a pullup resistor. When pulled low, trist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | n internal<br>ates VCLK |

| VCLK OUT 19 Video Clock (VCLK) output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <del></del>             |

| DVCC 20 Power supply for digital circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                         |

| DGND 10 Ground for digital circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                         |

| AVCC 15 Power supply for analog circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                         |

| AGND 16 Ground for analog circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                         |

T-52-33-49

### Video Graphics Array Clock

- Preliminary

#### ABSOLUTE MAXIMUM RATINGS

| Ambient temperature under bias                        | $0^{\circ}$ C TO $70^{\circ}$ C |

|-------------------------------------------------------|---------------------------------|

| Storage temperature                                   | -40° C to 125° C                |

| Voltage on all inputs and outputs with respect to VSS | -0.5 to 7 Volts                 |

NOTE: Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

#### STANDARD TEST CONDITIONS

The characteristics below apply for the following standard test conditions, unless otherwise noted. All voltages are referenced to VSS (0V Ground). Positive current flows into the referenced pin.

| Operating temperature range | $0^{\circ}$ to $70^{\circ}$ C |

|-----------------------------|-------------------------------|

| Power supply voltage        | 4.75 to 5.25 Volts            |

#### D.C. CHARACTERISTICS

| SYMBOL     | PARAMETER                                                                          | MIN      | MAX      | UNITS | CONDITIONS        |

|------------|------------------------------------------------------------------------------------|----------|----------|-------|-------------------|

| $V_{I\!L}$ | Input Low Voltage                                                                  | $v_{ss}$ | 0.8      | V     | $V_{CC} = 5V$     |

| $V_{IH}$   | Input High Voltage                                                                 | 2.0      | $V_{CC}$ | V     | $V_{CC} = 5V$     |

| IIH        | Input Leakage Current                                                              |          | 20       | uA    | $V_{IN} = V_{CC}$ |

| $V_{OL}$   | Output Low Voltage                                                                 |          | 0.4      | V     | IOL = 8.0mA       |

| VOH        | Output High Voltage                                                                | 2.4      |          | V     | IOH = 4.0mA       |

| ICC        | Supply Current                                                                     |          | 25       | mA    | $V_{CC} = 5V$     |

| RUP        | Internal Pullup Resistors<br>(FCLKSEL, MCLKS0,<br>MCLKS1, VGATTL,<br>MCLKE, VCLKE) | 25K      | ***      | Ohm   | VCC = 5V          |

| Cin        | Input Pin Capacitance                                                              |          | 8        | pF    | Fc = 1 MHz        |

| Cout       | Output Pin Capacitance                                                             |          | 12       | pF    | Fc = 1 MHz        |

### Video Graphics Array Clock

T-52-33-49

Preliminary

**DECEMBER 06, 1989**

#### **AC CHARACTERISTICS**

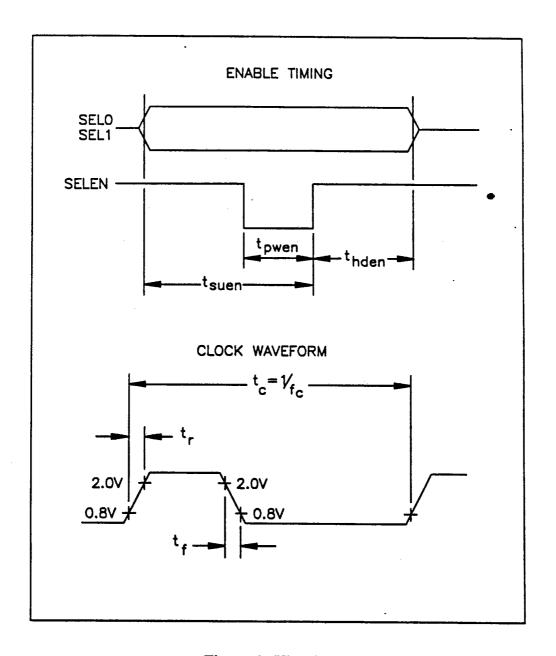

SELEN timing (Top waveform, Figure 3)

| SYMBOL | PARAMETER                 | MIN | MAX | UNITS |

|--------|---------------------------|-----|-----|-------|

| tpwen  | Enable Pulse Width        | 20  |     | ns    |

| tsuen  | Setup Time Data to Enable | 20  | *** | ns    |

| thden  | Hold Time Data to Enable  | 10  |     | ns    |

| Reference Input Clock (See Figure 3) |              | REFCLK = 14.318MHz |      |       |  |

|--------------------------------------|--------------|--------------------|------|-------|--|

| SYMBOL                               | PARAMETER    | MIN                | MAX  | UNITS |  |

|                                      | Duty Cycle   | 42.5               | 57.5 | %     |  |

| tr                                   | Rise Time    | ***                | 10   | ns    |  |

| tf                                   | Fall Time    | •••                | 10   | ns    |  |

|                                      | Phase Jitter |                    | 1    | ns*   |  |

#### MCLK & VCLK Waveforms (See Figure 3)

| SYMBOL | <b>PARAMETER</b> | MIN | MAX | UNITS |  |

|--------|------------------|-----|-----|-------|--|

|        | Duty cycle       | 40  | 60  | %     |  |

| tr     | Rise time        |     | 3   | ns    |  |

| tf     | Fall time        |     | 3   | ns    |  |

|        | Phase Jitter     |     | 5   | ns*   |  |

NOTE: Parameteric Test And Measurement Data is based upon the following details;

- \* 1 Maximum jitter within a range of 30 us after triggering on a 400 MHz scope.

- 2 Output pin loading = 25pf.

- 3 Rise and fall time between 0.8 and 2.0 VDC.

T-52-33-49

Video Graphics Array Clock

Preliminary

Figure 3. Waveforms

T-52-33-49

Preliminary

### Video Graphics Array Clock

**DECEMBER 06, 1989**

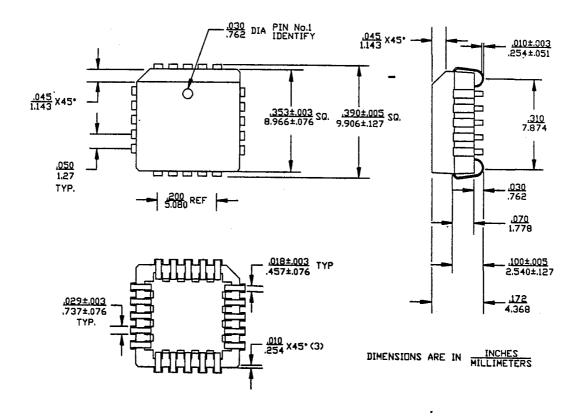

#### SALES ORDER INFORMATION:

**PACKAGE**

WESTERN DIGITAL

**TYPE**

**PART NUMBER**

20-PIN PLCC

WD90C61JE00

Figure 4. Packaging

#### T-52-33-49

#### Video Graphics Array Clock

Preliminary

#### APPLICATION DESCRIPTION

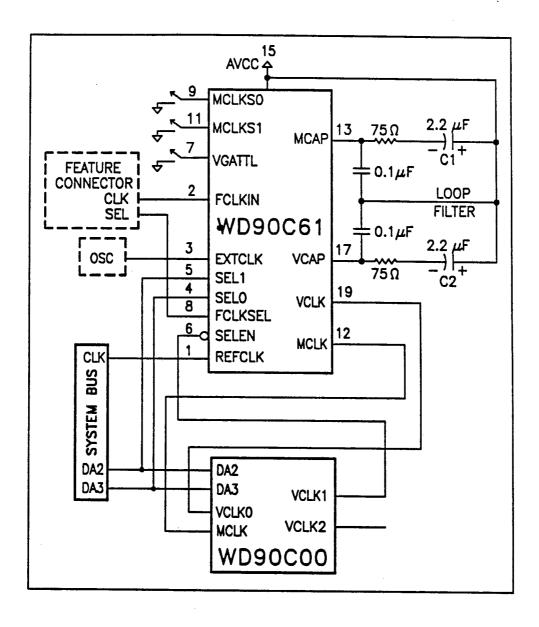

The typical application block diagram (refer to Figure 4) shows the Western Digital Video Graphics Array Clock (WD90C61) and the Western Digital Video Graphics Array (WD90C00), with external oscillators connected to a system bus.

The system bus provides a reference frequency to the WD90C61, which can dynamically select different video clock frequencies (VCLK) based upon the state of the mode control bits. The Western Digital Video Graphics Array (WD90C00) is normally designed with VCLK1 as an input pin. The configuration register bit 3 can be programmed to make it an output and provide the mode control latch enable (SELEN) pulse. This pulse can be used to select the desired VCLK frequency or external input frequency EXTCLK or REFCLK based on the state of the select pins. The FCLKIN and FCLKSEL pins can be connected to the clock and select pins from the Feature Connector.

MCLK frequencies can be selected by strapping the MCLKS0 and MCLKS1 inputs according to Table 2 of this data sheet.

The VGATTL input of the WD90C61 can be left open or strapped to ground to select the VCLK frequencies suitable for VGA or TTL modes.

The WD90C00's pin 73 (VCLK2) can be programmed to be configured as an output. This output can be controlled by software and so can be used as a frequency select input by the WD90C61. Please refer to the WD90C00 datasheet for more information.

# T-52-33-49 Preliminary

### Video Graphics Array Clock

**DECEMBER 06, 1989**

Figure 5. Typical Application

#### NOTES:

- 1 C1 and C2 are 2.2 uF, 25V, tant. capacitors.

- 2 0.1 uF capacitors are ceramic capacitors.

- 3 75-Ohm resistors are 1% metal film resistors.

- 4 WD90C00 is Western Digital Advanced Video Graphics Array