# DP802512 TROPIC™ Upper Memory Decoder

### **General Description**

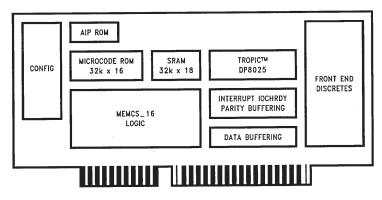

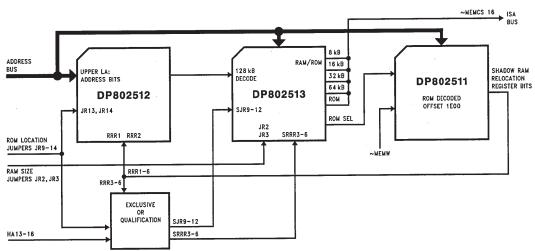

The DP802511, DP802512 and DP802513 form the majority of the MEMCS\_16 circuitry that is responsible for notifying the ISA bus (by way of MEMCS\_16) that it can execute 16-bit bus transfers with the DP8025 TROPIC.

The areas of the architecture that will benefit most from the increased performance of 16-bit transfers are the shared memory interface and the host boot ROM (if so designed). For the boot ROM it is a relatively simple matter of matching the jumpered configuration bits SD9–SD15 (BIOS/MMIO base address) with the system address (SA) lines. The MEMCS\_16 signal's maximum propagation delay from the SA lines is about 25 ns (assuming 8 MHz IBM® PC-AT®).

The shared memory interface RAM size is determined by jumper bits SD2 and SD3. These indicate the block size decoded to the shared memory MEMCS\_16 circuitry. The

address of this shared memory interface is software selectable. In order for the hardware to respond to the proper memory address it must shadow the RAM Relocation Register of the TROPIC's memory mapped I/O space. The data programmed into the RAM Relocation Register is latched into this shadowing register and used in conjuction with the system address lines to determine which address range contains the shared memory interface.

#### **Features**

- Single chip custom logic solution

- Replaces glue logic

- Built-in noise filter

- t<sub>PD</sub> = 15 ns (max)

# **Logic Diagram**

# (15) RRR1 (14) RRR2 (4) LA17 (11) LA23 (9) LA22 (8) LA21 (7) LA20 (6) LA19 (1) JR14 (2) JR13 (018) T<sub>RESET</sub> (019) N<sub>RESET</sub>

# **Block Diagram**

TL/L/11445-1

The DP802512 TROPIC Upper Memory Decoder is manufactured using National's high performance 1.2  $\mu m$  CMOS process and generates two 128k block decode output signals. RAM\_DCD provides a 128k block decode of a user programmable base in the lower 1 Megabyte of system address space, excluding addresses E000 and F000.

ROS\_DCD provides a 128k block decode of a user jumper selected base for the system boot ROM in the lower 1 Megabyte of system memory.

The device also contains a noise and glitch filter. Treset is a qualified version of the system reset signal, which ensures that any noise or glitches will be factored out.

FIGURE 1. TROPIC 16-Bit ISA Token Ring Workstation Adapter

FIGURE 2. MEMCS\_Logic

TL/L/11445-4

TL/L/11445-3

1

## Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage (V<sub>CC</sub>)

-0.5V to +7.0V

Input Voltage

-2.5V to  $V_{CC} + 1.0V$

Off-State Output Voltage Output Current

-2.5V to  $V_{CC} + 1.0$ V

± 100 mA

Power Applied Junction Temperature

Storage Temperature

Ambient Temperature with

-65°C to +125°C

-65°C to +150°C

-65°C to +150°C

Lead Temperature

(Soldering, 10 seconds)

260°C

# **Recommended Operating Conditions**

SUPPLY VOLTAGE AND TEMPERATURE

| Symbol         | Parameter                      |      |     |      |       |

|----------------|--------------------------------|------|-----|------|-------|

|                | i didiletei                    | Min  | Nom | Max  | Units |

| Vcc            | Supply Voltage                 | 4.75 | 5   | 5.25 | V     |

| T <sub>A</sub> | Operating Free-Air Temperature | 0    | 25  | 75   | °C    |

# Electrical Characteristics Over Recommended Operating Conditions

| Symbol          | Parameter                              | Conditions                                                       |                          | Temperature<br>Range | Min  | Тур | Max                 | Units |

|-----------------|----------------------------------------|------------------------------------------------------------------|--------------------------|----------------------|------|-----|---------------------|-------|

| V <sub>IH</sub> | High Level Input Voltage               |                                                                  |                          |                      | 2.0  |     | V <sub>CC</sub> + 1 | ٧     |

| V <sub>IL</sub> | Low Level Input Voltage                |                                                                  |                          |                      | -0.5 |     | 0.8                 | V     |

| V <sub>OH</sub> | High Level Output Voltage              | V <sub>CC</sub> = Min                                            | I <sub>OL</sub> = 3.2 mA | СОМ                  | 2.4  |     |                     | V     |

| V <sub>OL</sub> | Low Level Output Voltage               | V <sub>CC</sub> = Min                                            | I <sub>OL</sub> = 24 mA  | СОМ                  |      |     | 0.5                 | V     |

| lozh            | High Level Off State<br>Output Current | V <sub>CC</sub> = Max,<br>V <sub>O</sub> = V <sub>CC</sub> (Max) |                          |                      |      |     | 10                  | μА    |

| lozL            | Low Level Off State Output Current     | V <sub>CC</sub> = Max, V <sub>O</sub> = GND                      |                          |                      |      |     | -10                 | μА    |

| lį              | Maximum Input Current                  | $V_{CC} = Max, V_I = V_{CC} (Max)$                               |                          |                      |      |     | 10                  | μА    |

| l <sub>IH</sub> | High Level Input Current               | V <sub>CC</sub> = Max, V <sub>I</sub> = V <sub>CC</sub> (Max)    |                          |                      |      |     | 10                  | μА    |

| I <sub>IL</sub> | Low Level Input Current                | $V_{CC} = 5.0V, V_O = GND$                                       |                          |                      |      |     | -10                 | μА    |

| los*            | Output Short Circuit Current           | $V_{CC} = 5.0V, V_O = GND$                                       |                          | СОМ                  | -30  |     | -150                | mA    |

| Icc             | Supply Current                         | V <sub>CC</sub> = Max                                            |                          |                      |      |     | 90                  | mA    |

| CI              | Input Capacitance                      | $V_{CC} = 5.0V,$                                                 | V <sub>I</sub> = 2.0V    |                      |      |     | 8                   | pF    |

<sup>\*</sup>One output at a time for a maximum duration of one second.

Note 1: Absolute maximum ratings are those values beyond which the device may be permanently damaged. Proper operation is not guaranteed outside the specified recommended operating conditions.

# А

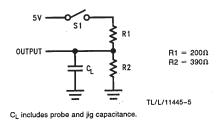

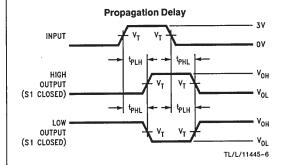

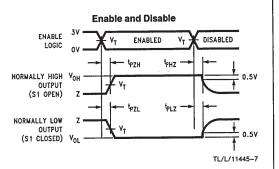

#### DP802512 Conditions Commercial Symbol **Parameter** Min Max Units S1 Closed, $C_L = 50 \, pF$ 15 ns Input to Output $t_{PD}$ Input to Output Enabled via Active High: S1 Open, C<sub>L</sub> = 50 pF t<sub>PZXI</sub> 15 ns Active Low: S1 Closed, $C_L = 50 \text{ pF}$ Control Logic Active High: S1 Open, $C_L = 5 pF$ Input to Output Disabled via tpxzi 15 ns Active Low: S1 Closed, C<sub>L</sub> = 5 pF Control Logic

Switching Characteristics Over Recommended Operating Conditions

### **AC Test Load**

### **Test Waveforms**

TL/L/11445-8

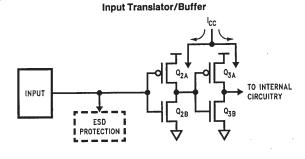

## **Input Schematic**