# Am7984A

# **FDDI ENcoder DECoder (ENDEC)**

# Advanced Micro Devices

## DISTINCTIVE CHARACTERISTICS

- Implements 4B/5B encoding/decoding as specified by the ANSI X3T9.5 Fiber Distributed Data Interface (FDDI) standard

- 100 Mbps, 125 MBaud serial data-rate

- Byte-clock and nibble-clock output

- Selectable loopback and repeat modes

- Elasticity Buffer

- Smoother

- Repeat filter

- Single +5-V supply

# **GENERAL DESCRIPTION**

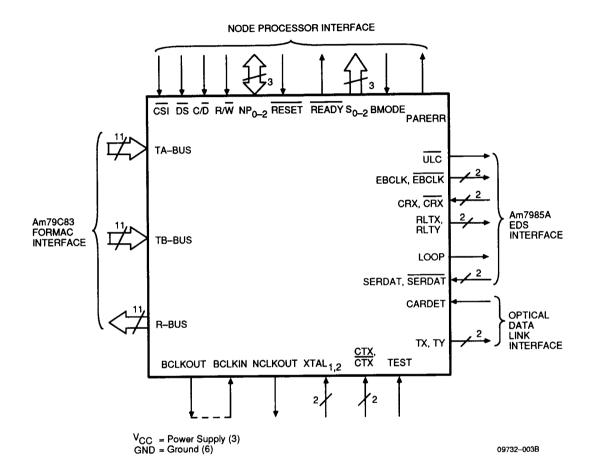

The Am7984A ENDEC (ENcoder DECoder) performs 4B/5B encoding on data to be transmitted from an FDDI station. The chip also performs 4B/5B decoding of received data. It has an elasticity buffer which allows a station to compensate for small differences between receive and transmit clock frequencies. There is a smoother present in the receive path to ensure with a very high probability that a minimum of 6 bytes of IDLE are received before a frame. It also decodes line state information from data that has been received from the network media, and enables line states to be forced onto

the media for connection management purposes. A repeat filter replaces any invalid symbols with other symbols that are determined by the repeat filter state machine. The ENDEC interfaces to the FORMAC through two 11-bit transmit buses and one 11-bit receive bus. Data is serially transferred to an optical transmitter by a differential driver. The ENDEC interfaces to the Node Processor (NP) through a 3-bit bus and associated handshake lines. It also supplies the master clock for the network interface of the station.

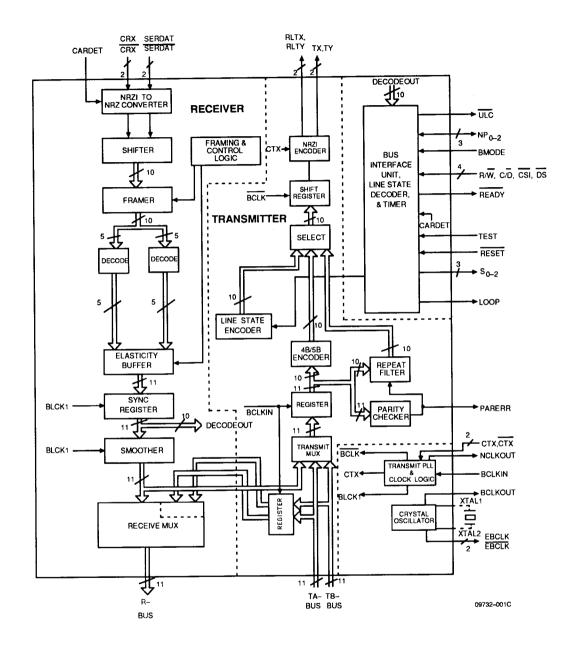

# **BLOCK DIAGRAM**

Am7984A

# NOTE

The word "frame" is used in the SUPERNET data sheets to describe two different groups of information.

1) One group is passed over the network media and is structured as follows:

| Frame    | Start     | Frame   | Destination | Source  |             | Frame          | End       | Frame  |

|----------|-----------|---------|-------------|---------|-------------|----------------|-----------|--------|

| Preamble | Delimiter | Control | Address     | Address | Information | Check Sequence | Delimiter | Status |

2) The others are stored in buffer memory and structured as follows:

| A \ | Tron | amit | frame |

|-----|------|------|-------|

|     |      |      |       |

|   | , ,        |         |             |         |             |                |         |

|---|------------|---------|-------------|---------|-------------|----------------|---------|

| ı |            | Frame   | Destination | Source  |             | Frame          |         |

| ŀ | Descriptor | Control | Address     | Address | Information | Check Sequence | Pointer |

B) Receive frame

|            | Frame   | Destination | Source  |             | Frame          |

|------------|---------|-------------|---------|-------------|----------------|

| Descriptor | Control | Address     | Address | Information | Check Sequence |

# **TABLE OF CONTENTS**

| DISTINCTIVE CHARACTERISTICS                       | 1        |

|---------------------------------------------------|----------|

| GENERAL DESCRIPTION                               | 1        |

| BLOCK DIAGRAM                                     | 2        |

| CONTENTS                                          | 4        |

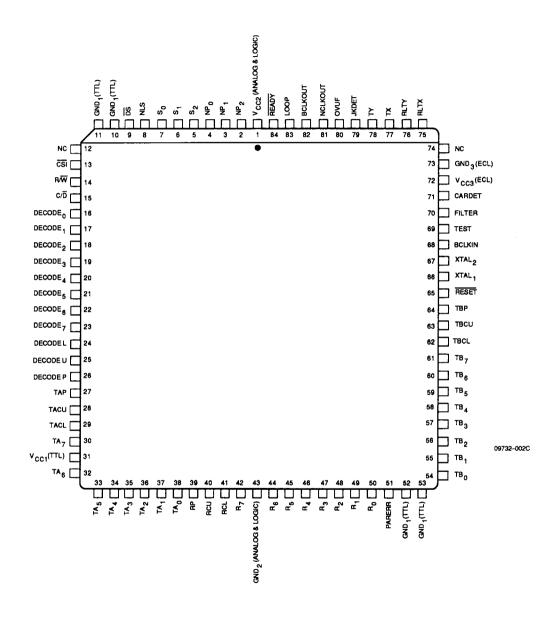

| CONNECTION DIAGRAM (Top View)                     | 5        |

| LOGIC SYMBOL                                      | 6        |

| ORDERING INFORMATION                              | 7        |

| Standard Products                                 | 7        |

| PIN DESCRIPTION                                   | 8        |

| Parallel Buses                                    | 8        |

| Node Processor (NP) Interface                     | 9        |

| EDS Interface                                     | 9        |

| Clock Signals                                     | 10<br>10 |

| Optical Data Link Interface                       |          |

| Test Signals                                      | 10       |

| Power Supply                                      | 11       |

| FUNCTIONAL DESCRIPTION                            | 12<br>12 |

| User-Accessible Resources                         | 12       |

| Programmable Resources                            | 12       |

| Hardwired Resources                               |          |

| Block Diagram Description                         | 12<br>12 |

| Transmitter                                       | 15       |

| Line State Decoder, Timer, and Bus Interface Unit | 15       |

| Receiver                                          | 15       |

| Decoder                                           | 15       |

| Framing and Control Logic                         | 16       |

| Elasticity Buffer                                 | 16       |

| Sync. Register                                    | 16       |

| Smoother                                          | 16       |

| Receive Mux                                       | 16       |

| Crystal Oscillator                                | 16       |

| Transmit PLL and Clock Logic                      | 17       |

| Operational Modes                                 | 17       |

| User-Accessible Registers                         | 17       |

| Diagnostic Features                               | 22       |

| ABSOLUTE MAXIMUM RATINGS                          | 22       |

| OPERATING RANGES                                  | 23       |

| DC CHARACTERISTICS                                | 25<br>25 |

| SWITCHING CHARACTERISTICS                         | 25<br>28 |

| SWITCHING WAVEFORMS                               | 26<br>35 |

| SWITCHING TEST CIRCUITS                           | 36       |

| SWITCHING TEST WAVEFORMS                          | 37       |

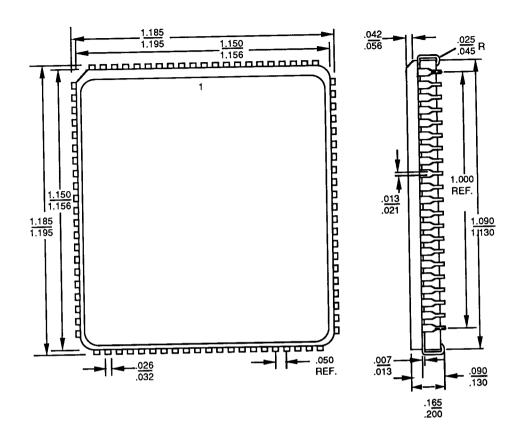

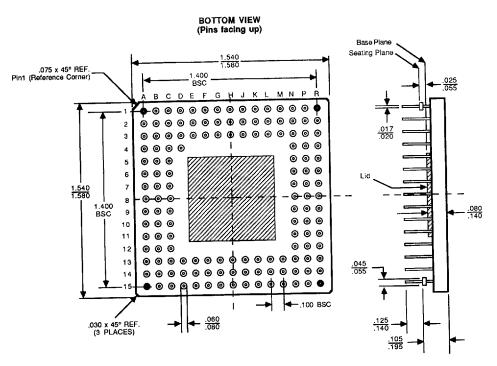

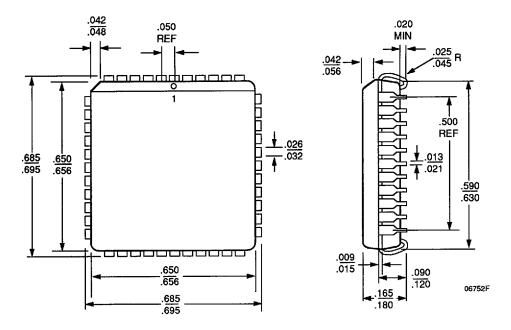

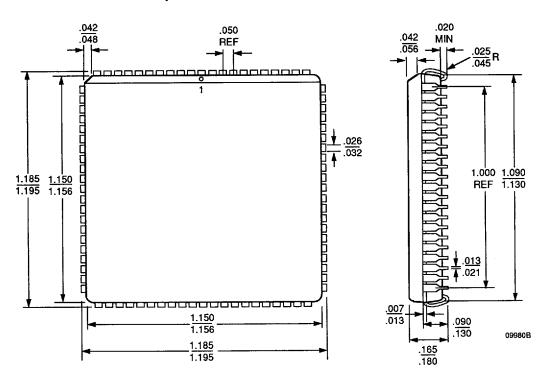

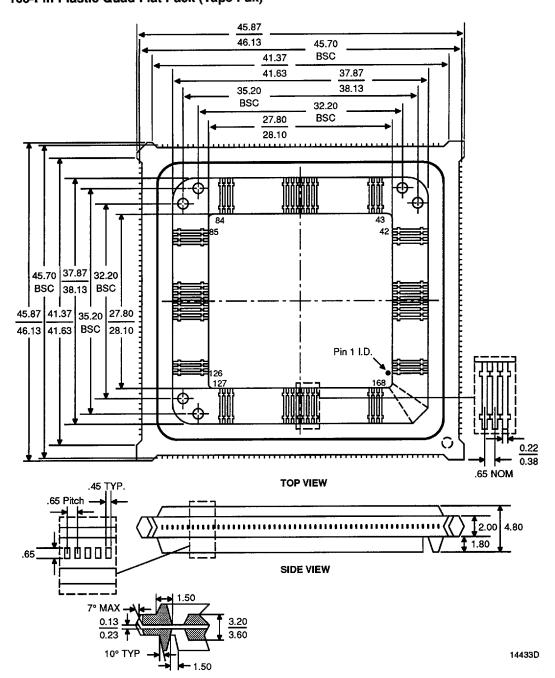

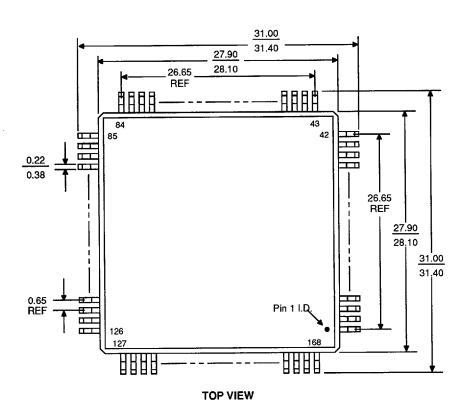

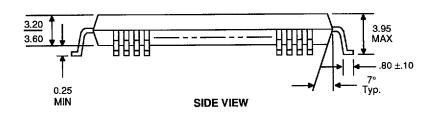

| PHYSICAL DIMENSIONS                               | 3/       |

5–4 Am7984A

Am7984A

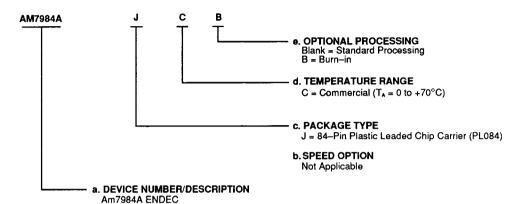

# ORDERING INFORMATION Standard Products

AMD standard products are available in several packages and operating ranges. The ordering number (Valid Combination) is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Package Type d. Temperature Range

- e. Optional Processing

| Valid Combinations |         |

|--------------------|---------|

| AM7984A            | JC, JCB |

### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

#### PIN DESCRIPTION

#### Parallel Buses

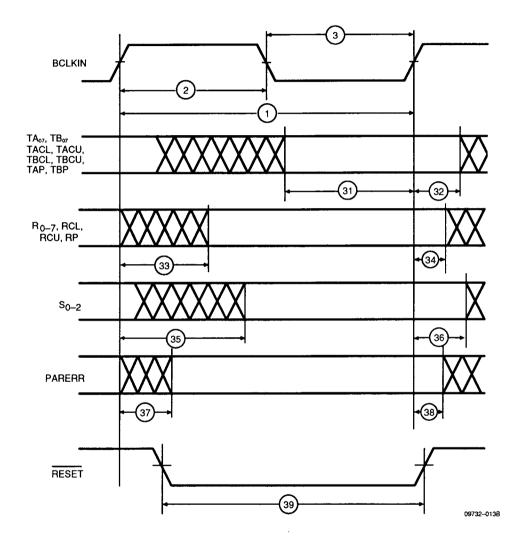

This section describes the pins used to interface the Am7984A ENDEC with a FORMAC or another ENDEC. All of the signals are synchronous with BCLKIN. There are two transmit buses and one receive bus. The higher order nibble is transmitted first.

#### R0-7

#### Receive Bus (TTL Outputs)

The R-bus output sends information being decoded from the serial receive input of the ENDEC to either the FORMAC or the transmit bus of another ENDEC in the station.

#### RCL

# Receive Control Lower (TTL Output; Active HIGH)

The RCL signal is used to identify the type of information being presented on the lower nibble (Ro-3) of the ENDEC receive bus output. If RCL is HIGH, then the lower nibble is a network control character; if LOW, the lower nibble is data.

#### **RCU**

# Receive Control Upper (TTL Output; Active HIGH)

The RCU signal is used to identify the type of information being presented on the upper nibble (R4-7) of the ENDEC receive bus output. If RCU is HIGH, then the upper nibble is a network control character; if LOW, the upper nibble is data.

## RP

# Receive Bus Parity (TTL Output; Active HIGH)

The RP signal ensures odd parity on RCU, RCL, and lines  $R_{0.7}$  of the ENDEC receive bus. If the number of "1s" on these pins is odd, then RP will be logic "0".

#### $TA_{0-7}$

### Transmit Bus A (TTL Inputs)

This is one of two input buses used to accept transmit data and control information from either the FORMAC or the other ENDEC (if one exists) at the station.

#### TACL

# "Transmit Bus A" Control Lower (TTL Input; Active HIGH)

The TACL signal is used to identify the type of information being presented on the lower nibble (TAo.3) of trans-

mit bus A. When TACL is HIGH, the lower nibble is interpreted as a network control character; otherwise, it is interpreted as data.

#### TACU

# "Transmit Bus A" Control Upper (TTL Input; Active HIGH)

The TACU pin is similar in function to TACL except that it identifies the type of information being presented on the upper nibble (TA<sub>4-7</sub>) of transmit bus A.

#### TAP

# "Transmit Bus A" Parity (TTL Input; Active HIGH)

The TAP signal ensures odd parity of signals TAo-7, TACL, and TACU. If the number of logic "1s" on these pins is odd, then TAP will be logic "0". Data with a parity error will be processed by the repeat filter state machine inside the ENDEC.

#### TB<sub>0-7</sub>

#### "Transmit Bus B" (TTL Inputs)

This is one of two input buses used to accept transmit data and control characters from the FORMAC or the other ENDEC (if one exists) in the station.

#### **TBCL**

# "Transmit Bus B" Control Lower (TTL Input; Active HIGH)

TBCL is similar in function as TACL except that it identifies the type of information being presented on the lower nibble of transmit bus B. If TBCL is HIGH, the nibble TB<sub>03</sub> is a control character.

#### **TBCU**

# "Transmit Bus B" Control Upper (TTL Input; Active HIGH)

The TBCU signal provides an identical function as TBCL for the upper nibble of transmit bus B. If TBCU is HIGH, then the nibble TB<sub>4.7</sub> is a control character.

# **TBP**

#### "Transmit Bus B" Parity (TTL Input; Active HIGH)

The TBP signal ensures odd parity of signals TBo-7, TBCL, and TBCU (see pin TAP). If the number of logic "1s" on these pins is odd, then TBP will be logic "0". Data with a parity error will be processed by the repeat filter inside the Am7984A.

#### EDS Interface

The following section describes the pins which connect to Am7985A EDS.

# CRX. CRX

#### Clock Receive+, Clock Receive-(Differential CML/ECL input)

The bit rate clock derived from the received serial data (RX, RY or RLTX, RLTY) is sent to the ENDEC from the receive PLL in the EDS using CRX, CRX.

# EBCLK, EBCLK

# ECL Byteclock+, ECL Byteclock- (Differential Pseudo ECL Output)

The crystal oscillator on the ENDEC generates the byte rate (12.5 MHz) frequency reference for use by the EDS. This signal is synchronous to BCLKOUT.

#### LOOP

#### (Pseudo-ECL Output; Active HIGH)

The LOOP signal is active when the ENDEC is in loopback mode. When the LOOP pin is active, it causes the RLTX, RLTY outputs of the ENDEC to be looped back through the RLTX, RLTY inputs of the EDS.

## **RLTX. RLTY**

## Receive Loop Transmit+, Receive Loop Transmit-(Differential Pseudo-ECL Outputs)

RLTX, RLTY are an alternate set of serial outputs from the ENDEC, used to loop back through the EDS. They contain the same data as TX, TY except when the ENDEC is in loopback mode.

# SERDAT, SERDAT

# Serial Data+, Serial Data- (Differential CML/ECL Input)

SERDAT, SERDAT are NRZI data coming from the EDS. They are synchronized with the rising edge of CRX.

#### **ULC**

# Use Local Clock (Single Ended Pseudo ECL Output; Active LOW)

The ULC signal is active whenever CARDET goes inactive, or when in Quiet Line State (QLS). ULC is also controlled by the noise timer inside the ENDEC. The noise timer forces ULC to be active for a period of 128 BCLK cycles (10.24 µsec @ 100 Mbps) after NLS has been active for at least one byteclock. After 128 BCLK cycles, the noise timer releases ULC for the next 128 BCLK cycles. After the end of this second 128 BCLK cycle interval, if NLS is still active, then the noise timer becomes active again, forcing ULC active.

# Node Processor (NP) Interface

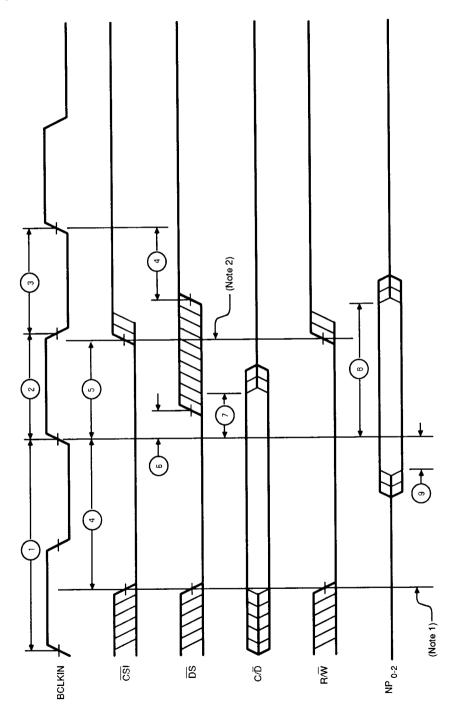

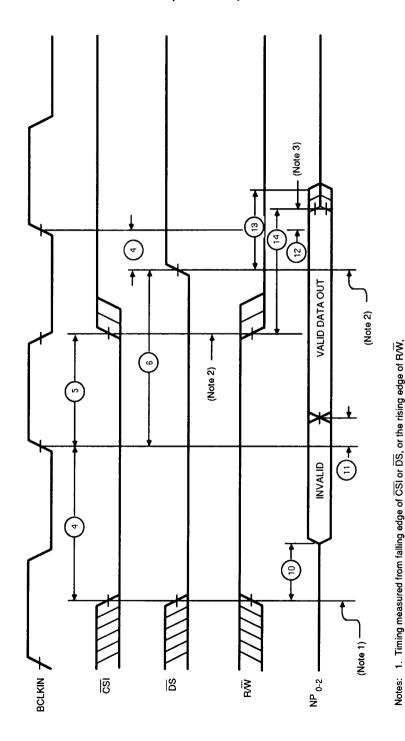

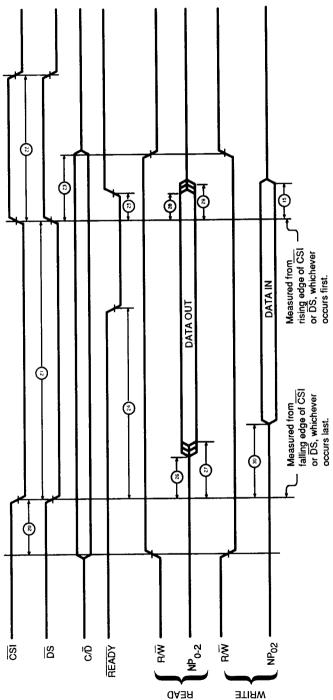

# C/D

# Command/Data (TTL Input)

When  $C/\overline{D}$  is HIGH, the data on the NP<sub>0-2</sub> (NP<sub>0-2</sub>) is written into the 3-bit pointer register in the ENDEC. When  $C/\overline{D}$  is LOW, data on NP<sub>0-2</sub> is written into one of the control registers or read from one of the control/ status registers inside the ENDEC, as pointed to by the pointer register.

#### CSI

## Chip Select (TTL Input; Active LOW)

CSI, when LOW, indicates that the NP has selected the ENDEC to write into the control registers inside the ENDEC or to read either the control registers or the line state status register. It should stay LOW until the READY signal from the ENDEC goes LOW (in asynchronous mode).

# DS

# Data Strobe (TTL Input; Active LOW)

The  $\overline{DS}$  is used for defining the presence of data on the NP<sub>0-2</sub>.  $\overline{DS}$  is LOW whenever the data to be written is valid in the case of write operation, or when the NP is ready to read in the case of a read operation. It should stay LOW until the  $\overline{READY}$  signal from the ENDEC goes active (LOW).

#### NP<sub>0-2</sub>

# Node Processor Bus (TTL Input/Output; Three State)

Data from the NPo2 is written into the control register of the ENDEC when  $\overline{CSI}$ ,  $\overline{DS}$ , and R/W are all LOW. The contents of any of the control registers or of the line state status register inside the ENDEC may be read onto the NPo2 when  $\overline{CSI}$  and  $\overline{DS}$  are LOW and R/W is HIGH. The NP operates synchronously with the ENDEC when the BMODE pin is HIGH, or operates asynchronously if the BMODE pin is LOW. The NPo2 is three-stated whenever either  $\overline{CSI}$  or  $\overline{DS}$  is HIGH.

### **PARERR**

#### Parity Error (TTL Output; Active HIGH)

PARERR indicates that there is a parity error on data which is coming in from the selected transmit bus.

#### READY

# READY (TTL Output; Open Collector, Active LOW)

The READY signal is a handshake signal for use with an asynchronous NP. When the BMODE pin is HIGH, as in the case of a synchronous NP. READY is also HIGH and

is typically not used in the system. When BMODE is LOW, the NP runs asynchronous to BCLKIN and the ENDEC indicates that data is being acted upon by bringing READY LOW. During a write operation, READY goes LOW after data from the NP is clocked into the ENDEC. In the case of a read operation, READY goes LOW after the ENDEC supplies valid data on the NPo2. Typically, the ENDEC takes between two and three BCLKIN cycles to force READY LOW after NP asserts DS. READY stays LOW as long as DS and CSI stay LOW.

# RESET

# Reset (TTL Input; Active LOW)

This is a hardware reset that initializes the internal logic in the ENDEC. Reset can be activated asynchronously with BCLKIN but must be held LOW for at least three BCLKIN cycles.

## R/W

# Read/Write (TTL Input)

When  $R/\overline{W}$  is HIGH, the NP reads data from one of the control/status registers. When  $R/\overline{W}$  is LOW, the NP writes data into one of the control registers or the pointer register.

#### S<sub>0-2</sub>

#### Line Status (TTL Outputs)

These signals indicate the line states of the medium as seen at the Ro-7, RCL, RCU, and RP outputs of the ENDEC. The meaning of the status lines is detailed in Table 2.

### **BMODE**

## **Bus Mode (TTL Input)**

The BMODE pin is strapped HIGH for synchronous operation of the NP<sub>0-2</sub> or LOW for asynchronous operation of the NP<sub>0-2</sub>.

# Clock Signals

#### **BCLKIN**

# Byte Clock (TTL Input)

BCLKIN is the main clock that runs the ENDEC. It must be driven from a TTL clock source such as the chip's own BCLKOUT pin or from that of another nearby ENDEC. The transmit PLL uses BCLKIN as a reference to generate the transmit bit clock. The transmit bit clock is ten times the frequency of BCLKIN.

## **BCLKOUT**

#### Byte Clock (TTL Output)

BCLKOUT is derived from an internal oscillator which uses an external crystal operating in its fundamental mode of operation. It is the main clock running the station. All SUPERNET devices use this clock. When there

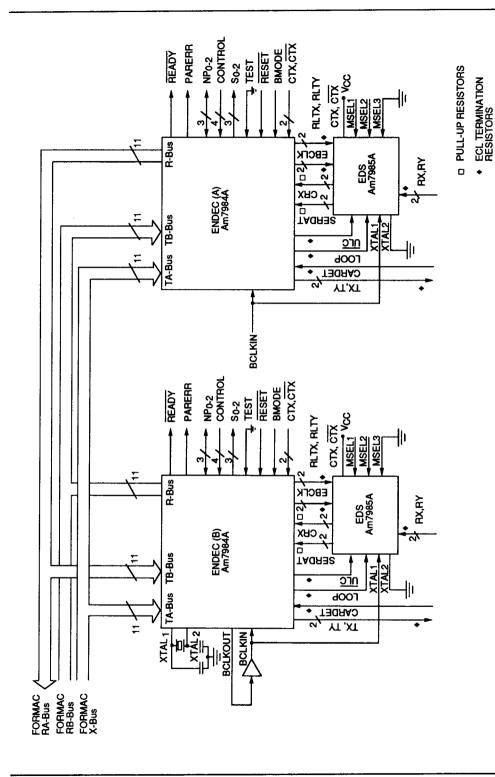

are two ENDECs in a station, as in a dual attachment station (DAS), only one clock source is used; BCLKIN of all ENDECs in the station must be driven from the same clock source.

#### NCLKOUT

#### Nibble Clock (TTL Output)

NCLKOUT is derived from the internal PLL and is twice the frequency of BCLKIN and synchronous to BCLKIN.

## XTAL<sub>1</sub>, XTAL<sub>2</sub>

#### Crystal 1, Crystal 2 (Inputs)

These two crystal inputs connect to an oscillator which operates at the fundamental frequency of a parallel resonant crystal. During normal operation, the byte rate is set by the crystal frequency. If these pins are not used, ground XTAL1. If an external TTL clock source is used to drive XTAL1, then XTAL2 should be grounded.

# Optical Data Link Interface

#### CARDET

# Carrier Detect (Pseudo-ECL Input; Active HIGH)

The CARDET signal is received from the optical receiver. When HIGH, it indicates the presence of data in the fiber. When LOW, this signal is used to force a quiet line state (QLS) in the line state status register and quiet into the decoder. CARDET is ignored in loopback mode.

# TX, TY

# Transmit+, Transmit- (Differential Pseudo-ECL Outputs)

These output pins provide a differential ECL NRZI output from the ENDEC. These ECL signals drive the optical transmitter input. They are referenced to +5 volts and are capable of driving lines which are terminated with 50 ohms resistance connected to Vcc - 2 volts.

# Test Signals

#### **TEST**

## Test (Input; Active HIGH)

When the TEST pin is connected to Vcc, the internal PLL is disabled and instead an external bit clock is input through the CTX,  $\overline{CTX}$  pins. When in TEST mode, we recommend that an external clock source provide BCLKIN. The TEST pin must be grounded for normal operation.

# CTX CTX

# Clock Test+, Clock Test- (Differential Pseudo-ECL Inputs)

CTX,  $\overline{\text{CTX}}$  are used during outgoing inspection, when the TEST pin is tied to Vcc. They are used to supply the bit clock to the ENDEC.

# Power Supply GND<sub>1</sub>, GND<sub>2</sub>, GND<sub>3</sub> Ground Pins

GND $_1$  is the TTL ground, GND $_2$  is the logic and analog ground, and GND $_3$  is the ECL ground.

# V<sub>CC1</sub>, V<sub>CC2</sub>, V<sub>CC3</sub> Power Supply

These are +5.0-volt nominal power supply pins. Vcc1 powers TTL, Vcc2 powers logic and analog, and Vcc3 powers ECL circuitry.

Am7984A 5–11

# **FUNCTIONAL DESCRIPTION**

# **User-Accessible Resources**

# **Programmable Resources**

The ENDEC can be programmed for various modes of operation by the NP using NP data and control status lines. There are four control registers and one status register, each 3 bits wide, inside the ENDEC. Data is written into the control register and read from control/ status registers using the NPo2. The NP interface is used to configure the ENDEC in the following ways:

- A string of quiet symbols, halt symbols, master line states (halt- quiet symbol pairs), idle-quiet symbol pairs, idle symbols, or a JK pair followed by idle symbols may be forced onto the network by the ENDEC by setting the appropriate bits in the control register CRo (see Table 3-2);

- The repeat filter state machine may be enabled by programming control register CR<sub>0</sub> (see Table 3-2).

It is disabled by resetting the ENDEC;

- Either the TA- or TB-bus may be selected for transmission onto the network by programming register CR1;

- Repeat, short loopback, or through mode for the ENDEC, or loopback for the ENDEC/EDS combination may be selected by programming register CR<sub>1</sub>;

- By programming the PARCON bit in register CR<sub>2</sub>, parity error may be converted into halt followed by idle symbols by the repeat filter state machine;

- The ENDEC can be reset using control register CR<sub>2</sub>;

- Information stored in control and status registers may be read;

- Even/Odd parity mode of operation can be chosen by using control register CR2.

- Smoother can be reset through use of control register CR<sub>3</sub> and smoother extension status can be read through control register CR<sub>3</sub>.

#### **Hardwired Resources**

The following are the hardwired resources in the ENDEC:

- 1) The TEST pin;

- The presence of various line states in the decoded data stream is indicated by the ENDEC on pins So<sub>2</sub>;

- The RESET pin operates asynchronously and resets the internal logic of the ENDEC;

- The CARDET pin may be used to force a quiet line state (QLS); (logic "1"s will also be forced onto the R-bus.)

- The PARERR pin indicates the occurrence of parity errors in data to be sent out from the transmit bus;

- The nibble clock is brought out on pin NCLKOUT for possible use by the system;

- 7) The main clock for the station, running at the byte rate, may be generated by the crystal oscillator inside the ENDEC and is available for other chips in the station on the BCLKOUT pin. The BCLKIN pin accepts this byte-rate clock, distributes it to the internal logic associated with data transmission, and uses it to generate a bit-rate clock,

- The ULC pin is used to disable the input data going to the EDS and change the frequency reference for the receive PLL inside the EDS to the transmit byte clock (EBCLK or XTAL1);

- The BMODE pin can be used to select the asynchronous or synchronous mode of operation for the NP bus.

# **Block Diagram Description**

#### **Transmitter**

The transmitter section is divided into eight sub-blocks: transmit mux, register, 4B/5B encoder, select, shift register, NRZI encoder, repeat filter, and parity checker.

The transmit mux is used to select the source of data to be transmitted. The source could be either of the two transmit buses (TA or TB), or the output of the smoother. The selected data is clocked into the register on the rising edge of BCLKIN. The data then goes simultaneously to the encoder, parity checker, and repeat filter. The register is forced to a quiet byte (QQ) during reset.

The parity checker circuit detects the presence of parity error in data coming from the transmit bus. If an error is found, this circuit flags the error to the repeat filter and drives the PARERR pin HIGH.

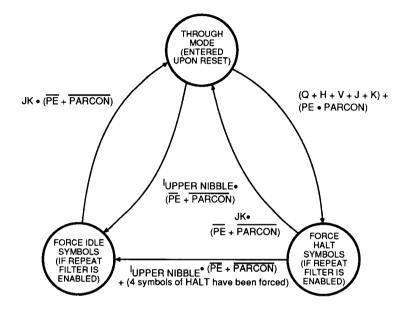

The purpose of the repeat filter is to detect the presence of invalid symbols such as halt, quiet, violation, isolated J or K, or parity error, and to force four symbols of halt followed by a string of idles onto the medium once any of these symbols is detected. The repeat filter implements the state machine shown in Figure 1.

The 4B/5B encoder performs the data conversion (binary to 4B/5B) for both the upper and lower nibbles of the register contents as shown in Table 1A.

The select circuit is used to choose symbols from either the 4B/5B encoder, the line state encoder, or the repeat filter for transmission. The select circuit chooses the encoder output only when either the control register (CRo) enables the repeat filter and the repeat filter does not force any control symbols, or when the repeat filter is

not enabled and the line state encoder is not forcing any line state symbols.

The 10-bit parallel data from select is serialized using the shift register. This is a 10-bit parallel-to-serial shift register which is parallel loaded with the output of select on the falling edge of BCLKIN and shifted out using the transmit bit clock. The most significant bit of the upper nibble is transmitted first.

The output from the shift register is clocked into the NRZI encoder using the bit clock. Its output is logic "0" whenever the ENDEC is reset or when quiet symbols are forced onto the network. In loopback and short loopback modes, TX is held at logic "0" (RLTX and RLTY remain unaffected).

# Abbreviations:

Parity Error

PARCON: Parity Error Convert (CR2, bit 0)

Q: Quiet Symbol

H: Halt Symbol

V: Violation (any bit pattern not defined in Table 1)

J.K: Start Delimiters Logical "OR" function +: Logical "AND" function

09732-004B

Figure 1. Repeat Filter State Machine

Am7984A 5-13

Table 1A. FDDI Encoding Table

| Trans<br>C | smit Bus<br>Data | NRZ C<br>Symbol | ODE<br>12345 |

|------------|------------------|-----------------|--------------|

| 0          | 0000             | 0               | 11110        |

| 0          | 0001             | 1               | 01001        |

| 0          | 0010             | 2<br>3          | 10100        |

| 0          | 0011             | 3               | 10101        |

| Ó          | 0100             | 4               | 01010        |

| 0          | 0101             | 5               | 01011        |

| Ö          | 0110             | 6               | 01110        |

| 0          | 0111             | 7               | 01111        |

| Ó          | 1000             | 8               | 10010        |

| Ō          | 1001             | 9               | 10011        |

| Ö          | 1010             | Α               | 10110        |

| Ö          | 1011             | В               | 10111        |

| Ö          | 1100             | С               | 11010        |

| 0          | 1101             | D               | 11011        |

| Ō          | 1110             | Ε               | 11100        |

| ō          | 1111             | F               | 11101        |

| i          | 0100             | Н               | 00100        |

| i          | 0111             | 1               | 11111        |

| i          | 1100             | j               | 11000        |

| 1          | 0011             | ĸ               | 10001        |

| i          | 0000             | Q               | 00000        |

| 1          | 0001             | R               | 00111        |

| i          | 1001             | S               | 11001        |

| i          | 1101             | Т               | 01101        |

|            |                  |                 |              |

#### Notes:

- Any unused combination including H, Q, V, and isolated J, Ks are treated according to Figure 1.

- 2) Order of NRZI code transmission: 1, 2, 3, 4, 5.

- When the ENDEC is in the unfiltered encoded mode, these unused combinations are encoded as shown.

| 1 | 0010 | 00000 (Q) |

|---|------|-----------|

| 1 | 0101 | 00101 (V) |

| 1 | 0110 | 01000 (H) |

| 1 | 1000 | 00110 (V) |

| 1 | 1010 | 11000 (J) |

| 1 | 1011 | 11001 (S) |

| 1 | 1110 | 11000 (J) |

| 1 | 1111 | 11111 (l) |

|   |      |           |

## Symbol Notation:

0,1...F = Hexadecimal digits

H, I, J, K, Q, R, S, T = Network control symbols

H = Halt symbol

I = Idle symbol

J = First-Half Start Delimiter

K = Second-Half Start Delimiter

Q = Quiet symbol

R = Reset

S = Set

T = Terminate

Table 1B. FDDI Decoding Table

| NRZ<br>CODE | SYMBOL | DECODER<br>C | OUTPUT<br>DATA |

|-------------|--------|--------------|----------------|

| 11110       | 0      | 0            | 0000           |

| 01001       | 1      | 0            | 0001           |

| 10100       | 2      | 0            | 0010           |

| 10101       | 3      | 0            | 0011           |

| 01010       | 4      | 0            | 0100           |

| 01011       | 5      | 0            | 0101           |

| 01110       | 6      | 0            | 0110           |

| 01111       | 7      | 0            | 0111           |

| 10010       | 8      | 0            | 1000           |

| 10011       | 9      | 0            | 1001           |

| 10110       | Α      | 0            | 1010           |

| 10111       | В      | 0            | 1011           |

| 11010       | С      | 0            | 1100           |

| 11011       | D      | 0            | 1101           |

| 11100       | E      | 0            | 1110           |

| 11101       | F      | 0            | 1111           |

| 00100       | Н      | 1            | 0100           |

| 10000       | Н      | 1            | 0100           |

| 01000       | н      | 1            | 0100           |

| 00010       | н      | 1            | 0100           |

| 00001       | H      | 1            | 0100           |

| 11111       | ı.     | 1            | 0111           |

| 11000       | Ĵ      | 1            | 1100           |

| 10001       | K      | 1            | 0011           |

| 00000       | Q      | 1            | 0000           |

| 00111       | R      | 1            | 0001           |

| 11001       | S      | 1            | 1001           |

| 01101       | Ţ      | 1            | 1101           |

| 00011       | V      | 1            | 1000           |

| 00101       | V      | 1            | 1000           |

| 00110       | V.     | 1            | 1000           |

| 01100       | V      | 1            | 1000           |

Symbol Notation:

0, 1....F = Hexadecimal digits

H, I, J, K, Q, R, S, T, V: = Network Control Symbols

#### Note:

Overflow/Underflow in the elasticity buffer causes violation (11000) symbols to be sent out to the sync register. Also, line state conditions QLS, HLS, MLS, NLS in the line state decode logic cause PHY invalid (11111) symbols to be sent out on the R-bus.

|    | Table 2. Line State Identification |    |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|----|------------------------------------|----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| S2 | S1                                 | S0 | STATE | DEFINITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 0  | 0                                  | 0  | LSU   | Line State Unknown. The criteria for entering or remaining in any other line state have not been met.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 0  | 0                                  | 1  | NLS   | Noise Line State is entered upon the occurrence of 16 potential noise events without satisfying the criteria for entry into another line state. Potential noise events are the decoding of symbol pairs (with CARDET active) containing at least one Q,H,J,K, or V symbol or the detection of elasticity buffer overflow/underflow. Decoding of data R, S,and T when the last known state is not ALS or ILS is also considered a noise event. NLS is exited when the criteria for entry into any other line state is satisfied. |  |  |

| 0  | 1                                  | 0  | MLS   | Master Line State is entered upon the reception of eight or nine consecutive HQ or<br>QH symbol pairs when CARDET is HIGH. MLS is exited upon receipt of any symbol<br>pair other than HQ or QH, or when CARDET goes LOW.                                                                                                                                                                                                                                                                                                       |  |  |

| 0  | 1                                  | 1  | ILS   | Idle Line State is entered upon receipt of four or five consecutive idle symbols while<br>CARDET is HIGH. ILS is exited upon receipt of any symbol other than idle or when<br>CARDET goes LOW.                                                                                                                                                                                                                                                                                                                                  |  |  |

| 1  | 0                                  | 0  | HLS   | Halt Line State is entered upon receipt of 16 or 17 consecutive H symbols while<br>CARDET is HIGH. HLS is exited upon receipt of any symbol other than H when<br>CARDET is HIGH.                                                                                                                                                                                                                                                                                                                                                |  |  |

| 1  | 0                                  | 1  | QLS   | Quiet Line State is entered upon receipt of 16 or 17 consecutive Q symbols, or whenever CARDET goes LOW. QLS is exited upon receipt of any symbol other than Q when CARDET is HIGH.                                                                                                                                                                                                                                                                                                                                             |  |  |

| 1  | 1                                  | 0  | ALS   | Active Line State is entered upon receipt of a JK symbol pair while CARDET is HIGH. ALS is exited whenever CARDET goes LOW, ILS is entered, or when any control symbol other than I, R, S, or T is received.                                                                                                                                                                                                                                                                                                                    |  |  |

| 1  | 1                                  | 1  | OVUF  | Elasticity Buffer Overflow/ Underflow.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

#### Line State Decoder, Timer, and Bus Interface Unit

The purpose of line state decoder logic is to detect the presence of quiet, halt, master, idle, active, or noise line states at the sync register output. An 8-to-3 priority encoder decides the priority of line states indicated on pins So-2. A table showing the output is shown in Table 2. OVUF indicates overflow/underflow of the elasticity buffer present inside the ENDEC. OVUF gets the highest priority followed by ALS, QLS, HLS, ILS, MLS, and finally NLS. When two line states are simultaneously reached, the one with the higher priority is flagged.

The function of the bus interface unit is to provide the ENDEC with an interface to the NP for the purpose of:

- Connection management;

- Selecting various loopback and repeat modes for the ENDEC/EDS combination;

- 3) Enabling either the TA or TB bus for transmission:

- Forcing quiet, master, idle, or halt symbols onto the medium;

- Enabling the repeat filter:

- Enabling conversion of parity errors by the repeat filter;

- Indicating line state status and the contents of control registers;

- 8) Monitoring the smoother extensions:

- Software reset of the ENDEC and/or smoother:

- 10) Selecting odd or even parity of the transmit input.

Data from the 3-bit NPo2 may be written into the four control registers (described in the "User-Accessible Registers" section) in the ENDEC. These control registers are used to help perform items 1-10 listed above. Communication is established with the NP through the use of the  $\overline{CSI}$ ,  $\overline{DS}$ ,  $\overline{READY}$  and  $C/\overline{D}$ . The Bus Interface Unit also synchronizes the  $\overline{RESET}$  signal with BCLKIN before distributing it to the rest of the chip.

#### Receiver

#### Decoder

The decoder section consists of an NRZI to NRZ converter, a shifter, two 4B/5B decoders, and a parity generator. Data is first processed by the NRZI to NRZ converter. Then the shifter performs serial-to-10-bit parallel conversion of the NRZ data. The shifted symbol pair is then parallel-loaded into a register in the 4B/5B decoder; this transfer is timed by the framing and control logic. The decoder then performs 4B/5B decoding for the two nibbles of data and parity is generated for the 10-bit decoded output.

## Framing and Control Logic

The purpose of the framing and control logic is to generate timing pulses to load data into the decoder and to write data into the elasticity buffer. The timing of these pulses is based on the byte boundary information provided by the Start Delimiter (SD) of each frame.

Elasticity Buffer

The purpose of the elasticity buffer is to provide temporary storage for the decoded data before it is loaded into the sync. register and clocked out to the receive mux. This temporary storage is necessary because of the difference in frequency that may exist between the transmit clock and the receive clock which is recovered from the received bit stream. The maximum difference allowed by ANSI X3T9.5 is 100 parts per million.

The elasticity buffer also provides an indication of overflow/underflow and JK (Start Delimiter) detection to the line state decoder logic. These signals are synchronous to BCLKIN. Whenever overflow/underflow occurs, the elasticity buffer is allowed to modify up to three bytes of input to recenter correctly. Violation symbols are flagged during overflow/underflow.

Sync. Register

Data is clocked out from the elasticity buffer through the sync, register using delayed BCLKIN. The sync register is constructed in two stages to reduce the effects of metastability. It forces violation symbols (11000) into the receive mux under two conditions. The first is elasticity buffer overflow/underflow. The second case is when the noise line state (NLS) as described in the line state decoder section goes active. The sync. register will send violation symbols for 160 byte clock cycles once NLS goes active. The sync register will resume sending receive data from the elasticity buffer to the receive mux after 160 byte-clock cycles, even if NLS is still active. It is allowed 96 byte times to examine this data and decide whether NLS still exists. If so, the ENDEC will continue holding NLS active, and the sync. register will force violation symbols for another 160 byte-time period.

#### Smoother

The smoother is included in the ENDEC to ensure with a very high probability that at least 6 bytes of preamble precede a frame. The station that originates a frame

initially has 8 bytes of preamble. If the next station is a slower station, the elasticity buffer could delete a byte of Idle if the elasticity buffer implementation is bytewide. If succeeding stations are also slower, they could also delete an additional 2 bytes of Idle, causing the number of deleted bytes to be 3. This 5-byte interframe gap could prove inadequate for a station to copy its addressed frames because of the handshaking that goes on at the end of frames. The smoother helps to reduce the number of lost frames.

#### Receive Mux

This circuit is used to send data from the smoother, TA-, or TB-bus to the FORMAC on the R-bus. The selection is made by the TMUXSEL bit and the LPBK1 and LPBK0 bits in control register 1 (CR1). When any of QLS, HLS, NLS or MLS exists, this mux sends a pair of Phy Invalid symbols (11111) out on the R-bus. The Smoother output has a 0-, 1-, or 2- byte delay depending whether it is in extension 0,1,2, respectively. When data from the TA-or TB-bus is selected, it is sent through a register clocked using BCLKIN.

## **Crystal Oscillator**

A parallel-mode oscillator operating at the fundamental frequency of an external crystal generates the transmit byte-rate clock (BCLKOUT). This is the master clock which synchronizes the other members of the SUPERNET chip-set. Some applications require more than one ENDEC to be used in a station; in these cases, BCLKOUT from only one of the local ENDECs is used.

# Transmit PLL and Clock Logic

An internal PLL is used to generate a transmit bit clock. The PLL is referenced to BCLKIN, which is intended to be driven by BCLKOUT (described above). This section also drives a nibble clock, operating at twice the frequency of BCLKIN.

# **Operational Modes**

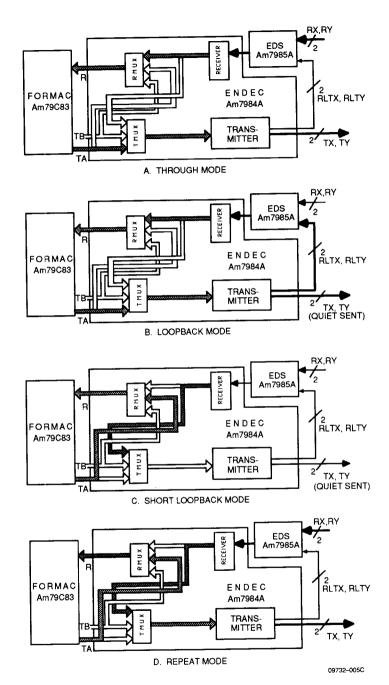

The ENDEC can operate any of the four modes listed in Table 3-3 and as shown in Figure 2. Bits LPBK<sub>1</sub> and LPBK<sub>0</sub> of control register CR<sub>1</sub> (located in the ENDEC) define the mode of operation.

In "through" mode, data from the FORMAC is transmitted onto the serial link, and the data received from the network is passed onto the FORMAC. In "loopback" mode, data from the transmit output is directly looped back to the receive input (RLTX, RLTY) of the EDS. This is useful for self-diagnostics. In "short loopback" mode. data from one of the transmit bus inputs to the ENDEC is directly looped back to the receive bus output, without going through the rest of the transmit path. In "repeat" mode, receive data is repeated onto the transmit path without being sent to the FORMAC. Also in "repeat" mode, the selected transmit bus input is looped back to the receive bus output as in "short loopback" mode. This is useful in connection management and station reconfiguration. Quiet symbols are sent out on pins TX and TY in "short loopback" or "loopback" modes.

#### **User-Accessible Registers**

There are four control registers (CR<sub>0</sub>, CR<sub>1</sub>, CR<sub>2</sub>, and CR<sub>3</sub>) and one pointer register (CR pointer) in the ENDEC. Each of these is 3 bits wide as shown in Table 3-1. Their contents are cleared to logic "0" when the Am7984A ENDEC is reset.

Table 3-1. Control Register and Pointer Bit Assignments

| Register        | Bit 2       | Bit 1       | (LSB)<br>Bit 0 |

|-----------------|-------------|-------------|----------------|

| CR₀             | C2          | C1          | CO             |

| CR <sub>1</sub> | TMUXSEL     | LPBK1       | LPBK0          |

| CR <sub>2</sub> | RESET       | EVEN/ODD    | PARCON         |

| CR₃             | EXTENSION 2 | EXTENSION 1 | SMRESET        |

| CR Pointe       | er REGSEL2  | REGSEL1     | REGSEL0        |

(All bits = 0 after reset.SMRESET and RESET are cleared once set)

Table 3-2. CRo (Force Line States)

| C2                              | C1                         | CO                              | Function                                                                                                   | Description                                                                                                                                                                                                                                                  |

|---------------------------------|----------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>0<br>0<br>0<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0 | 0<br>1<br>0<br>1<br>0<br>1<br>0 | Force Quiet Force Master Force Halt Force Idle Enable Repeat Filter Force JKILS Force IQ Unfiltered Encode | Q bytes continually forced QH bytes continually forced Halt bytes continually forced Idle bytes continuously forced Repeat filter enabled JK followed by continuous Idle bytes IQ bytes continuously forced Input bytes to encoder without repeat filtering. |

Control Register 0 – (CR<sub>0</sub>) programs the ENDEC to transmit data or various line states as described in Table 3-2. These line states are used for connection management and station reconfiguration.

Control Register 1– (CR<sub>1</sub>) selects either the TA-bus or the TB-bus inputs to the ENDEC for transmission onto the media. This is accomplished by setting the TMUX-SEL bit. Logic "0" selects the TB-bus and logic "1" chooses the TA-bus. CR<sub>1</sub> also forces the ENDEC and EDS into one of the operational modes described earlier and shown in Table 3-3.

| Table 3-3. CR, (Loopback Modes) |       |                |  |

|---------------------------------|-------|----------------|--|

| LPBK1                           | LPBK₀ | Function       |  |

| 0                               | 0     | Through        |  |

| Ō                               | 1     | Loopback       |  |

| 1                               | 0     | Short Loopback |  |

| 1                               | 1     | Repeat         |  |

Control Register 2 – (CR<sub>2</sub>) contains the RESET, EVEN/ODD and PARCON bits. When RESET is set to 1, the ENDEC gets reset and the bit gets cleared. When EVEN/ODD is 1, the even parity mode of operation is chosen for the ENDEC. When EVEN/ODD is 0, odd parity mode of operation is chosen for the ENDEC. PARCON, when set to logic "1", enables the conversion of parity by the repeat filter state machine.

Control Register 3 – (CR3) is used to reset the smoother (smoother is not extended) by means of SMRESET bit and can also be used to read the status of the smoother through EXTENSION2 and EXTENSION1 bits. When the EXTENSION2 bit is logic "1", the smoother is extended by two bytes. When the EXTENSION1 bit is logic "1", the smoother is extended by one byte. The SMRESET bit, once it resets the smoother, gets cleared to "0".

Pointer Register (CR pointer) – selects one of the control registers to be written or read by the NP as shown in Table 3-1. It can also select the line status of the decoded data as indicated by the  $S_{0.2}$  pins by choosing CR Pointer = 011. This register can be written, but not read.

| Table 3-4. Pointer Register (CR Pointer) |   |                 |  |  |  |

|------------------------------------------|---|-----------------|--|--|--|

| REGSEL2 REGSEL1 REG                      |   |                 |  |  |  |

| 0                                        | 0 | CR₀             |  |  |  |

| 0                                        | 1 | CR <sub>1</sub> |  |  |  |

| 1                                        | 0 | CR <sub>2</sub> |  |  |  |

| 1                                        | 1 | Status          |  |  |  |

| 0                                        | 0 | CR₃             |  |  |  |

|                                          |   |                 |  |  |  |

Loading and reading these registers is done using the  $C/\overline{D}$ ,  $\overline{DS}$ ,  $\overline{CSI}$ ,  $R/\overline{W}$ , and  $NP_{0\cdot 2}$  pins.  $C/\overline{D}$  is analogous to the INST<sub>0·3</sub> lines on the RBC, DPC, and FORMAC. Since the RESET and SMRESET bits are automatically cleared, it is not meaningful to read them.

# **Diagnostic Features**

The ENDEC and EDS together can operate in various loopback modes. These are described in the "Operational Modes" section of this data sheet. The ENDEC also has a TEST pin which disables the internal VCO in the "PLL and clock" section of the ENDEC. The

CTX/CTX pins can then be used to bring in the transmit bit clock for test purposes. When the TEST pin is floating, the on-chip crystal oscillator can be used as a bit rate oscillator.

#### Global Issues

Following are the global objectives for the ENDEC.

- Frequency Stability of bit clock: better than ±50 parts per million.

- Maximum latency through ENDEC with Smoother unextended: 65 bits.

- Maximum latency through ENDEC with Smoother extended once: 75 bits.

- Maximum latency through ENDEC with Smoother extended twice: 85 bits.

# **Crystal Specifications**

Frequency (fundamental) 12.5MHz Resonant Mode Parallel Load Capacitor (Correlation) 75pF Operating Temperature Range 0 to 70°C Temperature Stability ± 25 parts per million (Including calibration tolerance) Drive Level (Correlation) Effective Series Resistance 25 ohms (max) Holder Type Low Profile Aging for 10 years ± 10 parts per million

Figure 2. Loopback Paths (Active data paths are highlighted)

Figure 3: ENDEC-EDS Interconnections in a Dual-attach Station

09732-006C

# **ABSOLUTE MAXIMUM RATINGS**

5-22

Storage Temperature -55 to +125°C Ambient Temperature Under Bias Supply Voltage to Ground Potential -0.5 to +7.0 V Continuous DC Voltage Applied to Outputs -0.5 to Vcc Max. DC Input Voltage -0.5 to +5.5 V ±100 mA DC Output Current DC Input Current -30 to +5.0 mA

-65 to +150°C

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

# **OPERATING RANGES**

Commercial (C) Devices

0 to +70°C Ambient Temperature (TA) +4.5 to +5.5 V Supply Voltage (V∞)

**Extended Commercial (E) Devices**

Case Temperature (Tc) -55 to +125°C Supply Voltage (Vcc) +4.5 to +5.5 V

Operating ranges define those limits between which the functionality of the device is guaranteed.

Am7984A

| DC CHARACTERISTICS over COMMERCIAL of | perating range unless otherwise specified |

|---------------------------------------|-------------------------------------------|

|---------------------------------------|-------------------------------------------|

| Parameter<br>Symbol | Parameter<br>Description                             | Test Conditions (Notes 1 & 5)          |                                             | Min. | Max.               | Unit |

|---------------------|------------------------------------------------------|----------------------------------------|---------------------------------------------|------|--------------------|------|

| TTL INPUT           | PINS (Note7)                                         |                                        |                                             |      |                    |      |

| ViH                 | Input HIGH Voltage                                   | Vcc = Max (note 6                      | 6).                                         | 2.0  |                    | ٧    |

| VIL                 | Input LOW Voltage                                    | Vcc = Max.<br>(Note 6)                 |                                             |      | 0.8                | ٧    |

| Vı                  | Input Clamp Voltage                                  | Vcc = Min. I <sub>IN</sub> = -1        | 8 mA                                        |      | -1.5               | V    |

| liL                 | Input LOW Current                                    | Vcc = Max.,<br>V <sub>IN</sub> = 0.4 V | All Except NP <sub>0-2</sub> , CSI, DS, R/W |      | <b>–400</b>        | μА   |

|                     |                                                      |                                        | NP <sub>0-2,</sub><br>CSI, DS, R/W          |      | -550               | μА   |

| Ін                  | Input HIGH Current                                   | Vcc = Max.,                            | All Except NP <sub>0-2</sub>                |      | 50                 | μΑ   |

|                     |                                                      | $V_{IN} = 2.7 V$                       | NP <sub>0-2</sub>                           |      | 100                | μА   |

| lı .                | Input Leakage Current                                | Vcc = Max.,                            | All Except NP <sub>0-2</sub>                |      | 50                 | μА   |

|                     |                                                      | Vin = 5.5 V                            | NP <sub>0-2</sub>                           |      | 100                | μA   |

| TTL OUTP            | UT PINS (Note8)                                      |                                        |                                             |      |                    |      |

| Vон                 | Output HIGH Voltage<br>(All Outputs Except<br>READY) | Vcc = Min.                             | Іон = -1 mA                                 | 2.4  |                    | ٧    |

| Vol                 | Output LOW Voltage                                   | Vcc = Min.                             | loL = 4 mA                                  |      | 0.5                | ٧    |

| Isc                 | Output Short-Circuit<br>Current                      | Vcc = Max.<br>(Note 4)                 | All outputs<br>except READY<br>and NPo2     | -15  | -85                | mA   |

|                     |                                                      |                                        | NP <sub>0-2</sub>                           | -15  | -100               | mA   |

| ICEX                | Output Leakage Current (READY pin only)              | VIN = 2.4 V                            |                                             |      | 50                 | μА   |

| CML/ECL             | INPUT PINS (SERDAT, SE                               | RDAT, CRX, CRX,                        | CTX, CTX )                                  |      |                    |      |

| IIL.                | Input LOW Current                                    | Vcc = Max<br>Vin = Vcc - 1.81          |                                             | 0.5  |                    | μА   |

| fier                | Input HIGH Current                                   | Vcc = Max<br>Vin = Vcc                 |                                             |      | 500                | μΑ   |

| VDIFF               | Differential Input<br>Voltage                        | Vcc = Max                              |                                             | 0.2  | 1.1                | ٧    |

| Vicm                | Input Common Mode<br>Voltage                         | (Note 9)                               |                                             | 3.05 | V∞-<br>1/2 (VDIFF) | V    |

| DC CHARACTERISTICS (Conti |

|---------------------------|

|---------------------------|

| Parameter<br>Symbol | Parameter<br>Description                      | Test Conditions (Notes 1 and 5)              |                 | Min.           | Max.           | Unit       |

|---------------------|-----------------------------------------------|----------------------------------------------|-----------------|----------------|----------------|------------|

| ECL INPUT           | F PINS (CARDET)                               |                                              |                 |                |                |            |

| Vins                | Input HIGH Voltage                            | Vcc = Max. (Note 6                           | 5)              | Vcc -<br>1.165 | Vcc -<br>0.88  | ٧          |

| Vils                | Input LOW Voltage                             | Vcc = Max. (Note 6)                          |                 | Vcc -<br>1.81  | Vcc -<br>1.475 | V          |

| lı.                 | Input LOW Current                             | Vcc = Max,<br>V <sub>IN</sub> = Vcc - 1.81V  | ·               |                |                | μА         |

| Ін                  | Input HIGH Current                            | Vcc = Max,<br>V <sub>IN</sub> = Vcc - 0.88 V |                 |                | 220            | μΑ         |

| ECL OUTP            | PUT PINS (TX, TY, RLTX, R                     | LTY, EBCLK, EBC                              | LK, ULC, LOOP)  |                |                |            |

| Vон                 | Output HIGH Voltage                           | Vcc = Min., ECL Load                         |                 | Vcc -<br>1.025 | Vcc -<br>0.88  | ٧          |

| Vol                 | Output LOW Voltage                            | Vcc = Min., ECL Load                         |                 | Vcc -<br>1.81  | Vcc -<br>1.62  | ٧          |

| CRYSTAL             | PINS (XTAL <sub>1</sub> , XTAL <sub>2</sub> ) |                                              |                 |                |                |            |

| HLX                 | Input LOW Current XTAL <sub>1</sub>           | Vin = 0 V                                    |                 |                | -1             | mA         |

| Інх                 | Input HIGH Current XTAL                       | V <sub>IN</sub> = 3.5 V                      |                 |                | +1             | mA         |

| POWER S             | UPPLY PINS (Vcc1, Vcc2, Vc                    | 23)                                          |                 |                |                |            |

| Icc                 | Supply Current                                | Vcc1 = Vcc2                                  | Pin Vccı (TTL)  |                |                | mA         |

|                     | (Note 10)                                     | = Vcc3<br>= Max.,                            | Pin Vcc2 (CML)  |                |                | mA         |

|                     |                                               | Ta = +25°C                                   | Pin Vcc3 (ECL)  |                | · · · · ·      | mA         |

|                     |                                               | Vcc1 = Vcc2<br>= Vcc3                        | Total @ + 125°C |                |                | mA         |

|                     |                                               | = Max                                        | Total @ +25°C   |                | 930            | m <i>A</i> |

|                     |                                               |                                              | Total @ - 55°C  |                |                | m/         |

# SWITCHING CHARACTERISTICS over COMMERCIAL operating range unless otherwise specified (Notes 4 & 11)

| No.   | Parameter                                                                                                                     | Signal Name                                                                                                        | Min.              | Max.                | Unit |

|-------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------|---------------------|------|

| 1     | Clock Period                                                                                                                  | BCLKIN                                                                                                             | 80                |                     | ns   |

| 2     | HIGH Pulse Width                                                                                                              | BCLKIN                                                                                                             | 35                |                     | ns   |

| 3     | LOW Pulse Width                                                                                                               | BCLKIN                                                                                                             | 35                |                     | ns   |

| 4     | Setup Time Before BCLKIN ↑                                                                                                    | $\overline{\text{CSI}}$ , $\overline{\text{DS}}$ , $\text{C/}\overline{\text{D}}$ , $\text{R/}\overline{\text{W}}$ | 36                |                     | ns   |

| 5     | Hold Time After BCLKIN ↑                                                                                                      | ĈŜĪ, R∕W                                                                                                           | 8                 |                     | ns   |

| 6     | Hold Time After BCLKIN ↑                                                                                                      | DS .                                                                                                               | 8                 |                     | ns   |

| 7     | Hold Time After BCLKIN ↑                                                                                                      | C/D                                                                                                                | 8                 |                     | ns   |

| 8     | Hold Time After BCLKIN ↑                                                                                                      | NP <sub>0-2</sub>                                                                                                  | 11                |                     | ns   |

| 9     | Setup Time Before BCLKIN ↑                                                                                                    | NP <sub>0-2</sub>                                                                                                  | 25                |                     | ns   |

| 10    | R/W↑, CSI ↓, DS ↓<br>(Whichever Occurs Last)<br>Until NP₀₂ is Enabled<br>(Synchronous Mode)                                   | NPo-2                                                                                                              | 0                 |                     | ns   |

| 11    | Signal Valid After BCLKIN↑                                                                                                    | NP <sub>0-2</sub>                                                                                                  |                   | (0.05 x T1)<br>+ 41 | ns   |

| 12    | Signal Invalid After BCLKIN ↑                                                                                                 | NPo-2                                                                                                              | (05 x T1)<br>+ 10 |                     | ns   |

| 13    | R/W↓, DS ↑, or CSI ↑ (Whichever Occurs First at the End of a Synchronous Read Cycle) to Bus Inactive                          | NP <sub>0-2</sub>                                                                                                  |                   | 30                  | ns   |

| 14    | Signal Invalid After DS ↑,<br>CSI ↑, or R/W ↓ (Whichever<br>Occurs First at the End of<br>a Synchronous Read Cycle)           | NP <sub>0-2</sub>                                                                                                  | 4                 |                     | ns   |

| 15    | Hold Time After DS ↑ or CSI ↑ (Whichever Occurs First in Asynchronous Write)                                                  | NP <sub>0-2</sub>                                                                                                  | 0                 |                     | ns   |

| 16-19 | Unused                                                                                                                        |                                                                                                                    |                   |                     |      |

| 20    | Setup Time Before CSI ↓ DS ↓ (Whichever Occurs Last in Asynchronous Read/Write)                                               | R/ <del>W</del> ↓ (Write)<br>or R/ <del>W</del> ↑ (Read),<br>C/D                                                   | 0                 |                     | ns   |

| 21    | Unused                                                                                                                        |                                                                                                                    |                   |                     |      |

| 22    | Pulse Width HIGH (Asynchro-<br>nous Read or Write, From<br>the First of these Signals<br>to go HIGH to the Last to<br>go LOW) | CSI, DS                                                                                                            | (1.5 x T1)        |                     | ns   |

| 23    | Hold Time After DS ↑ or CSI ↑ (Whichever Occurs First at the End of Asynchronous Read/Write)                                  | R/₩,C/Ď                                                                                                            | 0                 |                     | ns   |

| 24    | Delay Time From DS ↓                                                                                                          | READY                                                                                                              | (2 x T1)          | (3 x T1)<br>+ 40    | ns   |

| 25    | Delay Time From DS ↑                                                                                                          | READY                                                                                                              |                   | 40                  | ns   |

| 26    | Bus Enabled After DS ↓ or CSI ↓ (Whichever Occurs Last in Asynchronous Read)                                                  | NP <sub>0-2</sub>                                                                                                  | 0                 |                     | ns   |

Am7984A

# **SWITCHING CHARACTERISTICS (Continued)**

| No. | Parameter                                                                              | Signal Name                                                                    | Min.                  | Max.                | Unit |

|-----|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------|---------------------|------|

| 27  | Bus Valid After DS ↓ or<br>CSI ↓ (Whichever Occurs<br>Last in Asynchronous Read)       | NP <sub>0-2</sub>                                                              |                       | (2 x T1)<br>+ 60    | ns   |

| 28  | Signal Invalid After DS ↑ or<br>CSI ↑ (Whichever Occurs<br>First in Asynchronous Read) | NP <sub>0-2</sub>                                                              | 2                     |                     | ns   |

| 29  | Bus Disabled After DS ↑<br>or CSI ↑ (Whichever Occurs<br>First in Asynchronous Read)   | NP <sub>0-2</sub>                                                              |                       | 30                  | ns   |

| 30  | Setup Time Before DS ↓ or CSI ↓ (Whichever Occurs Last in Asynchro- nous Write)        | NP <sub>0-2</sub>                                                              | (-2 x T1)<br>- 6      |                     | ns   |

| 31  | Setup Time Before BCLKIN ↑                                                             | TA <sub>0-7</sub> , TACL, TACU,<br>TAP, TB <sub>0-7</sub> , TBCL,<br>TBCU, TBP | 7                     |                     | ns   |

| 32  | Hold Time After BCLKIN ↑                                                               | TA <sub>0-7</sub> , TACL, TACU,<br>TAP, TB <sub>0-7</sub> , TBCL,<br>TBCU, TBP | 10                    |                     | ns   |

| 33  | Signal Valid After BCLKIN ↑                                                            | R <sub>0-7</sub> , RCL, RCU, RP                                                |                       | (0.05 x T1)<br>+ 36 | ns   |

| 34  | Signal Invalid After BCLKIN↑                                                           | R <sub>0-7</sub> , RCL, RCU, RP                                                | (- 0.05 x T1)<br>+ 19 |                     |      |

| 35  | Signal Valid After BCLKIN ↑                                                            | S <sub>0-2</sub>                                                               |                       | (0.05 x T1)<br>+ 32 | ns   |

| 36  | Signal Invalid After BCLKIN ↑                                                          | S <sub>0-2</sub>                                                               | (-0.05 x T1)<br>+ 6   |                     | ns   |

| 37  | Signal Valid After BCLKIN 1                                                            | PARERR                                                                         |                       | 50                  | ns   |

| 38  | Signal Invalid After BCLKIN↑                                                           | PARERR                                                                         | 2                     |                     | ns   |

| 39  | Pulse Width LOW                                                                        | RESET                                                                          | (3 x T1)              |                     | ns   |

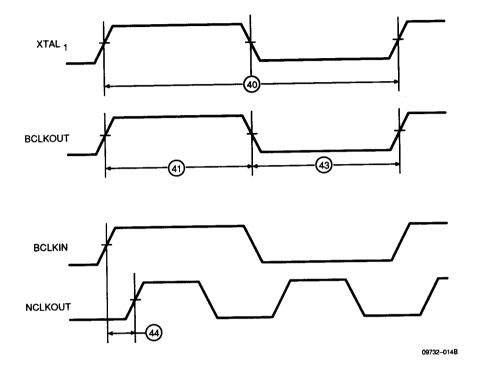

| 40  | Unused                                                                                 |                                                                                |                       |                     | ns   |

| 41  | Pulse Width HIGH                                                                       | BCLKOUT                                                                        | 35                    |                     | ns   |

| 42  | Unused                                                                                 |                                                                                |                       |                     |      |

| 43  | Pulse Width LOW                                                                        | BCLKOUT                                                                        | 35                    |                     | ns   |

| 44  | Skew From BCLKIN↑                                                                      | NCLKOUT ↑                                                                      |                       | (0.05 x T1)<br>+ 25 | ns   |

| 45  | Unused                                                                                 |                                                                                |                       |                     |      |

| 46  | Unused                                                                                 |                                                                                |                       |                     |      |

| 47  | Unused                                                                                 |                                                                                |                       |                     |      |

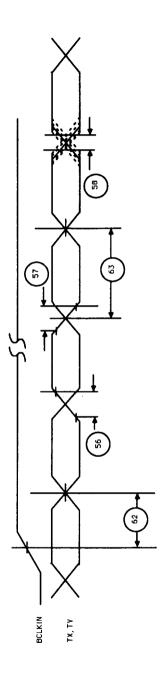

| 48A | Setup time Before CRX↑                                                                 | SERDAT, SERDAT                                                                 | 2                     |                     | ns   |

| 48B | Hold Time After CRX ↑                                                                  | SERDAT, SERDAT                                                                 | 0                     |                     | ns   |

| 49  | Signal Valid After BCLKIN↑                                                             | LOOP                                                                           |                       | 35                  | ns   |

| 50  | Signal Valid After BCLKIN ↑                                                            | ÜLC                                                                            |                       | (0.05 x T1)<br>+ 20 | ns   |

| 51  | CARDET ↓ or ↑ to ULC ↓ or ↑                                                            |                                                                                |                       | 30                  | ns   |

| 52  | Pulse Width HIGH                                                                       | EBCLK, EBCLK                                                                   | 35                    |                     | ns   |

| 53  | Pulse Width LOW                                                                        | EBCLK, EBCLK                                                                   | 35                    |                     | ns   |

| 54  | Unused                                                                                 |                                                                                |                       |                     |      |

| 55  | Unused                                                                                 |                                                                                |                       |                     |      |

| 56  | Rise Time (See note 2)                                                                 | TX, TY                                                                         | 0.8                   | 3                   | ns   |

# **SWITCHING CHARACTERISTICS (Continued)**

| No. | Parameter                            | Signal Name        | Min. | Max.      | Unit |

|-----|--------------------------------------|--------------------|------|-----------|------|

| 57  | Fall Time (See note 2)               | TX, TY             | 0.8  | 3         | ns   |

| 58  | Duty Cycle Distortion (peak to peak) | TX, TY             |      | 0.4       | ns   |

| 59  | Unused                               |                    |      |           |      |

| 60  | Unused                               |                    |      |           |      |

| 61  | Unused                               |                    |      |           |      |

| 62  | Delay from BCLKIN ↑                  | TX, TY, RLTX, RLTY |      | 0.75 x T1 | ns   |

| 63  | Transition Interval                  | TX, TY             | 8    | 80        | ns   |

| 64  | Setup time before CTX ↑ (Test Mode)  | BCLKIN             | 1    |           | ns   |

| 65  | Hold time after CTX ↑ (Test Mode)    | BCLKIN             | 1    |           | ns   |

#### Notes:

- 1. For conditions shown as Min. or Max., use the appropriate value specified under operating range.

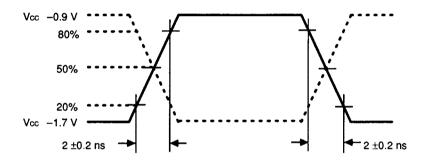

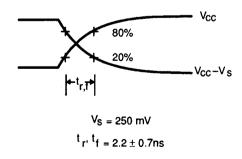

- 2. Rise and fall time measurements are made at 20% and 80% points.

- 3. Not more than one output should be shorted at a time. Duration of the short-circuit test should not exceed one second.

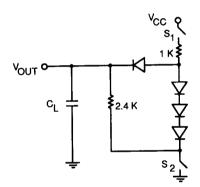

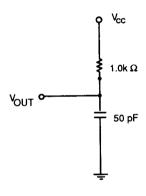

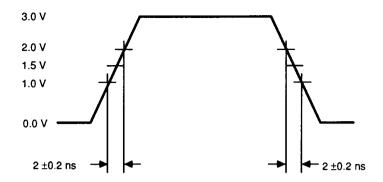

- 4. All timing references are made with respect to +1.5 V for TTL-level signals, to the 50% point between V<sub>OH</sub> and V<sub>OL</sub> for ECL signals and CML/ECL signals. ECL input rise and fall times must be 2 ns ± 0.2 ns between 20% and 80% points. TTL input rise and fall times must be 2 ns ± 0.2 ns between 1 V and 2 V. Output-enabled and disabled times are referenced to 0.5 V above V<sub>OL</sub> or below VOH.

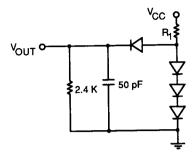

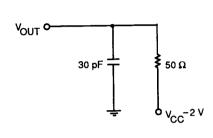

- Nominal input voltages are 0 or 3 V on TTL pins, V<sub>cc</sub> 0.9 or V<sub>cc</sub> 1.7 V on ECL input pins. Nominal input voltages on CML/ECL input pins are load dependent. For a load of 50 ohms connected to V<sub>cc</sub> and 30 pF to ground, CML/ECL nominal voltages are between V<sub>cc</sub> and V<sub>cc</sub> 0.25 Volts.

- 6. Measured with device in test mode while monitoring output logic states.

- 7. TTL Input Pins: RESET, BCLKIN, TA<sub>0.7</sub>, TACL, TACU, TB<sub>0.7</sub>, TBCL, TBCU, TAP, TBP, CSI, DS, C/D, R/W, NP<sub>0.2</sub>, and BMODE.