## MSD95C01/02

T.52-33-63

# Storage $\mu$ -Controller for Direct Access (Disk) or Serial Access (Tape) Devices — S $\mu$ nDAe<sup>TM</sup>

#### APPLICATIONS SUPPORTED ☐ Embedded SCSI Drives When Used With Companion MSD95C00 SCSI Controller ☐ IBM PS/2 ESDI Adapter When Used With Companion MSD95C10 Micro Channel ESDI Interface Chip ☐ IBM AT Adapter When Used With Companion MSD95C15 AT Interface Chip ☐ Compatible With ESDI and SMD Disk Interfaces ☐ Interfaces to 8051, Z8 and 80188 Microprocessors ☐ Supports 3-Sector Prefetch for Unix® Applications ☐ Supports QIC-24 Tape: 5 Mb/sec GCR Data Transfers Read-After-Write ☐ Controls Optical Disks and Floppy Disks ☐ Modular Design for Easy Adaptation to Special Purpose Applications **FEATURES** 24 Mb/sec NRZ or 12 Mb/sec RLL, MFM, FM Disk Data **Transfers** ☐ Zero Latency Read Capability ☐ Choice of ECC: 32-bit IBM® Compatible ECC and one of the following: ·(MSD95C01): Computer Generated ECC Fully Programmable from One to 64 Bits in One Bit Increments. -(MSD95C02): Extended Reed-Solomon ECC Able

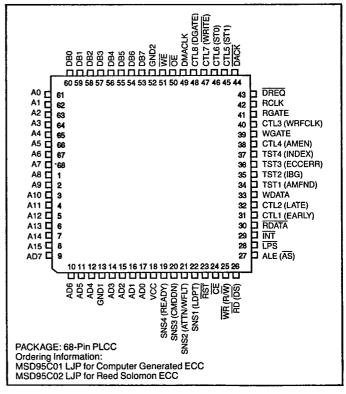

#### PIN CONFIGURATION

- ☐ 3-Channel Internal Double-Speed 64K (Externally Expandable) Ring Buffer DMA Controller

- ☐ Cache Buffer Management Allows Disk Data Transfers Without Processor Intervention

- □ Low Power CMOS with Standby Mode

#### **GENERAL DESCRIPTION**

The MSD95C01/02 is a high speed micro-programmable data path controller. It incorporates a triple channel DMA CONTROLLER, a RAM based MICROSEQUENCER, a sophisticated ECC generator/checker circuit, an RLL2, 7/MFM/FM/GCR Encoder/Decoder and a Parallel/Serial shift register in one 68 pin plastic package.

to Detect and Correct a 41 Bit Burst Error or Two

☐ Register Programmable Data Format via On-Chip

☐ Supports Transparent "On-The-Fly" Error Correction

Randomly Spaced 17 Bit Burst Errors.

Writeable Microsequencer

The MSD95C01/02 is built from a set of high level, function specific SuperCells™ that can be connected together in such a way as to adapt themselves to a special purpose customer requirement. The MSD95C01/02 can be combined in a circuit with standard local processor and static RAM chips to build a very high performance multi-media controller incorporating SCSI, ESDI, SMD, ST-506, QIC 24, and FLOPPY disk interfaces. The RAM based MICROSEQUENCER permits the user to build a mass storage controller that conforms with any currently available data format.

The addition of an SMC MSD95C00 SCSI CONTROLLER will provide a tightly coupled 2-chip set for high speed, high performance SCSI and "Embedded SCSI" applications with minimum component count and synchronous SCSI speeds of up to 5 megabytes per second.

Combining the MSD95C01 with the SMC MSD95C10 MICRO CHANNEL INTERFACE DEVICE will result in a highly integrated ESDI disk interface for the IBM Micro Channel Bus. The chip set may be used for adapter boards as well as PS/2 motherboard applications.

The SMC MSD95C15 IBM AT INTERFACE DEVICE can be used with the MSD95C01 DISK CONTROLLER to build an IBM AT hard disk interface for MFM, RLL and ESDI drives.

T-52-33-63

# **TABLE OF CONTENTS**

|                                                          | \GE |

|----------------------------------------------------------|-----|

| APPLICATIONS SUPPORTED                                   |     |

| FEATURES                                                 | . 1 |

| PIN CONFIGURATION                                        |     |

| GENERAL DESCRIPTION                                      | 1   |

| DESCRIPTION OF PIN FUNCTIONS                             |     |

| SYSTEM DESCRIPTION                                       | . 6 |

| LOCAL MICROPROCESSOR INTERFACE                           | . 6 |

| RAM BUFFER INTERFACE                                     |     |

| DISK DRIVE INTERFACE                                     |     |

| HOST BUS INTERFACE                                       |     |

| FUNCTIONAL DESCRIPTION                                   |     |

| DMA CONTROLLER                                           |     |

| MICROSEQUENCER                                           | 10  |

| Description of Individual Fields                         |     |

| Sequence Control Field                                   |     |

| Address Field                                            |     |

| Test Conditions Field                                    |     |

| Register Pointer Field                                   |     |

| Pointer Decrement Field                                  |     |

| Count Field                                              |     |

| Out Field                                                |     |

| Ext Field                                                | .14 |

| DISK INTERFACE & ENCODER/DECODER BLOCK                   |     |

| Programmable Polynomial Error Correction Code (MSD95C01) |     |

| Extended Reed Solomon Error Correction Block (MSD95C02)  |     |

| Fundamentals of Reed Solomon ECC                         |     |

| Case Examples                                            |     |

| CRC Addition Field                                       |     |

| ECC Extension Field                                      |     |

| LOCAL PROCESSOR INTERFACE                                |     |

| Overview of MSD95C01/02 Registers                        |     |

| Register Descriptions                                    |     |

| Reset Register                                           |     |

| DMA Control (Mode 1)                                     |     |

| Disk Interface and Encoder/Decoder Control (Modes 2-3)   |     |

| ECC Interface Control (Mode 4 Register)                  | .21 |

| Sync Register (8- or 16-bit Compares)                    | .21 |

| Tape Byte Counter Control Registers                      | .21 |

| Local Processor Control Registers                        | .22 |

| Interrupt Enable Registers                               | .22 |

| DMA Function Registers                                   | .23 |

| Status Registers                                         | .24 |

| Feedback Tap/Size Register                               | .26 |

| OPERATIONAL DESCRIPTION                                  | .27 |

| MAXIMUM GUARANTEED RATINGS                               | .27 |

| DC CHARACTERISTICS                                       | .27 |

| AC CHARACTERISTICS                                       | .27 |

| DESC | RIPT | ION. | OF | PIN | FUI | NCTIONS  |

|------|------|------|----|-----|-----|----------|

|      |      | 1011 | ~  |     |     | 10110110 |

| PIN NO.    | NAME                                        | SYMBOL                   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|---------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u> </u>   | FFER INTERF                                 | k- <u></u>               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 53-60      | Data Bus                                    | DB7-0                    | Input/Output. Bi-directional data bus to the external ring buffer RAM. This bus is automatically put into a high impedance state during valid External Device DMA cycles.                                                                                                                                                                                                                                                                                                            |

| 61-68, 1-8 | Address Bus                                 | A0-A15                   | Output. These signals are used to address the external ring buffer RAM.                                                                                                                                                                                                                                                                                                                                                                                                              |

| 50         | Output<br>Enable                            | ŌĒ                       | Output. This active low signal strobes the ring buffer RAM's data bus output drivers.                                                                                                                                                                                                                                                                                                                                                                                                |

| 51         | Write Enable                                | WE                       | Output. This active low signal strobes write data from the data bus into the ring buffer RAM.                                                                                                                                                                                                                                                                                                                                                                                        |

| 49         | DMA Clock                                   | DMACLK                   | Input. This 20 MHz (maximum) signal is used by the MSD95C01/02 to generate DMA cycles.                                                                                                                                                                                                                                                                                                                                                                                               |

| 43         | DMA<br>Request                              | DREQ                     | Input. This signal is driven active low by an External Device to request a DMA cycle.                                                                                                                                                                                                                                                                                                                                                                                                |

| 44         | DMA<br>Acknowledge                          | DACK                     | Output. This signal is driven active low by the MSD95C01/02 in response to DREQ. During data transfer from the ring buffer to the External Device, the rising edge of this signal is used to strobe data into the External Device. During data transfer from the external device to the ring buffer, a low will enable data transfer from the External Device.                                                                                                                       |

| 45<br>46   | Control 5<br>Control 6                      | CTL5 (ST1)<br>CTL6 (ST0) | Output. Depending on the programming of the MODE 1 Register, these bits can either reflect the data written to bits 4 and 5 of the Local Processor Output Register or they can be outputs that indicate the type MSD95C01/02 DMA controller cycle in progress:  ST1 ST0 CYCLE                                                                                                                                                                                                        |

|            |                                             |                          | 0 0 EXTERNAL DEVICE<br>0 1 LOCAL PROCESSOR<br>1 0 MICROSEQUENCER (DISK)<br>1 1 RESERVED                                                                                                                                                                                                                                                                                                                                                                                              |

| 47         | Control 7                                   | CTL7<br>(WRITE)          | Output. Depending on the programming of the MODE 1 Register, this bit can either reflect the data written to bit 6 of the Local Processor Output Register or this bit can be an output signal indicating to the ring buffer that a WRITE or READ cycle to or from the ring buffer is about to start. This output is low during a write cycle and high during a read cycle. CTL 7, 6, and 5, when programmed as WRITE, ST0, ST1, can be used for interfacing to an external ECC chip. |

| 48         | Control 8                                   | CTL8<br>(DGATE)          | Output. Depending on the programming of the MODE 1 Register, this bit can reflect the data written to bit 7 of the Local Processor Output Register. It may also be used as an output of the MICROSEQUENCER to be used as a "data valid" signal to indicate when data is being transferred on the DB7-0 bus for interface with an external ECC chip.                                                                                                                                  |

| DRIVE IN   | TERFACE                                     |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

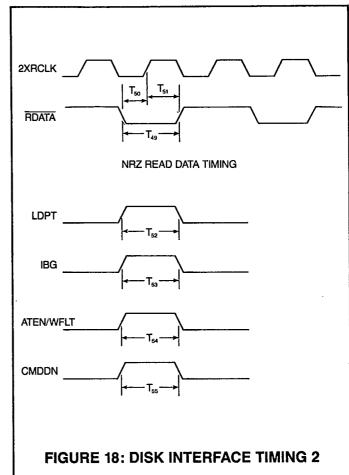

| 30         | Read Data                                   | RDATA                    | Input. This signal is the serial, active low data from the disk or tape drive. It may be encoded as RLL2, 7, MFM, FM, GCR, or NRZ as selected in MODE 2 Register bits 2-0.                                                                                                                                                                                                                                                                                                           |

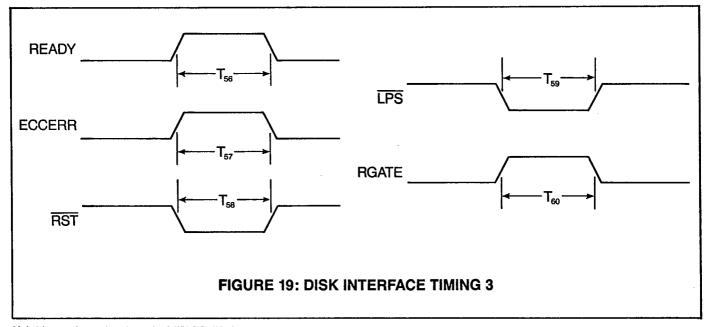

| 41         | Read Gate                                   | RGATE                    | Output. This signal is typically used to enable the data separator to begin locking to data. Normally, it becomes active during the PLO sync field. This signal is controllable via microcode to allow specific read data search algorithms and conformance to unique drive formats.                                                                                                                                                                                                 |

| 42         | Read Clock<br>(Read/<br>Reference<br>Clock) | RCLK                     | Input. This clock is used to frame the encoded RDATA bit stream from the drive. For NRZ input data, the Read/Reference Clock signal provides the timing necessary to synchronize the serial data transfer between the drive and the MSD95C01/02. RCLK is divided internal to the MSD95C01/02 and is used to run the MICROSEQUENCER. It is therefore necessary to provide a glitch-free clock into this input when the microprocessor is in operation.                                |

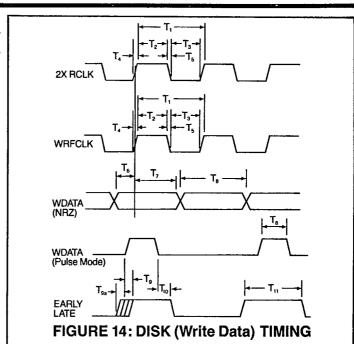

| 33         | Write Data                                  | WDATA                    | Output. This signal is the serial NRZ, FM, MFM, GCR or RLL data being written to the drive.                                                                                                                                                                                                                                                                                                                                                                                          |

| 39         | Write Gate                                  | WGATE                    | Output. This signal is controlled by the microsequencer and is active when the MSD95C01/02 is writing data to the drive.                                                                                                                                                                                                                                                                                                                                                             |

## **DESCRIPTION OF PIN FUNCTIONS (CONTINUED)**

T-52-33-63

| PIN NO.        | NAME                                            | SYMBOL              | DESCRIPTION                                                                                                                                                                                                                                                                                                                           |

|----------------|-------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRIVE IN       | TERFACE (CO                                     | NTINUED)            |                                                                                                                                                                                                                                                                                                                                       |

| 31             | Control 1                                       | CTL1<br>(EARLY)     | Output. Depending on the programming of the MODE 3 Register, this bit either reflects the data written to bit 0 of the Local Processor Output Register or indicates that the current disk Write Data bit should be externally precompensated early.                                                                                   |

| 32             | Control 2                                       | CTL2<br>(LATE)      | Output. Depending on the programming of the MODE 3 Register, this bit either reflects the data written to bit 1 of the Local Processor Output Register or indicates that the current disk Write Data bit should be externally precompensated late.                                                                                    |

| 40             | Control 3                                       | CTL3<br>(WRFCLK)    | Input/Output. Depending on the programming of the MODE 3 Register, this bit either reflects the data written to bit 2 of the Local Processor Output Register or acts as a tape write reference clock input. In tape applications that require read after write capability, this pin must be programmed as an input (WRFCLK).          |

| 38             | Control 4                                       | CTL4<br>(AMEN)      | Output. Depending on the programming of the MODE 2 Register, this bit either reflects the data written to bit 3 of the Local Processor Output Register or acts as a MICROSEQUENCER output which may be used to write an Address Mark (WGATE active) or search for an address mark (WGATE, RGATE inactive) in ESDI drive applications. |

| 19             | Sense<br>Input 4                                | SNS4<br>(READY)     | Input. The MSD95C01/02 can be programmed to generate a high-to-low level change interrupt from this pin. This input may be used to sense READY status from the drive.                                                                                                                                                                 |

| 20             | Sense<br>Input 3                                | SNS3<br>(CMDDN)     | Input. The MSD95C01/02 can be programmed to generate a high-to-low level change interrupt from this pin. This input may be used to indicate a Command Complete status when using ESDI drives.                                                                                                                                         |

| 21             | Sense<br>Input 2                                | SNS2<br>(ATTN/WFLT) | Input. The MSD95C01/02 can be programmed to generate a high-to-low level change interrupt from this pin. This input may be used to sense ATTENTION status from an ESDI drive or a WRITE FAULT status from an ST-506 drive.                                                                                                            |

| 22             | Sense<br>Input 1                                | SNS1<br>(LDPT)      | Input. The MSD95C01/02 can be programmed to generate any level change interrupt from this pin. This input may be used to sense load point status for tape applications.                                                                                                                                                               |

| 37             | Test Input 4                                    | TST4<br>(INDEX)     | Input. This edge-triggered signal is used by the MICROSEQUENCER for conditional branching. Typically, the INDEX pulse from the drive is connected to this pin.                                                                                                                                                                        |

| 36             | Test Input 3                                    | TST3<br>(ECCERR)    | Input. This level-triggered signal is used by the MICROSEQUENCER for conditional branching. When used with an external ECC chip, this input may be used to indicate an ECC error.                                                                                                                                                     |

| 35             | Test Input 2                                    | TST2<br>(IBG)       | Input. This level-triggered signal is used by the MICROSEQUENCER for conditional branching. An external signal indicating interblock gap for tape applications may be connected to this pin, but if it is not connected, then this pin must be grounded in tape applications.                                                         |

| 34             | Test Input 1                                    | TST1<br>(AMFND)     | Input. This edge-triggered signal is used by the MICROSEQUENCER for conditional branching. Typically, an ESDI address mark found signal is connected to this pin.                                                                                                                                                                     |

| PROCES         | SOR INTERFA                                     | CE                  |                                                                                                                                                                                                                                                                                                                                       |

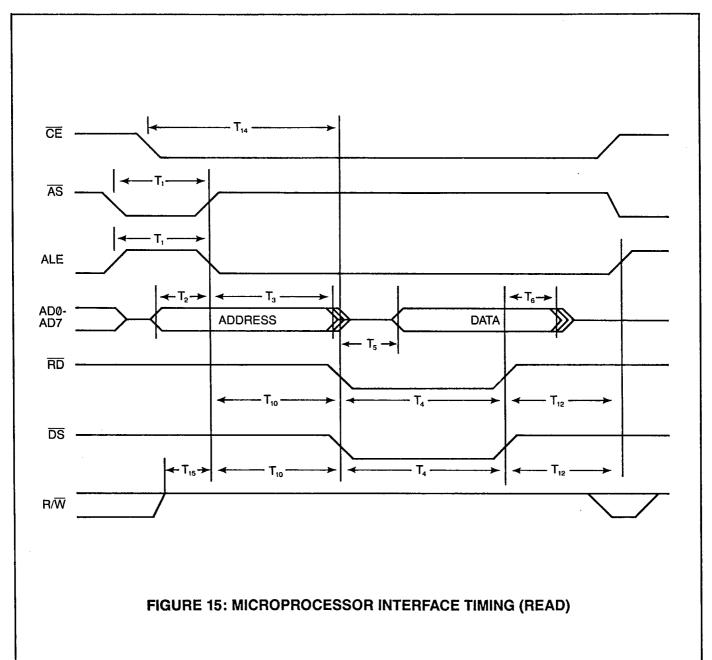

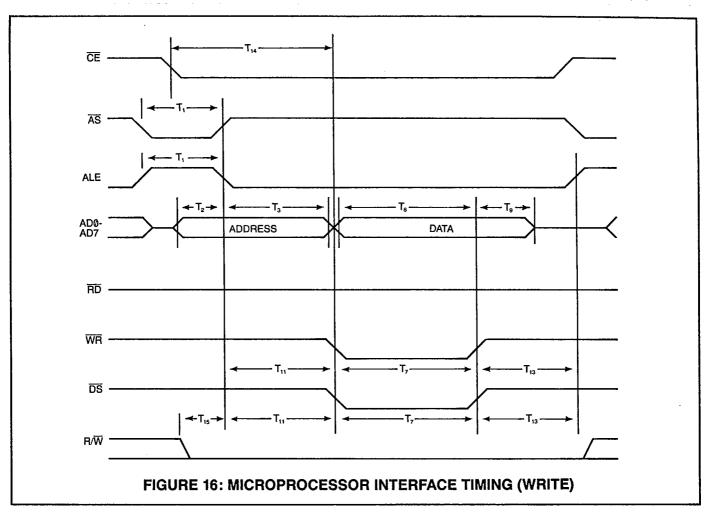

| 9-12,<br>14-17 | Address/<br>Data Bus                            | AD7-0               | Input/Output. Multiplexed bi-directional address/data bus to local processor.                                                                                                                                                                                                                                                         |

| 27             | Address<br>Latch Enable<br>(Address<br>Strobe). | ALE (ĀS)            | Input. This signal is active when an address is valid on the AD7-0 bus. The local processor reads the MSD95C01/02 RESET Register address either following a hard or prior to a soft reset to automatically configure the MSD95C01/02 to expect ALE or AS at this input.                                                               |

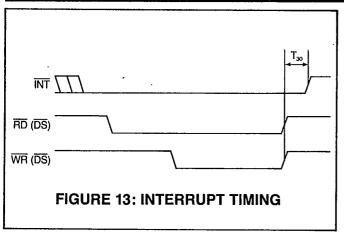

| 29             | Interrupt                                       | INT                 | Output. This open collector signal is driven low when the MSD95C01/02 detects an enabled interrupt.                                                                                                                                                                                                                                   |

| 26             | Read Strobe<br>(Data<br>Strobe)                 | RD (DS)             | Output. When the MSD95C01/02 is configured for ALE, this active low strobe is used to enable read data from the MSD95C01/02 onto the AD7-0 bus. When the MSD95C01/02 is configured for AS, this active low signal is used to strobe data into or out of the MSD95C01/02.                                                              |

#### **DESCRIPTION OF PIN FUNCTIONS (CONTINUED)**

T-52-33-63

| PIN NO. | NAME                         | SYMBOL      | DESCRIPTION                                                                                                                                                                                                                                              |

|---------|------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROCES  | SOR INTERFA                  | CE (CONTINU | JED)                                                                                                                                                                                                                                                     |

| 25      | Write Strobe<br>(Read/Write) | WR (R/W)    | Input. When the MSD95C01/02 is configured for ALE, this active low strobe is used to latch write data from the AD7-0 bus into the MSD95C01/02. When the MSD95C01/02 is configured for AS, the R/W input is used to qualify DS for a read or write cycle. |

| 24      | Chip Enable                  | CE          | Input. This input signal is used to qualify the RD and WR strobes for all accesses on the AD7-0 bus. This signal must be valid throughout the memory cycle.                                                                                              |

| 28      | Low Power<br>Standby         | LPS         | Input. A low level applied to this pin signifies that the system is requesting the low power standby mode. This pin should be tied to a logic "1" for normal operation.                                                                                  |

| 23      | Reset                        | RST         | Input. A low level applied to this pin will cause the MSD95C01/02 to be reset to a known state.                                                                                                                                                          |

| 18      | Power<br>Supply              | VCC         | +5V Power Supply pin.                                                                                                                                                                                                                                    |

| 13      | Ground 1                     | GND1        | Ground pin.                                                                                                                                                                                                                                              |

| 52      | Ground 2                     | GND2        | Ground pin.                                                                                                                                                                                                                                              |

#### SYSTEM DESCRIPTION

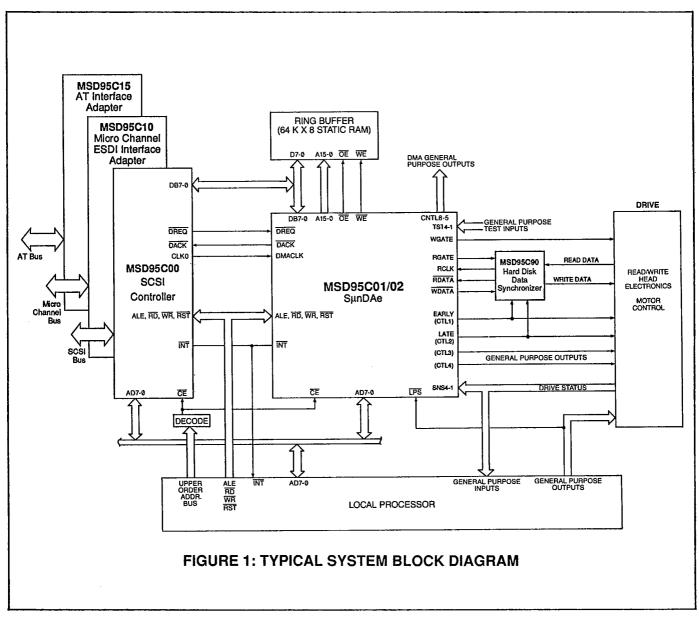

A typical MDS95C01/02 based system consists of a LOCAL MICROPROCESSOR to control low speed tasks, a RAM BUFFER to store data to and from the disk media, a DISK INTERFACE section which may include a data separator, and a HOST BUS INTERFACE unit which connects the MSD95C01/02 to advanced system buses such as the SCSI bus, the Microchannel bus or IBM AT bus.

As can be seen in the system block diagram, the interface to the external static RAM BUFFER requires no added circuitry. A major advantage of an MSD94C01/02 based system is the use of two external data buses; one to permit data flow between the RING BUFFER and the HOST BUS INTERFACE unit (e.g. SCSI, MCA, IBM AT, etc) and the other to permit the local processor to access both the MSD95C01/02 and the HOST BUS INTERFACE unit. The two data buses allow for uninterrupted data flow in and out of the RING BUFFER during local processor updates to the DISK CONTROLLER and BUS INTERFACE devices.

#### **LOCAL MICROPROCESSOR INTERFACE**

The MSD95C01/02 is optimized to work with a microprocessor or a microcontroller having a multiplexed

address/data bus without the need for any external glue logic. The main function of the local microprocessor is to interpret high level commands coming from the HOST BUS and convert them into proper instructions to the MSD95C01/02. Additionally, the local microprocessor will download micro-routines into the disk controller and handle the low speed control functions of the disk drive through the use of general purpose input and output lines.

#### **RAM BUFFER INTERFACE**

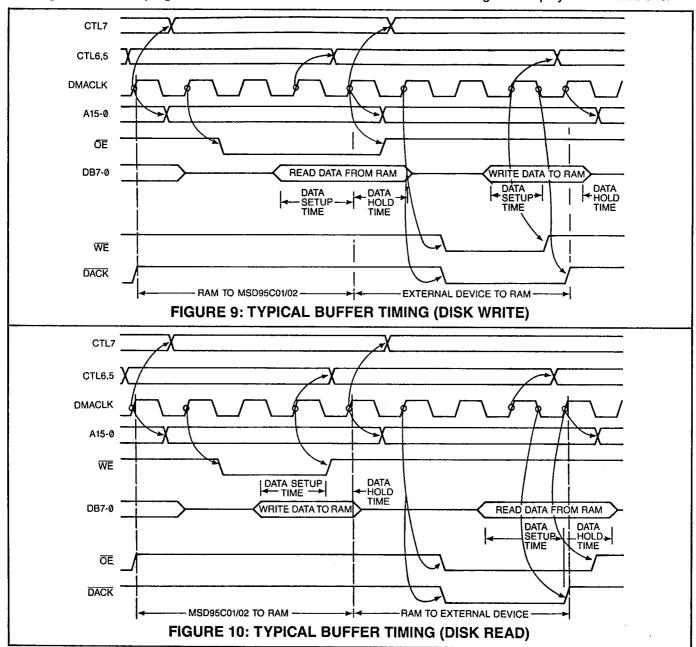

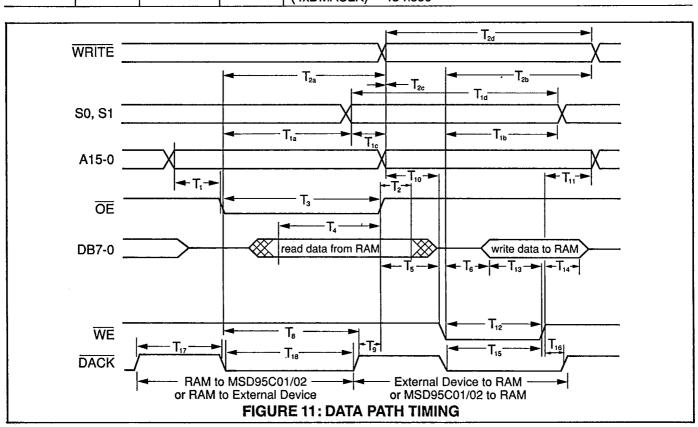

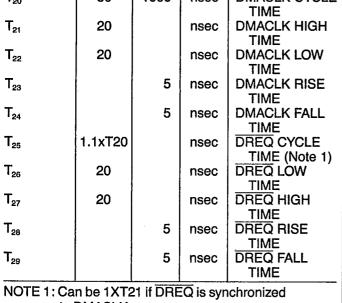

The interface to the RAM RING BUFFER is through the use of the triple DMA controller of the MSD95C01/02. The microsequencer of the MSD95C01/02 uses the RING BUFFER to store data going to and from the disk media. DMA transfers to and from the HOST bus are supported to transfer data from the RING BUFFER. Additionally, the local microprocessor has access to the RING BUFFER as well. The DMA controller section of the MSD95C01/02 controls and arbitrates up to 64K of external RING BUFFER built with standard static RAMs. The buffer size can be easily extended with the addition of a few gates. Disk data transfers to and from the buffer are managed by the MSD95C01/02 without the need for processor intervention. A DMA

Request/Acknowledge handshake is used to control HOST BUS (e.g. SCSI, MCA, etc) accesses to the RING BUFFER which are completely asynchronous with respect to disk and local processor transfers.

33E D

This method of local buffer access combined with a powerful programmable ECC (MSD95C01) or Extended Reed Solomon ECC (MSD95C02) and CRC extension designed to virtually eliminate miscorrections, provides the user with on-the-fly error correction capability with no loss of disk revolutions.

#### DISK INTERFACE

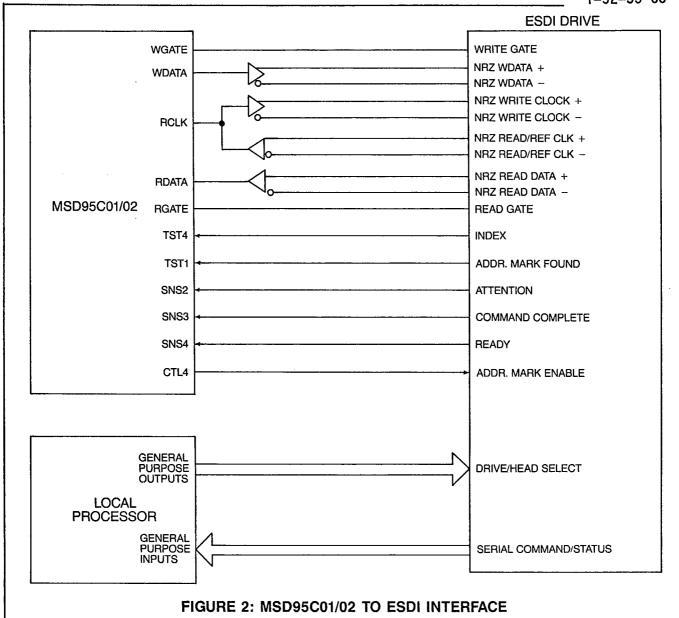

Interface to an ESDI type disk drive is accomplished with the use of a few driver/receiver components (see figure 2). When interfacing to an MFM or RLL type of drive, the MSD95C90 DISK INTERFACE UNIT may be used to provide data separation and pre-compensation functions. The MSD94C01/02 contain several general purpose input/output pins to control and monitor external events. In addition, there are four general purpose test inputs and four latched sense inputs that may be used directly by the microsequencer to perform conditional jumps. The sense inputs, test inputs, and the control outputs are used to efficiently handle ESDI drives.

#### **HOST BUS INTERFACE**

An assortment of HOST BUS INTERFACE circuits are provided by Standard Microsystems that interface the MSD95C01/02 to a variety of system buses. These include the MSD95C00 SCSI CONTROLLER for embedded SCSI applications, the MSD95C10 MIDAS device for Micro Channel applications and the MSD95C15 AT INTERFACE UNIT for interface to the IBM AT bus for both adapter and motherboard applications. Please refer to the appropriate data sheets for detailed information.

#### **FUNCTIONAL DESCRIPTION**

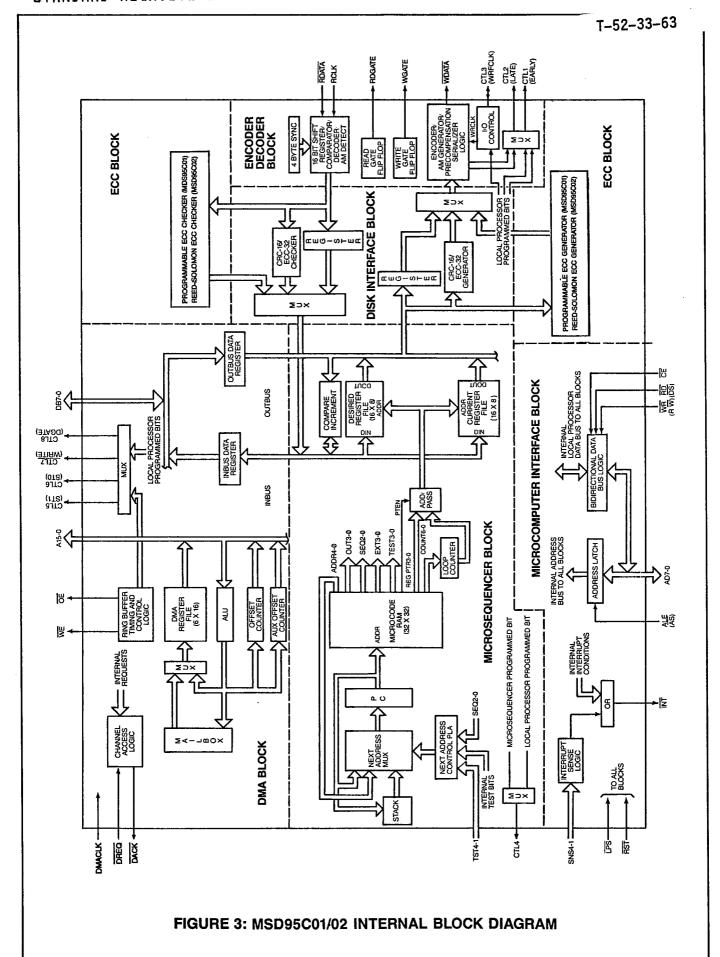

Figure 3 shows the internal block diagram of the MŠD95C01/02. The data flow through the chip occurs on the INBUS and the OUTBUS. The OUTBUS connects all data coming from the ring buffer to the drive and the INBUS connects all data from the drive to the ring buffer. The blocks which make up the MSD95C01/02 are described as follows:

#### DMA CONTROLLER

As shown in Figure 4, the three channel DMA controller is composed of a 6 X 16 bit register file, two OFFSET COUNTERS for monitoring ring buffer full/empty status, a DMA FUNCTION Register to indirectly address the register file, a ring buffer DATA Register, and ALU to perform incrementing (by 1, 2, 3 or 4) and in addition, a 16 bit mailbox register, state controller and DMA request priority resolver.

Channel access to the ring buffer comes from three sources. The MICROSEQUENCER requests are initiated by the DISK INTERFACE block for every byte transferred to/from the MICROSEQUENCER and is given top priority. Local processor accesses to the ring buffer are initiated by direct operation of the local processor on the addressable registers within the DMA controller. The local processor is given second priority. External Device access (like SCSI) is initiated via a DMA request-acknowledge handshake and is given third priority.

#### **ALU and Register function:**

For each DMA channel, specific register manipulations are In order to specify one of many housekeeping calculations, disk read operations, the channel must ensure that the addressable DMA FUNCTION Register). The bit definitions

starting address for a sector transfer is not updated until the data transferred into the ring buffer is known to be error free. The External Device, during a read operation from the ring buffer, must cause the address to be incremented for each byte transferred. It must also update the OFFSET COUNTER since there is a relationship between the value in the OFFSET COUNTER and the amount of available free space there is in the buffer and available error free data there is to transfer out on the External channel. The local processor channel might be required to perform read modify write routines during error correction operations.

Local Processor channel operation:

The local Processor can specify the address operation to be performed during its channel access via the DMA FUNCTION Register which is a write only local processor addressed register (assigned address 50HEX). This function register permits the loading of all registers in the register file which are not directly addressable from the external local processor.

The Local Processor can directly access four registers in the DMA controller. They are:

DMA FUNCTION Register (write only) address 50H MAILBOX HIGH Register (read/write) address 51H MAILBOX LOW Register (read/write) address 52H DATA Register (read/write) address 53H

The local processor can indirectly access 6 additional 16 bit registers that make up the DMA register file. These registers are accessed by using the DMA FUNCTION Register. An example of their use is illustrated as follows:

CONSTANT 1—Normally used to hold the sector size and in calculating address updates and ring buffer status flags.

CONSTANT 2—Normally used to hold a number that is a function of the Ring Buffer size for generating Ring Buffer empty/full status.

LOCAL PROCESSOR ADDRESS Register—Holds the current address of a local processor to ring buffer data transfer.

EXTERNAL DEVICE ADDRESS Register—Holds the current address of an External Device to ring buffer data transfer.

DISK Register—Maintains the address of the first location of a MICROSEQUENCER initiated disk transfer until data integrity is established.

DISK ADDRESS Register—Holds the current address of a MICROSEQUENCER initiated disk ring buffer data transfer.

DMA FUNCTION Register-Refer to Table 9 for details.

#### Disk Channel Access Operation:

Disk requests for data transfer are initiated by the MSD95C01/02's internal MICROSEQUENCER. For normal data transfer between the disk and the ring buffer, the MICROSEQUENCER causes the DISK ADDRESS in the DMA block to be incremented by one between ring buffer access cycles.

In addition, the MICROSEQUENCER may perform some housekeeping functions at each sector boundary if required. These housekeeping functions may include updating the OFFSET COUNTER, determining buffer full/empty status, etc.

possible depending upon the operation required. Each the MSD95C01/02's internal MICROSEQUENCER has the channel will have different requirements on the way the ability to specify the operation by loading a DISK DMA address to the ring buffer is updated. For instance, during FUNCTION Register (different from the local processor

33E D

of this register are identical to the DMA FUNCTION Register as defined in Tables 1 and 2. The MICROSEQUENCER can load the DISK DMA FUNCTION Register by transferring a value previously stored in the DESIRED RÉGISTER FILE to the DMA block.

#### EXTERNAL DEVICE CHANNEL ACCESS OPERATION:

Upon an external DMA request, this channel will perform one hardwired function consisting of proper adjustment of the current ring buffer address as well as decrementing the OFFSET COUNTERs for current handling of ring buffer full/ empty situations. The MSD95C01/02 can buffer a maximum of 12 DMA requests before issuing an acknowledgment without causing an overrun/underrun condition. The MSD95C01/02 uses the leading edge of DMA Request to post the EXTERNAL channel access. This permits the MSD95C01/02 to work with several REQ-ACK timing situations.

For External Device DMA operations, the DMA hardwired function performed is:

EXTERNAL DEVICE ADDRESS + N → EXTERNAL DEVICE ADDRESS.

N is used to permit various data bus widths between the ring buffer and the External Device as shown in table 1.

| N | DATA BUS WIDTH |

|---|----------------|

| 1 | 8 BITS         |

| 2 | 16 BITS        |

| 3 | 24 BITS        |

| 4 | 32 BITS        |

TABLE 1: EXTERNAL DEVICE BUS WIDTHS AS A **FUNCTION OF N**

The value N is programmed by the Local Processor in MODE 1 Register, bits 5 and 4.

**OFFSET COUNTER:**

The OFFSET COUNTER is part of the automatic

housekeeping function of the DMA block and is used to keep track of buffer empty/full conditions.

During External Device to Ring Buffer to disk operations (WRITE the disk), the OFFSET COUNTER keeps track of the number of free bytes left in the buffer. Whenever the Ring Buffer size minus the OFFSET COUNTER is less than the sector size (indicating that there is less than a sector's worth of data in the ring buffer), the disk WRITE is temporarily held off. The throttling of the Disk DMA channel as a function of buffer space status is done automatically by the DMA controller without local processor intervention.

During Disk to Ring Buffer to External Device (READ the disk) operations, the OFFSET COUNTER keeps track of the total data bytes left in the buffer. Whenever the Ring Buffer size minus the OFFSET COUNTER is less than the sector size (indicating that there is not enough room in the buffer to accept another sector), the disk READ is temporarily held off. The throttling of the Disk DMA channel as a function of buffer space status is done automatically by the DMA controller without local processor intervention.

Decisions by the MICROSEQUENCER regarding buffer empty/full status are made by interrogating the ZOFF flag whenever an ALU operation loads a zero into the OFFSET COUNTER.

#### AUXILIARY OFFSET COUNTER operation:

The AUXILIARY OFFSET COUNTER is loaded and modified along with the OFFSET COUNTER. It is required because data transferred from the disk into the Ring Buffer might contain errors. Because of this, the AUXILIARY OFFSET COUNTER might be different from the OFFSET COUNTER and is used to control the flow of data between the External Device and the Ring Buffer. During External Device to Ring Buffer transfers, the AUXILIARY OFFSET COUNTER keeps track of the number of free bytes left in the buffer. During Ring Buffer to External Device transfers, the AUXILIARY OFFSET COUNTER keeps track of the number of error free data bytes left in the buffer.

The OFFSET and AUXILIARY OFFSET COUNTERS are linked together until an error is detected on data read from the disk. When this occurs, only the OFFSET COUNTER is incremented as new data is transferred from the disk to the Ring Buffer. The AUXILIARY OFFSET COUNTER is not incremented until the error is corrected. Both counters are decremented when data is transferred from the Ring Buffer to the External Device. If the error is corrected before the AUXILIARY OFFSET COUNTER is decremented to zero, then the two counters are linked back together by transferring the contents of the OFFSET COUNTER into the AUXILIARY OFFSET COUNTER in response to a DMA FUNCTION Register command. If the AUXILIARY OFFSET COUNTER is decremented to zero before the error is corrected, the MSD95C01/02 will not respond to DMA requests from the external device until the AUXILIARY OFFSET COUNTER and OFFSET COUNTER are linked back together. See Appendix 4 for a further description of the OFFSET and AUXILIARY OFFSET COUNTERs during error correction on the fly.

And a superior of the superior

#### Status Flags:

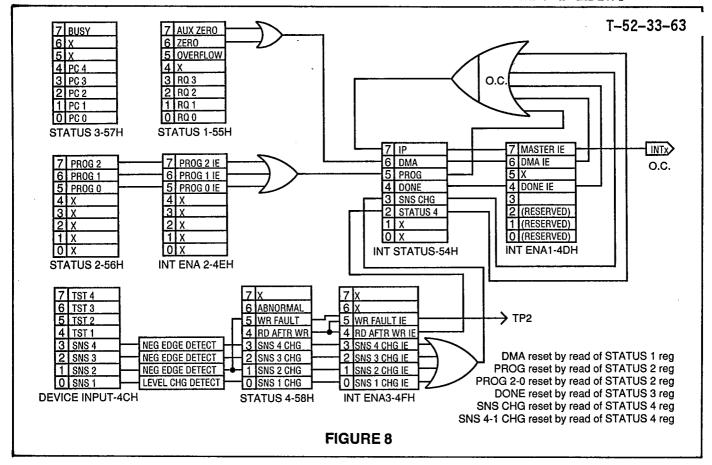

The DMA block will generate three status flags which can be used by the MICROSEQUENCER to test and make decisions on the microprogram flow. These three status flags, defined as follows, are also readable by the Local Processor in STATUS 1 Register (ADDR 55H):

OVERFLOW: During a DMA housekeeping cycle, this flag indicates the result of the current operation performed by the ALU; if the arithmetic yields an overflow, this bit will be set. This flag is latched during a DMA housekeeping cycle and will continue to indicate the result of the operation until the next housekeeping cycle latches a new OVERFLOW status. This bit is available to the Local Processor in STATUS 1 Register, bit D5.

ZERO: This flag is set to a one when the OFFSET COUNTER is decremented to zero. This bit is available to the Local Processor in STATUS 1 Register, bit D6.

AUX ZERO: This flag is set to a one when the AUXILIARY OFFSET COUNTER is decremented to zero. This bit is available to the Local Processor in STATUS 1 Register, bit D7.

The ZERO and AUX ZERO flags are not set if the OFFSET and AUXILIARY OFFSET COUNTERS are loaded with a zero.

The MICROSEQUENCER can interrogate the logical OR of the ZERO and AUX ZERO flags via the test input ZOFF. ECC ON THE FLY:

The three channel DMA arrangement provides the user with the ability to perform error correction on the fly without loss of a disk revolution. In general, upon disk read operations, one sector may be transferred from the Ring Buffer over the EXTERNAL channel, one sector may be operated on by the Local processor for error correction, and the third sector may be read from the disk and written into the Ring Buffer. Refer to Appendix 4 for further description of ECC on the fly.

#### **MICROSEQUENCER**

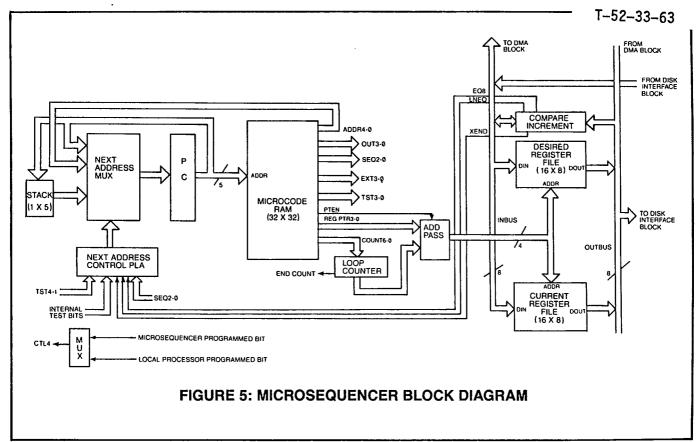

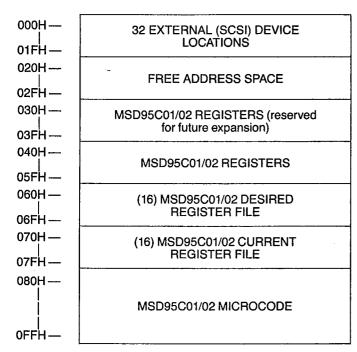

As shown in Figure 5, the MICROSEQUENCER consists of a 32 X 32 microcode RAM, a 7 bit loop counter, a one address STACK, a sophisticated next address generator and two 16 byte register files. During next address generation, the Program Counter can be loaded from the STACK, from the ADDRESS FIELD output by the microcode RAM (ADDR 4-0), or from the current or incremented value in the Program Counter.

The Local Processor can initiate Command execution (eg.

a Read Command) by writing to the COMMAND START Register (ADDR 54 HEX). The MSD95C01/02 will then begin execution at address zero in the microcode RAM. From this time until the command terminates, program flow is dependent on which of the several sources are specified when the Program Counter is loaded. Selection of the next address is dependent on the Sequence control field (SEQ 2-0), and internal and external test points which are input to the Next Address Control PLA. Test points are chosen via the Test field (TEST 3-0) for interrogation and program flow of the MICROSEQUENCER.

Contained within the MICROSEQUENCER block are two, 16 byte register files named DESIRED and CURRENT REGISTER FILEs. In general, the MICROSEQUENCER reads the DESIRED REGISTER FILE and writes the CURRENT REGISTER FILE. The Local Processor can read or write either register file. Local Processor access to these register files are restricted and controlled by interrupts generated by the MICROSEQUENCER to the Local Processor. This limited access is required to resolve the access contentions to these register files by both the Local Processor and the MICROSEQUENCER.

In addition to the DESIRED and CURRENT REGISTER FILEs, there is a comparator structure set up to compare contents in the two register files as shown in Figure 8. Any information loaded by the local processor in the DESIRED REGISTER FILE may be compared with the data that is deposited in the CURRENT REGISTER FILE as it is filled with data read from the disk. The sequence and number of compares made are all initiated under MICROSEQUENCER control. Typically, the compares can be performed to determine whether a particular ID field had been encountered.

The contents of any DESIRED REGISTER FILE location can be incremented under MICROSEQUENCER control. Typically, this can be used to increment the sector number in the DESIRED REGISTER FILE location when performing consecutive logical sector operations.

In addition, the CURRENT REGISTER FILE can, under MICROSEQUENCER control, be loaded with the error syndrome bytes for examination by the Local Processor during an error correction operation.

In typical applications, the CURRENT REGISTER FILE holds data such as the current header information (head #, sector #, track #) and the writing to these registers is controlled by the MICROSEQUENCER as data is converted from serial to parallel in the DISK INTERFACE block. The DESIRED REGISTER FILE holds information such as the desired sector to be operated on in a READ or WRITE DISK operation. The desired header information, in this case is written into the DESIRED REGISTER FILE by the Local Processor prior to the execution of the READ OR WRITE command in an order that is consistent with the order in which the MICROSEQUENCER loads and compares the CURRENT REGISTER FILE.

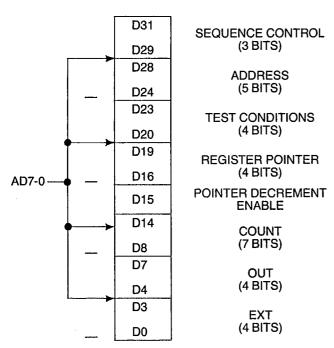

The 32 bit microprogram word definition contains a total of 8 separate fields as shown in Figure 6.

#### **Description of Individual Fields:**

Sequence Control Field (D31-29):

The SEQUENCE CONTROL FIELD determines the next address loaded into the PROGRAM COUNTER which feeds the MICROSEQUENCER RAM. Depending upon which SEQUENCE CONTROL FIELD is specified, the next address might remain at the current address, increment, use the value stored in the STACK, or use the value specified in

FIGURE 6: 32 BIT MICROSEQUENCER PROGRAM WORD DESCRIPTION

the ADDRESS FIELD. In addition, it can cause the current value in the PROGRAM COUNTER to be pushed on the STACK. The STACK is one address deep. The END COUNT and TEST POINT can affect the next address generation and STACK operations in a number of ways. See section on the TEST FIELD and COUNT FIELD for a description of the various conditions that will produce a valid TEST POINT or END COUNT.

#### Address Field (D28-24):

The Address Field bits in the microcode instruction may be directly loaded into the Program counter when executing "jump" and "call" instructions. When executing a call instruction, the current (or next) Program Counter value may be saved on a one address STACK. "Return" instructions can be implemented by loading the contents of the STACK back into the Program Counter. It should be noted that subroutines can only be nested one deep.

#### Test Conditions Field (D23-20):

The test condition field permits the MICROSEQUENCER to test one of 16 conditions for the purpose of conditional jumps and calls as specified in the SEQUENCE CONTROL FIELD. These 16 inputs originate in the MICROSEQUENCER block and other blocks and four of the test points are general purpose inputs from outside the MSD95C01/02 appearing on pins TST1-4.

## T-52-33-63

### **SEQUENCE CONTROL FIELD DEFINITION:**

| MNEMONIC                  | D31-29 | OPERATION       | TEST POINT<br>END COUNT | 1 1            | 1 0     | 0              | 0       |

|---------------------------|--------|-----------------|-------------------------|----------------|---------|----------------|---------|

| SHLP<br>(SHORT LOOP)      | 000    | PC =<br>STACK = |                         | PC+1<br>D28-24 | PC<br>— | PC+1           | PC<br>— |

| LGLP<br>(LONG LOOP)       | 001    | PC =<br>STACK = |                         | PC+1<br>D28-24 | PC<br>— | PC+1           | PC<br>— |

| RC<br>(RETURN OR CALL)    | 010    | PC =<br>STACK = |                         | STACK          | PC<br>— | D28-24<br>PC+1 | PC<br>— |

| CI<br>(CALL OR INCREMENT) | 011    | PC =<br>STACK = |                         | D28-24<br>PC+1 | PC<br>— | PC+1           | PC<br>— |

| TSJ<br>(TEST JUMP)        | 100    | PC =<br>STACK = |                         | PC+1           | PC+1    | D28-24         | PC<br>  |

| TSC<br>(TEST CALL)        | 101    | PC =<br>STACK = |                         | PC+1<br>—      | PC+1    | D28-24<br>PC+1 | PC<br>— |

| TSJL<br>(TEST JUMP LONG)  | 110    | PC =<br>STACK = |                         | PC+1           | PC+1    | D28-24         | PC<br>— |

| TSCL<br>(TEST CALL LONG)  | 111    | PC =<br>STACK = |                         | PC+1<br>—      | PC+1    | D28-24<br>PC+1 | PC<br>— |

D28-24 is the address as specifird in the ADDR field of the microcode word.

- = no change.

## TEST SIELD DESIMITION

|       | FIELD     | DEFIN            | ITION            |                              |                                                                                                                                                                                                                                                                                                                                                                                  |

|-------|-----------|------------------|------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D23   | D22       | D21              | D20              | TEST POINT<br>SELECTED       | DEFINITION                                                                                                                                                                                                                                                                                                                                                                       |

| 0     | 0         | 0                | 0                | FORCE ZERO                   | Forces the TEST input to a logic zero.                                                                                                                                                                                                                                                                                                                                           |

| 0     | 0         | 0                | 1                | DC GAP                       | From the ENCODER/DECODER block indicating that no transitions have occurred on the RDATA input pin for 15 clocks.                                                                                                                                                                                                                                                                |

| 0     | 0         | 1                | 0                | SYNC                         | From the DISK INTERFACE block indicating a 16 bit high speed compare between disk data and the MICROSEQUENCER selected SYNC Register(s). This signal is used to start all CRC and ECC generation logic.                                                                                                                                                                          |

| 0     | 0         | 1                | 1                | INTER*                       | From the DISK INTERFACE block indicating that a CRC-16, ECC-32, Programmable ECC (MSD95C01) or Reed Solomon ECC (MSD95C02) data error has occurred. In tape read after write mode, a one indicates a data error. Otherwise, a zero indicates a data error.                                                                                                                       |

| 0 0 0 | 1 1 1 1 1 | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | TST1<br>TST2<br>TST3<br>TST4 | Input pin TST1. Input pin TST2. Input pin TST3. Input pin TST4.                                                                                                                                                                                                                                                                                                                  |

| 1     | 0         | 0                | 0                | EQ                           | This input reflects the status of an 8 bit compare between the INBUS and the DESIRED REGISTER FILE.                                                                                                                                                                                                                                                                              |

| 1     | 0         | 0                | 1                | LNEQ                         | Indicates that one of the previous 8 bit compares or the current 8 bit compare is not equal.                                                                                                                                                                                                                                                                                     |

| 1     | 0         | 1                | 0                | XEND                         | Indicates that the contents of a DESIRED REGISTER FILE location has been incremented to all zeros.                                                                                                                                                                                                                                                                               |

| 1     | 0         | 1                | 1                | NTP2                         | This is an auxiliary test input which is the logical OR of four independent conditions. It is equal to either a HALT (local processor initiated via Register 54, bit 0), an ABNORMAL DATA MARK (Register 58H, bit 6), a WRITE FAULT (Register 58H, bit 5), or, in tape mode, if the sync was not found in read after write. A zero indicates that one of the conditions is true. |

| 1     | 1         | 0                | 0                | CMD                          | Originates in the DMA block and indicates if the command loaded by the local processor is a READ or WRITE Command with respect to the Disk. This operation tests bit 6 inverted in the START COMMAND Register. A one is a disk write and a zero is a disk read.                                                                                                                  |

| 1     | 1         | 0                | 1                | BFRDY                        | Originates from the DMA block. This test input is a logic one if the result of an ALU operation has not yielded an overflow and NTP2 is a logic one.                                                                                                                                                                                                                             |

| 1     | 1         | 1                | 0                | ZOFF                         | Originates from the DMA block and indicates when either the OFFSET or AUXILIARY OFFSET COUNTER is loaded with a zero as a result of an ALU operation.                                                                                                                                                                                                                            |

| 1     | 1         | 1                | 1                | ONE                          | Forces the TEST input to a logic ONE.                                                                                                                                                                                                                                                                                                                                            |

Register Pointer Field (D19-16): The REGISTER POINTER FIELD is associated with the DESIRED and CURRENT REGISTER FILES and specifies the addess of the particular register file location to be operated on. The DESIRED and CURRENT REGISTER FILEs have a common address such that the same corresponding location in each file may be operated on at the same time.

Pointer Decrement Field (D15):

This one bit field permits one to access sequentially decrementing locations in the DESIRED and CURRENT REGISTER FILEs for multiple operations within these

If the Pointer Decrement enable bit is zero, the Register Address will be the value specified in the Register Pointer field. If the Pointer Decrement enable bit is one, the Register Address will be the value specified in the Register Pointer field added to the current contents of the Loop Counter. When accessing sequential register file locations, the Count field should be initialized to the number of sequential access required and the REGISTER POINTER FIELD should be initialized to the last sequential register file location to be accessed. At each MICROSEQUENCER clock, the loop counter in the instruction is decremented, thus permitting sequential access at the MICROSEQUENCER clock frequency.

Count Field (D14-8):

This field serves two functions. First, it is loaded into the loop counter for counting microinstruction loops. In this instance, the generation of an END COUNT status bit, will cause branching conditions as defined by the SEQUENCE CONTROL FIELD (D31-29). The END COUNT status bit will be set to a logic one when the loop counter is decremented to zero. The second function of this field is for accessing sequential locations of the DESIRED and CURRENT REGISTER FILEs as described in the POINTER DECREMENT ENABLE FIELD.

It should be noted that the count value is loaded into the loop counter as the microinstruction containing it is exited.

The loop counter is decremented every microinstruction clock or every 128th microinstruction clock for a short loop (SHLP) or a long loop (LGLP) respectively. To perform a count of N, the value N-1 should be specified in the previous instruction in the microcode since the loop counter gets loaded as an instruction is exited.

#### Out Field (D7-4):

The out field is one of two control fields used to control internal and external operations during microprogram execution. This four bit field yields one of 16 control outputs

| D7-D4<br>0000<br>0001<br>0010 | OPERATION  No operation.  To DISK INTERFACE block causing the output CTL 4 to change. This output is multiplexed with a programmable output controlled by the local processor. This signal may be used for an external address mark enable when interfacing with ESDI drives.  To the DMA block. This signal is a DMA request from the MICROSEQUENCER and enables disk data to get transferred to the DATA Register in the DMA block over the INBUS. It also can cause the output DG (Data Gate) to go active. The DG output is multiplexed with a programmable output controlled by the local processor.                                                                 |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0010                          | To DISK INTERFACE block causing the output CTL 4 to change. This output is multiplexed with a programmable output controlled by the local processor. This signal may be used for an external address mark enable when interfacing with ESDI drives.  To the DMA block. This signal is a DMA request from the MICROSEQUENCER and enables disk data to get transferred to the DATA Register in the DMA block over the INBUS. It also can cause the output DG (Data Gate) to go active. The DG output is multiplexed with a programmable output controlled by the local processor.                                                                                           |

| 0010                          | multiplexed with a programmable output controlled by the local processor. This signal may be used for an external address mark enable when interfacing with ESDI drives.  To the DMA block. This signal is a DMA request from the MICROSEQUENCER and enables disk data to get transferred to the DATA Register in the DMA block over the INBUS. It also can cause the output DG (Data Gate) to go active. The DG output is multiplexed with a programmable output controlled by the local processor.                                                                                                                                                                      |

|                               | enables disk data to get transferred to the DATA Register in the DMA block over the INBUS. It also can cause the output DG (Data Gate) to go active. The DG output is multiplexed with a programmable output controlled by the local processor.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0011                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                               | This signal turns DGATE off.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0100                          | This signal allows the PLO SYNC (preamble) data stored in the DESIRED REGISTER FILE to be loaded into the ENCODER/DECODER/DISK INTERFACE block over the OUTBUS. In addition, during a write, it is used to preset all CRC and ECC generation logic.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0101                          | For disk drive application: This signal allows the missing clock data pattern stored in the DESIRED REGISTER FILE to be loaded into the ENCODER/DECODER/DISK INTERFACE block over the OUTBUS and generate the missing clock pattern when shifting the data out to the disk.  For tape application: This signal is used to write special marks in GCR code. To write out a block of "file mark" data (00101 00101), write FFH data with WMISS in out field. To write out a byte of "Data Mark" data (11111 00111), write out 5DH data with WMISS in out field.  In addition, during a write, WMISS is used to start all CRC and ECC generation logic and to activate CTL4. |

| 0110                          | This signal gates the data stored in the DESIRED REGISTER FILE on to the OUTBUS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0111                          | This signal gates the error syndrome (from the selected error checker) to the CURRENT REGISTER FILE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1000                          | This signal causes the contents of the DESIRED REGISTER FILE pointed to by the register pointer field to be loaded into the DISK DMA FUNCTION Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1001                          | This signal gates the check bytes (CRC-16, ECC-32, Programmable ECC (MSD95C01), or Reed Solomon ECC (MSD95C02) out to the disk.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1010                          | This signal enables the deleted data mark.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1011                          | RESERVED FOR FUTURE USE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1100                          | This signal sets bit 5 of STATUS 2 Register (ADDR 56H) and will, if enabled, generate an interrupt to the Local Processor. In addition, this interrupt will permit the Local Processor to access the CURRENT REGISTER FILE. It also separates the OFFSET and the AUXILIARY OFFSET COUNTERS. Typically, this interrupt is used for error correction operations. See description of STATUS 2 Register.                                                                                                                                                                                                                                                                      |

|                               | 0100<br>0101<br>0110<br>0111<br>1000<br>1001<br>1010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

**OUT FIELD DEFINITION (CONTINUED):**

| MNEMONIC | D7-D4 | OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PINT1    | 1101  | This signal sets bit 6 of STATUS 2 Register (ADDR 56H) and will, if enabled, generate an interrupt to the Local Processor. In addition, this interrupt will permit the Local Processor to access the CURRENT REGISTER FILE. Typically, this interrupt may be used to permit the Local Processor to read the current ID information that is stored in the CURRENT REGISTER FILE.                                                                                                                                                       |

| PINT2    | 1110  | This signal sets bit 7 of STATUS 2 Register (ADDR 56H) and will, if enabled, generate an interrupt to the Local Processor. This interrupt is general purpose and can be generated upon recognition of any MICROSEQUENCER detectable condition.                                                                                                                                                                                                                                                                                        |

| DNINT    | 1111  | This signal sets bit 4 of the INTERRUPT STATUS Register (ADDR 54H) and will, if enabled, generate an interrupt to the Local Processor. Typically, this signal is invoked to inform the Local Processor that the current command executed by the MICROSEQUENCER has been completed. Generation of this signal will stop the MICROSEQUENCER, reset BUSY (STATUS 3 Register, Bit D7), and set done (INTERRUPT STATUS Register, Bit D4). In addition, this interrupt will permit the Local Processor to access the CURRENT REGISTER FILE. |

#### EXT Field (D3-0):

The EXT field is one of two control fields used to control execution. This four bit field yields one of 16 control outputs internal and external operations during microprogram as follows:

#### **EXT FIELD DEFINITION:**

| EVI LIEFD DE |       |                                                                                                                                                                                                                                                                                                                                          |

|--------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MNEMONIC     | D3-D0 | OPERATION                                                                                                                                                                                                                                                                                                                                |

| NOOP         | 0000  | No operation.                                                                                                                                                                                                                                                                                                                            |

| SWDG         | 0001  | This signal posts a DMA request for the MICROSEQUENCER to the DMA block and is used during disk write operations. The signal allows data to be transferred from the DATA Register in the DMA block to the DISK INTERFACE and ENCODER/DECODER blocks. It also generates the DG (Data Gate) signal.                                        |

| SRCRC        | 0010  | This signal is used to inform the CRC-16 or ECC-32 CHECKER that the respective code is being transferred from the disk.                                                                                                                                                                                                                  |

| SRECC        | 0011  | This signal is used to inform the Programmable ECC CHECKER (MSD95SC01) or the Reed Solomon ECC CHECKER (MSD95SC02) that the ECC bytes are being transferred in from the disk.                                                                                                                                                            |

| SGAP         | 0100  | RESERVED FOR FUTURE USE.                                                                                                                                                                                                                                                                                                                 |