# DP8025 TROPIC™ Token-Ring Protocol Interface Controller

# **General Description**

The Token-Ring Protocol Interface Controller (TROPIC) is a microCMOS VLSI device designed for easy implementation of IEEE 802.5 Token-Ring LAN interface adapters. The TROPIC chip includes integrated Analog and Digital Token-Ring interfaces and bus interface support for ISA and MicroChannel hosts. Transmit and receive buffers are implemented in shared RAM, with buffer arbitration and control provided by the TROPIC chip.

TROPIC provides full IEEE 802.5 compatibility, including Medium Access Control (MAC) and Logical Link Control (LLC) protocol handling, and is IBM 802.5 certified. Network performance exceeds current 802.5 Jitter Requirements. The TROPIC supports both 16 Mbps and 4 Mbps operation, which are chip-selectable.

TROPIC integrates both digital and analog CMOS technologies in a single 175-pin, 1.48" (37.2 mm) module. Operation is driven by an integral Microprocessor Unit (MPU), which is microcoded for flexible functionality. The microcode controlling the MPU (provided with TROPIC) is stored in an external PROM, which allows simple PROM upgrades to remain current with any future changes to the IEEE 802.5 standard. External RAM is used for data, control, and scratch-pad storage. The TROPIC chip provides an interface for directly attaching the required external PROM and RAM devices.

Host Transmit and Receive buffers and control blocks are provided through a Shared RAM Interface, which is managed by a TROPIC integral controller. The control blocks are used to pass commands and messages between the Host system and TROPIC.

### **Features**

- Complete Token-Ring Adapter solution

- Integrated Bus Interface support for ISA and MicroChannel, including MicroChannel POS registers

- MAC Layer 802.5 and LLC executed in integral microprocessor unit (MPU), minimizing Host software

- MPU microcode provided

- Chip-selectable 16/4 Mbps operation

- Minimal supporting hardware required

- Single +5V supply required

- CMOS for low power dissipation

- Configurable RAM size and Page size

- Optional Parity on Host interface

- Shared buffer memory using standard 8k by 9 or 32k by 9 RAM

- Support for IBM Source Routing Bridges

- Minimal Host memory space required

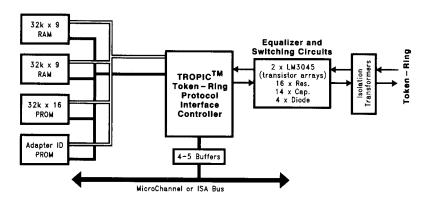

# 1.0 System Diagram

TL/F/11334-1

# **Table of Contents**

- 1.0 SYSTEM DIAGRAM

- 2.0 BLOCK DIAGRAM

- 3.0 FUNCTIONAL DESCRIPTION

- 4.0 INITIALIZATION

- 5.0 HOST ADDRESS SPACE STRUCTURE

- 6.0 REGISTERS

- 7.0 SOFTWARE OPERATION OF TROPIC

- **8.0 PIN DESCRIPTIONS**

- 9.0 HARDWARE INTERFACE

- 10.0 INTERFACE CONSIDERATIONS

- 11.0 DC AND AC SPECIFICATIONS

- 12.0 CONNECTION DIAGRAMS

- 13.0 PHYSICAL DIMENSIONS

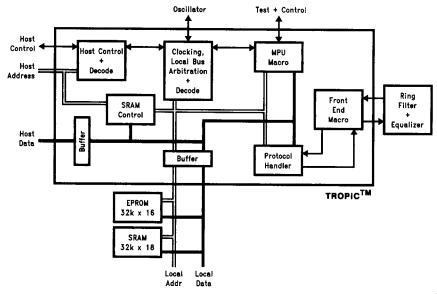

# 2.0 Block Diagram

TL/F/11334-2

# 3.0 Functional Description

TROPIC provides three external interfaces (Token-Ring, Host Bus, and Local Storage). TROPIC also requires certain Host system resources.

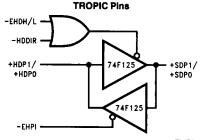

### **TOKEN-RING INTERFACE**

The Front End Macro within TROPIC supplies a Ring Interface. This provides signals and inputs for external equalization and transformer circuits that form the actual Token-Ring Serial interface. The external Token-Ring Serial Interface provides physical connection to the Token-Ring LAN Media. It must include appropriate filter circuits (one Transmit filter and two Receive filters, one each for 4 Mbps and 16 Mbps operation), switching circuitry to switch between the 4 Mbps and 16 Mbps Receive filters, and line protection and conditioning components.

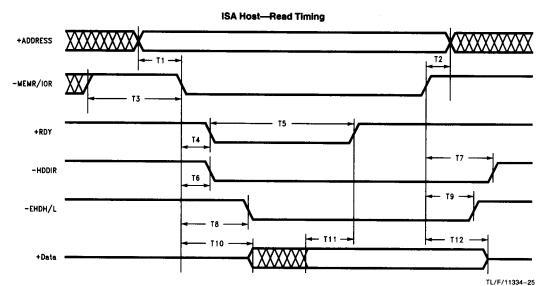

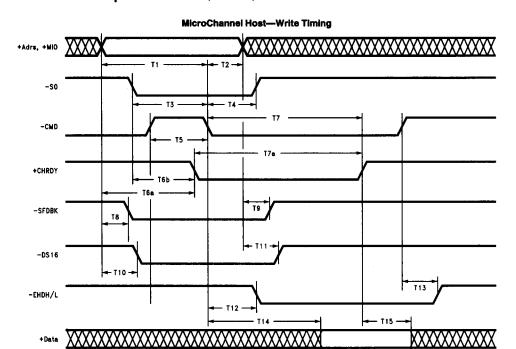

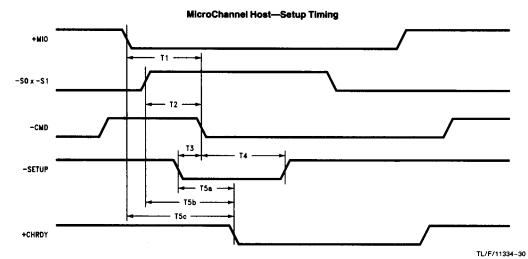

#### **HOST BUS INTERFACE**

The Host Bus interface allows the Host system to transfer data to and from TROPIC. This interface includes a twenty-four bit address bus, a sixteen bit data bus with optional parity, and control signals to allow the TROPIC Host Bus interface to attach directly, as a bus slave, to ISA or MicroChannel. This makes TROPIC appear to be a memory device on the Host Bus that can be read or written using standard memory access and MMIO (Memory Mapped I/O) procedures.

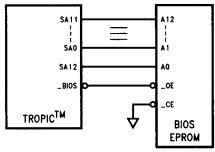

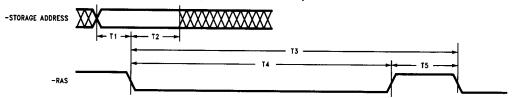

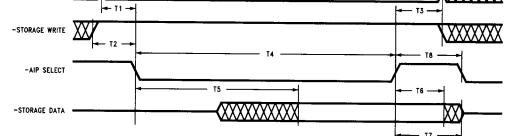

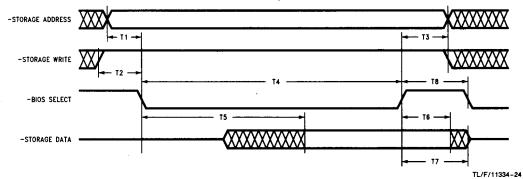

#### **LOCAL STORAGE INTERFACE**

This interface provides direct attachment from TROPIC to local PROM and RAM devices, which TROPIC controls exclusively. This interface includes an eighteen bit data bus and sixteen bit address bus, plus control lines to choose proper memory devices and control read and write operations.

#### HOST SYSTEM RESOURCE REQUIREMENTS

TROPIC requires four Host system resources for MicroChannel and ISA bus Hosts as follows:

- One Interrupt

- 16k or 64k of memory address space for Shared RAM buffers and control blocks (which allow passing of highlevel commands, frame data, and status codes between TROPIC and Host software)

- ROM/MMIO space (8k for MicroChannel/ISA)

- 5 bytes of I/O space for MicroChannel and ISA

Each of these resources is described in more detail later.

#### TROPIC INTERNAL ELEMENTS

TROPIC can be implemented with an understanding of just its external interfaces and Host requirements. However, some consideration of TROPIC's internal structure and data flow is useful.

TROPIC consists of four main logical blocks:

- Front End Macro (FEM)

- Protocol Handler

- Integral MPU

- Shared Memory Controller

The functions of each of TROPIC's internal logical elements is best understood by considering data flow through the device during reception and transmission of Token-Ring data, as described next (these discussions assume some understanding of Token-Ring message structures).

# 3.0 Functional Description (Continued)

#### TROPIC DATA FLOW—RECEPTION

#### Front End Macro

The Front End Macro (FEM), combined with external equalizer components, provides the interface needed to transmit and receive Manchester coded data over the Token-Ring media at either 4 Mbps or 16 Mbps. The provided functions include:

- · Equalization of transmission channel

- · Detection of receive signal

- · Clock recovery and re-timing of received signal

- · Transmission of output data

- Control functions, such as wrap test of interface circuit

- · Ring Insertion and Wire Fault detection

The Front End Macro provides D-to-A and A-to-D signal conversion only. The Protocol Handler and MPU perform MAC and LLC processing, encoding, and decoding of data streams.

Received signals that have been decoded to NRZ clock and data form are sent to the Protocol Handler.

### **Protocol Handler**

When data is received from the Front End Macro, the Protocol Handler first converts the serial data to byte parallel data usable by the MPU, and generates parity on the received data for subsequent internal validity checks.

At the proper time during the receive sequence, the Protocol Handler begins bit-wise CRC (Cyclic Redundancy Check) accumulation on the received data. At the proper point in the received message, the Protocol Handler extracts the Token-Ring destination address. It then compares it with the values loaded into the Protocol Handler to determine if the message should be copied by this station. If so, the Protocol Handler begins transferring the message to TROPIC's local RAM for additional MPU operations.

The Protocol Handler transfers, in order, the physical control field, the Token-Ring destination and source addresses, the data fields, and the message's CRC characters. When the CRC-protected portion of the message has been received, the received CRC characters are checked for validity.

If there is a CRC mismatch, the local RAM area used to store the message is released and the message is not processed. Otherwise, proper changes are made to the frame status byte after the end of frame delimiter. At this point, processing moves from the Protocol Handler to the MPU.

#### MPU

The MPU assembles the data transferred from the Protocol Handler into multi-byte segments. The areas where the message data has been stored are set up as valid for transfers to the Host Bus via the Shared Memory interface.

The actual mapping and management of data into the buffers is controlled by the MPU microcode, and is also affected by certain host-controlled parameters and status codes from the Protocol Handler.

#### Shared Memory Controller

When the transfer is complete, a status code is written to the appropriate buffer control block address in Shared RAM and an interrupt is issued to the Host. The Host software can then transfer the received data out of the Shared Memory area.

### TROPIC DATA FLOW-TRANSMISSION

Transmissions from the Host are essentially the opposite of receptions. The Host software transfers data and an appropriate transfer command code to a free buffer in Shared RAM, and then signals TROPIC's MPU that a message is waiting. The MPU then sets up the Protocol Handler to begin a transfer from Shared Memory.

When the Protocol Handler senses a pending transmission, it begins transferring the data into its 32-byte FIFO. When enough data is buffered to allow continuous transmission through the Front End Macro, the Protocol Handler waits for a token on the LAN. When a token is acquired, it is converted to a frame. Applicable control characters are generated, encoded, and transmitted (via the FEM), and the transmission continues with destination and source addresses, followed by the information field. When the entire information field has been transferred, the Protocol Handler inserts the CRC characters that it has accumulated into the message, followed by the encoded delimiter and frame status byte.

### 4.0 Initialization

The TROPIC can be configured to work in a number of environments. The Power-On Reset configuration is initialized in three ways:

- by setting TROPIC configuration input pins to steady state levels via switches, jumpers, pullup/pulldown resistors, or hard-wiring of the input pins

- · by Microcode setting of software control switches

- by loading configuration data into internal TROPIC registers (Configuration Registers). In MicroChannel Hosts, this is accomplished by writing to TROPIC's internal POS registers. For all other implementations, the TROPIC Configuration Registers are loaded from the Storage Data bus after reset (as described later in this section).

#### TROPIC CONFIGURATION PINS

Four input pins are used to configure TROPIC for the Host environment: DPEN, -CFG2, -CFG1, and -CFG0.

The DPEN pin enables/disables generaton and checking of parity of the Host dats bus. The Host Configuration pins —CFG2, —CFG1, and —CFG0 are used to identify the Host bus type, as shown below. This affects various operating aspects, including memory mapping and register usage.

# 4.0 Initialization (Continued)

Host Configuration Pins (0 = GND, 1 =  $V_{CC}$ )

| -CFG2 | -CFG1 | -CFG0 | Bus Type Indicated  |

|-------|-------|-------|---------------------|

| 1     | 1     | 1     | ISA 16-bit          |

| 0     | 1     | 1     | ISA 8-bit           |

| 1     | 0     | 1     | MicroChannel 16-bit |

| 0     | 0     | 1     | MicroChannel 8-bit  |

| 1     | 1     | 0     | Reserved            |

| 0     | 1     | 0     | Reserved            |

| 1     | 0     | 0     | Reserved            |

| 0     | 0     | 0     | Reserved            |

#### **MICROCODE SETTINGS**

Several TROPIC registers are initialized by PROM microcode. These control mostly memory mapping and management and internal parity functions, and are usually unavailable to the Host (even in Ready-only mode).

#### TROPIC CONFIGURATION REGISTERS

In MicroChannel host environments, the Configuration Registers are loaded directly from the host during POS. For all other host implementations, the Configuration Register is automatically loaded from the Storage data bus after reset. Access to the Configuration Registers is limited and varies according to Host bus type.

Besides Host Bus type (set by configuration pins), the following TROPIC aspects can also be configured:

ROM/MMIO Host Base Address—Defines the base address (in the Host's memory space) for the ROM/MMIO control area

- Host Interrupt Level—For ISA and MicroChannel bus types, defines the IRQ level to be used

- Ring Speed—Selects 4 Mbps or 16 Mbps Ring Speed

- RAM Type—Indicates the type of storage RAM (static or dynamic) used on the TROPIC-based adapter

- Shared RAM Page Size—Selects the Shared RAM interface page (window) size in host memory space

- Primary/Secondary Adapter—For ISA and MicroCharnel bus types, sets TROPIC to respond as either the Primary Adapter (x0A20) or the Secondary Adapter (x0A24h)

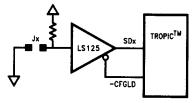

To facilitate the load of the configuration data for ISA Host implementations, TROPIC provides the signal -CFGLD. This signal can be used to "gate" configuration data onto the storage data bus as illustrated below:

TL/F/11334-5

Storage Data bus signals during configuration load are defined as shown in the table on the next page.

# 4.0 Initialization (Continued)

Storage Data Bus Signals during ISA Configuration Load (0 = GND, 1 =  $V_{CC}$ )

| Data Bit(s)* | Configuration Description                                                                                                                                                                                                  |                                                    |                                                                     |                                                                                                  |  |  |  |  |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| SD15-SD9     | BIOS/MMIO Base Address—Defines initial Host Base Address for the TROPIC ROM/MIO region of host memory (described in Section 5.0). Data Bits correspond to the inverted sense of host address lines HA19-HA13 respectively: |                                                    |                                                                     |                                                                                                  |  |  |  |  |  |  |  |  |

|              | 0000                                                                                                                                                                                                                       | 0000                                               | xFE000                                                              |                                                                                                  |  |  |  |  |  |  |  |  |

|              | •                                                                                                                                                                                                                          | •                                                  |                                                                     |                                                                                                  |  |  |  |  |  |  |  |  |

|              | •                                                                                                                                                                                                                          | •                                                  |                                                                     |                                                                                                  |  |  |  |  |  |  |  |  |

|              | 0010                                                                                                                                                                                                                       | 111                                                | xD0000                                                              |                                                                                                  |  |  |  |  |  |  |  |  |

|              | •                                                                                                                                                                                                                          | •                                                  |                                                                     |                                                                                                  |  |  |  |  |  |  |  |  |

|              | •                                                                                                                                                                                                                          |                                                    |                                                                     |                                                                                                  |  |  |  |  |  |  |  |  |

|              | 0011                                                                                                                                                                                                                       | 001                                                | xCC000                                                              |                                                                                                  |  |  |  |  |  |  |  |  |

|              |                                                                                                                                                                                                                            |                                                    |                                                                     |                                                                                                  |  |  |  |  |  |  |  |  |

|              | 1111                                                                                                                                                                                                                       | , , , , ,                                          | x00000                                                              |                                                                                                  |  |  |  |  |  |  |  |  |

|              |                                                                                                                                                                                                                            | ·                                                  |                                                                     |                                                                                                  |  |  |  |  |  |  |  |  |

| SD8-SD7      | Encoded IRQ Lev                                                                                                                                                                                                            | vei (ISA ONLY)                                     |                                                                     | for adapter, as follows:                                                                         |  |  |  |  |  |  |  |  |

|              | 50.0                                                                                                                                                                                                                       | 5                                                  | Selected                                                            |                                                                                                  |  |  |  |  |  |  |  |  |

|              | Bit 8                                                                                                                                                                                                                      | Bit 7                                              | IRQ                                                                 |                                                                                                  |  |  |  |  |  |  |  |  |

|              | 0                                                                                                                                                                                                                          | 0                                                  | IRQ7                                                                |                                                                                                  |  |  |  |  |  |  |  |  |

|              | 0                                                                                                                                                                                                                          | 1                                                  | IRQ6                                                                |                                                                                                  |  |  |  |  |  |  |  |  |

|              | 1                                                                                                                                                                                                                          | 0                                                  | IRQ3                                                                |                                                                                                  |  |  |  |  |  |  |  |  |

|              | 1                                                                                                                                                                                                                          | 1                                                  | IRQ2                                                                |                                                                                                  |  |  |  |  |  |  |  |  |

| SD6          | Reserved—must                                                                                                                                                                                                              | be set to 0.                                       |                                                                     |                                                                                                  |  |  |  |  |  |  |  |  |

| SD5          | RAM Type: Indica<br>0 = Static RAM, 1                                                                                                                                                                                      |                                                    | -                                                                   | he TROPIC-based adapter.                                                                         |  |  |  |  |  |  |  |  |

| SD4          | Reserved-DO N                                                                                                                                                                                                              | OT drive                                           |                                                                     |                                                                                                  |  |  |  |  |  |  |  |  |

| SD3-SD2      |                                                                                                                                                                                                                            |                                                    | RAM. These bits are co                                              | (window) size, i.e., the amount of the Host's memory ded as follows:                             |  |  |  |  |  |  |  |  |

|              |                                                                                                                                                                                                                            | 200                                                | Page                                                                |                                                                                                  |  |  |  |  |  |  |  |  |

|              | SD3                                                                                                                                                                                                                        | SD2                                                | Size                                                                |                                                                                                  |  |  |  |  |  |  |  |  |

|              | l o                                                                                                                                                                                                                        | 0                                                  | 64 kB                                                               |                                                                                                  |  |  |  |  |  |  |  |  |

|              | -                                                                                                                                                                                                                          |                                                    | 0010                                                                |                                                                                                  |  |  |  |  |  |  |  |  |

|              | o                                                                                                                                                                                                                          | 1                                                  | 32 kB                                                               |                                                                                                  |  |  |  |  |  |  |  |  |

|              | 0                                                                                                                                                                                                                          | 1<br>0                                             | 16 kB                                                               |                                                                                                  |  |  |  |  |  |  |  |  |

|              | 1 1                                                                                                                                                                                                                        | 0                                                  | 16 kB<br>8 kB                                                       |                                                                                                  |  |  |  |  |  |  |  |  |

|              | 1<br>1<br>This shared RAM                                                                                                                                                                                                  | 0<br>1<br>page size may                            | 16 kB<br>8 kB<br>not be the total amount                            | of shared RAM on the adapter. For example, an adapter<br>B page size to allow shared RAM paging. |  |  |  |  |  |  |  |  |

| SD1          | 1<br>1<br>This shared RAM                                                                                                                                                                                                  | 0<br>1<br>page size may<br>lable shared R <i>A</i> | 16 kB<br>8 kB<br>not be the total amount<br>M can be set for a 16 k | of shared RAM on the adapter. For example, an adapter<br>B page size to allow shared RAM paging. |  |  |  |  |  |  |  |  |

<sup>\*</sup>TROPIC Storage Data Lines are internally pulled up to V<sub>CC</sub>. Allowing a data line to "float" during configuration load will result in setting that bit/option to "1". For more detailed descriptions of configuration register bit fields see Section 6.0.

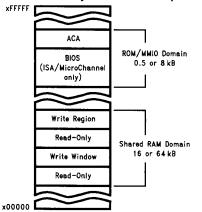

# 5.0 Host Address Space Structure

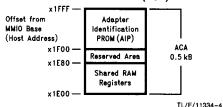

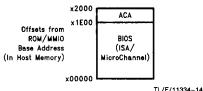

TROPIC's Host Address Space is divided into two domains: Shared RAM and ROM/MMIO, shown below:

### Shared Memory—Host Address Map

TL/F/11334-3

#### SHARED RAM DOMAIN

As discussed in the Functional Description, transmission and reception data and control blocks are transferred between TROPIC and the Host via the TROPIC Shared RAM area. This area can be either 16 kB or 64 kB, depending on the Host's upper memory area usage; its size and initial base address are configured during Reset initialization.

During operation, Shared RAM can be relocated and paged. Location and paging status are available through the Shared RAM address parameters defined in the RAM Relocation Register (RRR) and Shared RAM Paging Register (SRPR), as described in Section 6.0.

Mapping of the buffers and control blocks in Shared RAM is controlled by microcode. Buffer management and handshaking are summarized in Section 7.0. More complete details are beyond the scope of this document, and are covered in a separate programming document.

### ROM/MMIO (MEMORY MAPPED I/O) DOMAIN

For MicroChannel and ISA Hosts, the ROM/MMIO domain is 8k and includes 7.5k for BIOS and 0.5k for an area called the Attachment Control Area (ACA).

The structure of the ACA is shown below.

#### Attachment Control Area (ACA)

The Adapter Identification PROM (AIP) area is a read-only region that contains unique adapter parameters, such as the IEEE node address and serial number.

The area from x1E80 to x1EFF is reserved and should not be accessed by the Host.

The MMIO Registers provide several important status and control registers that are accessible to the Host during operation. These are discussed in the next section.

# 6.0 Registers

The Host communicates with and controls TROPIC using three methods: Shared RAM, interrupts, and registers.

TROPIC supports three register areas:

- MMIO Registers—these are used by all Host bus types

- Programmed I/O (PIO) Registers—these are used only by ISA and MicroChannel hosts and are decoded during normal operation

- MicroChannel Standard POS Registers—these are used only by MicroChannel hosts and are decoded only during Setup

Note: POS Registers reside in PIO space, but are treated separately because they are only decoded during Setup.

#### **REGISTER USAGE AND LOCATION BY BUS TYPE**

Register usage varies by bus type, as shown below.

#### Register Usage by Bus Type

| Bus Type | MMIO<br>Registers | PIO<br>Registers | MicroChannel<br>POS Registers |

|----------|-------------------|------------------|-------------------------------|

| MCS      | Yes               | Yes              | Yes                           |

| ISA      | Yes               | Yes              | No                            |

Memory allocation of registers is shown below.

#### Register Location by Bus Type

|                  | PIO Space (ISA)                      | PIO Spa          | ace (MicroChannel                    |

|------------------|--------------------------------------|------------------|--------------------------------------|

| !                | x0FFFF<br>x00A28 Unused              |                  | x0FFFF Unused                        |

| x00A27<br>x00A24 | Adapter 1 PIO<br>Registers           | x00A27<br>x00A24 | Adapter 1 PIO<br>Registers           |

| x00A23<br>x00A20 | Adapter 0 PIO<br>Registers           | x00A23<br>x00A20 | Adapter 0 PIO<br>Registers           |

|                  | x00A1F<br>x002F8 Unused              |                  | x00A1F                               |

| x002F7           | Giobal Interrupt<br>Enable (IRQ7)    |                  |                                      |

| x002F6           | Giobal Interrupt<br>Enable (IRQ6)    |                  | Unused                               |

|                  | x00AF5<br>x002F4 Unused              |                  |                                      |

| x002F3           | Global Interrupt<br>Enable (IRQ3)    | ×00107           | x00108                               |

| x002F2           | Global Interrupt<br>Enable (IRQ2, 9) | x00100           | POS Registers<br>(Only during Setup) |

|                  | x002F1<br>x00000 Unused              |                  | x000FF<br>x00000 Unused              |

|                  | TL/F/11334-0                         | 3                | TL/F/11334-                          |

#### MMIO Space (All Busses) Unused x1E1A Reserved x1E18 Shared RAM Page Register (SRPR) x1E10 Reserved x1E0E Timer Value Register (TVR) Timer Control Register (TCR) x1E0C x1E0A TROPIC Interrupt/Status Register (TISR) Host Interrupt/Status Register (HISR) x1E08 x1E06 Write Window Close Register (WWCR) x1E04 Write Window Open Register (WWOR) Write Region Base Register (WRBR) x1E02 RAM Relocation Register (RRR) x1E00

Unused

TL/F/11334-8

### MMIO REGISTERS-GENERAL

The MMIO Registers are used by all bus types and are located within the ACA Host Address Space area. They include mostly read-only status registers, with a few Read/Write control registers. For ISA and MicroChannel buses, some of these registers are replicated in the PIO Registers; in such cases, one register is usually read-only while the alternative location is read/write. All of the MMIO Registers consists of two-byte (word) registers, each having its low order byte at an even address and its high order byte at the following odd address. Note that addresses are relative to the ROM/MMIO Base Address.

### MMIO REGISTERS-ISA AND MICROCHANNEL

This section describes MMIO Register usage in detail for ISA and MicroChannel Hosts.

#### **RAM Relocation Register (RRR)**

This register is used to relocate the Shared RAM region and indicate its page size and location. It also contains bits used to control different TROPIC operating modes.

Warning: Reserved bits (indicated by "-"), though readable, are controlled by TROPIC. These bits should not be changed.

ISA BUS MODE:

|    |    |    | x1i | E01 |      |   |   |      |      |      | x1l  | E00  |      |               |   |

|----|----|----|-----|-----|------|---|---|------|------|------|------|------|------|---------------|---|

| 15 | 14 | 13 | 12  | 11  | 10   | 9 | 8 | 7    | 6    | 5    | 4    | 3    | 2    | 1             | 0 |

| _  | _  |    | _   | RAM | Size | _ | _ | AB19 | AB18 | AB17 | AB16 | AB15 | AB14 | AB13<br>(= 0) | _ |

### **MICROCHANNEL BUS MODE:**

|    |    |    | x1 | E01 |        |   |   |   |   |   | <b>x1</b> l | E00 |   |   |   |  |

|----|----|----|----|-----|--------|---|---|---|---|---|-------------|-----|---|---|---|--|

| 15 | 14 | 13 | 12 | 11  | 10     | 9 | 8 | 7 | 6 | 5 | 4           | 3   | 2 | 1 | 0 |  |

| _  | _  | _  | -  | RAM | l Size | _ | _ | _ | _ |   | _           | _   |   | _ |   |  |

| Bit(s) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |  |  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|

| 15-12  | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |  |  |

| 11–10  | <b>Shared RAM Page Size:</b> Selects the shared RAM page (window) size, i.e., the amount of the Host's memory space that is allocated to shared RAM. These bits are coded as follows:                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |  |  |  |

|        | 11 10 Page Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |  |  |  |

|        | 0 0 8 kB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |  |  |

|        | 0 1 16 kB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |  |  |

|        | 1 0 32 kB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |  |  |

|        | 1 1 64 kB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |  |  |

|        | This shared RAM page size may not be the total amount of shared RAM on the adapter; instead, this value indicates the amount of shared RAM for the Host to map into its memory. For example, an adapter with 64 kB of available shared RAM can be set for a 16 kB page size to allow shared RAM paging. If the RRR bit 11 is set to 0 and bit 10 is set to 1, this would indicate 16 kB of shared RAM in the Host's memory map.                                                                                |  |  |  |  |  |  |  |  |  |  |  |  |

|        | Note: To use Shared RAM paging, Host software must also use the SRPR (Shared RAM Paging Register) correctly. See the later SRPR description for details.                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |  |  |

| 9-8    | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |  |  |

| 7-1    | (FOR MICROCHANNEL BUS MODE) Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |  |  |  |

|        | (FOR ISA BUS MODE) Shared RAM Host Base Address:                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |  |  |

|        | For TROPIC adapters in ISA I/O Bus mode, bits 7 through 1 of the RRR register are used to set the shared RAM starting address. This location must be set before the Shared RAM can be accessed and must be set to a location in the memory map that does not cause a conflict. These register bits default to zero on power-up or after an adapter reset. If the register contains zero, the shared RAM is not mapped into the memory map. This register must be set to a correct address boundary as follows: |  |  |  |  |  |  |  |  |  |  |  |  |

|        | 8 kB shared RAM page should be on an 8 kB address boundary.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |  |  |

|        | <ul> <li>16 kB shared RAM page should be on a 16 kB address boundary.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |  |  |

|        | 32 kB shared RAM page should be on a 32 kB address boundary.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |  |  |

|        | 64 kB shared RAM page should be on a 64 kB address boundary.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |  |  |

|        | For shared RAM paging, the address boundary can be on a 16 kB boundary since only 16 kB of PC address space is used                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |

|        | Note: To select a valid address boundary, RRR Bit 1 (AB13) should always be set to 0.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |  |  |  |

|        | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |  |  |

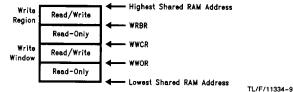

Write Region Base Register (WRBR)—READ ONLY Write Window Open Register (WWOR)—READ ONLY Write Window Close Register (WWCR)—READ ONLY

#### WRBR (Read Only):

|    |    |         | <b>x</b> 1 | E03     |         |   |   |   |   |         | x1        | E02      |         |   |   |

|----|----|---------|------------|---------|---------|---|---|---|---|---------|-----------|----------|---------|---|---|

| 15 | 14 | 13      | 12         | 11      | 10      | 9 | 8 | 7 | 6 | 5       | 4         | 3        | 2       | 1 | 0 |

|    | L  | SB (Lea | st Signifi | cant By | te) WRB | R |   |   | M | ISB (Mo | st Signif | icant By | te) WRB | R |   |

### WWOR (Read Only):

|    |    |          | x1l        | E05      |        |   |   |   |   |         | x1         | E04     |         |    |   |

|----|----|----------|------------|----------|--------|---|---|---|---|---------|------------|---------|---------|----|---|

| 15 | 14 | 13       | 12         | 11       | 10     | 9 | 8 | 7 | 6 | 5       | 4          | 3       | 2       | 1  | 0 |

| L  | LS | SB (Leas | st Signifi | cant Byt | e) WWC | R |   |   | М | SB (Mos | st Signifi | cant By | te) WWC | )R |   |

#### WWCR (Read Only):

|    |    |          | x1I        | E07      |        |   |   |   |   |         | x1         | E06     |         |   |   |

|----|----|----------|------------|----------|--------|---|---|---|---|---------|------------|---------|---------|---|---|

| 15 | 14 | 13       | 12         | 11       | 10     | 9 | 8 | 7 | 6 | 5       | 4          | 3       | 2       | 1 | 0 |

|    | LS | SB (Leas | st Signifi | cant Byt | e) WWC | R |   |   | М | SB (Mos | st Signifi | cant By | te) WWC | R |   |

These management register pairs specify an offset into shared RAM. The offsets are 16-bit values. The even register contains the most significant byte of this value. For example:

WRBR(15-8) at x1E03 = 24 (LSB)

WRBR(7-0) at x1E02 = 47 (MSB)

WRBR full register value = 2447

In this example, a 16-bit Read of the WRBR (at x1E02) returns 2447; however, the logical (useable) address value is 4724. **IMPORTANT:** To obtain a useable address, Host software **must** perform a byte-swap on 16-bit Reads from the WRBR, WWOR, and WWCR registers.

As illustrated below, TROPIC can concurrently define two separate and independent computer write areas within the Shared RAM domain: the write region and the write window. The size of each of these areas can be individually defined in word (2-byte) increments from 2 bytes to the maximum size of the shared RAM domain.

The two areas differ only in how they are bound. The write region always extends from the highest address of the shared RAM domain down to a variable origin specified by the WRBR. The write window extends from a variable base defined by the WWOR pair to a variable limit defined by the WWCR pair. Also, the low-order bit in each odd register is zero since all write boundaries are word (2-byte) aligned.

Any address in the shared RAM not given specific Host write access by the shared RAM management registers is given Host read-only access. A Host write to any of these read-only memory addresses or to any shared RAM management register MMIO address will not be completed and will activate the Host Access error interrupt condition (HISR bit 2). Since the origin of the write region (WRBR) and the write window (WWOR) must be greater than zero if either write area is to be defined, the first 2 bytes of the shared RAM domain are always read-only to the Host.

The interface mechanism allows the Host read-only access to the entire shared RAM domain until TROPIC is initialized and Host write-access areas are defined by TROPIC.

The WRBR contains either zero or the offset of the beginning of the write region. When this field is zero, no write region is available. The WWOR contains either zero or the offset of the beginning of the write window. This field contains zero until TROPIC is opened, and when it is zero, no write window is available. The WWCR contains either zero or the first offset after the last writeable offset. This field is reserved until TROPIC is opened, and when it is zero, no write window is available.

# HOST INTERRUPT/STATUS REGISTER (HISR)

This read/write register contains interrupt and control bits to allow TROPIC to issue interrupts to Host software.

|    |      |      | x1I  | E09  |      |      |   | x1E08 |      |   |      |      |      |      |       |

|----|------|------|------|------|------|------|---|-------|------|---|------|------|------|------|-------|

| 15 | 14   | 13   | 12   | 11   | 10   | 9    | 8 | 7     | 6    | 5 | 4    | 3    | 2    | 1    | 0     |

| _  | тснк | SRBR | ASBF | ARBC | SSBR | BFFC | _ | CH/IR | INTE | _ | TINT | EINT | AINT | IBLK | PR/AL |

| Bit(s) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15     | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 14     | TROPIC Check (TCHK): TROPIC has encountered an unrecoverable error and is closed. The reason for the check may be read from the shared RAM using the address in the write window close management register pair in the attachment control area of the MMIO region. The information returned is defined in the separate programming reference document.                                                                                                                                                                                                                                                              |

| 13     | SRB Response (SRBR): TROPIC has recognized an SRB request and has set the return code in the SRB. A return code of:  x00: Indicates successful completion of the SRB request.  x01-xFD: Indicates unsuccessful completion of the SRB request.  xFF: Indicates that the request has been accepted and is in process. A subsequent SSB response will be issued at the command completion. This interrupt bit is set for this return code only if the Host has set the "SRB Free Request" bit in the TISR.                                                                                                             |

| 12     | ASB Free (ASBF): TROPIC has read the response provided in the ASB, and the ASB is available for another response. This interrupt bit is set only if the Host has set the "ASB Free Request" bit in the TISR or if an error has been detected in the response.                                                                                                                                                                                                                                                                                                                                                       |

| 11     | ARB Command (ARBC): The ARB contains a command for the Host to act on.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10     | SSB Response (SSBR): The SSB contains a response to a previous SRB command from the Host.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9      | Bridge Frame Forward Complete (BRFC): TROPIC has completed transmitting a frame forwarded by the bridge Host software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8      | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7      | CHCK/IRQ Steering Control (CH/IR): This bit is used to control error interrupts. If 0, TROPIC will issue a CHCK. If 1, TROPIC will issue IRQ. CHCK is not supported in ISA and MicroChannel bus modes and, for those modes, this bit must be set to 1.                                                                                                                                                                                                                                                                                                                                                              |

| 6      | Interrupt Enable (INTE): When this bit is on, interrupt requests will be presented to the Host. When this bit is off, all interrupts are masked off. The bit can be set by either TROPIC or the Host.                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5      | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4      | Timer Interrupt (TINT): When this bit is on, the TVR(7-0) has expired.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3      | Error Interrupt (EINT): TROPIC has had a machine check occur, the TROPIC deadman timer expire, or the TROPIC timer overrun.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2      | Access Interrupt (AINT): When this bit is on, it indicates that a shared RAM access violation or an illegal MMIO operation by the Host to an Attachment Control Area register pair has occurred. The following conditions will set this bit:  • Any Host write to a write-protected location in the shared RAM domain  • Any Host write to a shared RAM management (WRBR, WWCR, WWOR) register  • Any Host write to HISR(7-0)  • Any Host write to a nonzero interrupt field of TISR(15-8) or HISR(15-8). Nonzero interrupt fields of TISR(15-8) and HISR(15-8) must be manipulated using OR and AND MMIO commands. |

| 1      | 1SA Bus Mode ONLY Interrupt Block Bit (IBLK): Set by TROPIC to prevent interrupts until interrupts are re-enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0      | Primary/Alternate Address (PR/AL): This bit reflects the setting of the TROPIC primary/alternate setup information. If this bit is off, the primary adapter address is selected. If this bit is on, the alternate adapter address is selected.                                                                                                                                                                                                                                                                                                                                                                      |

# TROPIC INTERRUPT/STATUS REGISTER (TISR)

This read/write register provides interrupts (for Shared RAM management, errors, timeouts, and other events) and control values that allow Host software to issue interrupts to TROPIC (letting the Host and TROPIC communicate asynchronously). The Host software sets bits in TISR(14-8) to interrupt TROPIC.

| x1E0B |      |      |      |       |       |      |      | x1E0A |       |       |       |       |   |      |      |

|-------|------|------|------|-------|-------|------|------|-------|-------|-------|-------|-------|---|------|------|

| 15    | 14   | 13   | 12   | 11    | 10    | 9    | 8    | 7     | 6     | 5     | 4     | 3     | 2 | 1    | 0    |

|       | BFFR | CSRB | RASB | SRBFR | ASBFR | ARBF | SSBF | IPE   | TINTT | AINTT | DTEXP | TCHKT |   | ТНІМ | тѕім |

| Bit(s) | Description .                                                                                                                                                                                                                     |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15     | Reserved.                                                                                                                                                                                                                         |

| 14     | <b>Bridge Frame Forward Request (BRFR):</b> The Host software has placed a frame in the bridge transmit buffers and is requesting that the frame be forwarded.                                                                    |

| 13     | Command in SRB (CSRB): The Host software has placed a command in the SRB and is informing TROPIC.                                                                                                                                 |

| 12     | Response in ASB (RASB): The Host software has placed a response to an ARB request in the ASB and is informing TROPIC.                                                                                                             |

| 11     | SRB Free Request (SRBFR): The Host software wants to use the SRB, but a previous request is still being processed by TROPIC. TROPIC will return an "SRB free" interrupt when the SRB return code field has been set.              |

| 10     | ASB Free Request (ASBFR): The Host software wants to use the ASB, but a previous response is still being processed by TROPIC. TROPIC will return an "ASB free" interrupt when the ASB return code field has been set.             |

| 9      | ARB Free (ARBF): The command in the ARB has been read by the Host software and the ARB is available. If the command requires a response from the Host software (receive and transmit only), it will be provided in the ASB later. |

| 8      | SSB Free (SSBF): The response in the SSB has been read by the Host software and the SSB is available.                                                                                                                             |

| 7      | internal Parity Error (IPE): If this bit was on, there was a parity error on TROPIC's internal bus.                                                                                                                               |

| 6      | Timer Interrupt—TROPIC (TINTT): At least one of the TCR(15-8) timers has an interrupt to present to TROPIC.                                                                                                                       |

| 5      | Access Interrupt—TROPIC (AINTT): When this bit is on, it indicates that a shared RAM access violation or an illegal MMIO operation by TROPIC to an Attachment Control Area register has occurred.                                 |

| 4      | Deadman Timer Expired (DTEXP): The deadman timer has expired, indicating an adapter microcode problem. This bit is one of the conditions that can set HISR bit 3.                                                                 |

| 3      | TROPIC Processor Check—TROPIC (TCHKT): This bit does not latch on but follows the state of the TROPIC processor machine check indication. This bit is one of the conditions that can set HISR bit 3.                              |

| 2      | Reserved.                                                                                                                                                                                                                         |

| 1      | <b>TROPIC Hardware Interrupt Mask (THIM):</b> When this bit is on, it prevents adapter hardware interrupts (TISR bits 7 and 5) from being presented to the TROPIC processor.                                                      |

| 0      | TROPIC Software Interrupt Mask (TSIM): When this bit is on, it prevents Host software interrupts (TISR bits 14-8) from being presented to the TROPIC processor.                                                                   |

# TIMER CONTROL REGISTER (TCR)

This register controls both Host and ring timing. TCR(7-0) is used with the TVR register to control the Host programmable timer. TCR(15-8) controls the fixed-duration timers used by TROPIC's microcode timing routines, and is reserved.

| x1E0D |     |    |    |    |    |   |     |      |      | x1E0C |      |      |      |   |   |

|-------|-----|----|----|----|----|---|-----|------|------|-------|------|------|------|---|---|

| 15    | 14  | 13 | 12 | 11 | 10 | 9 | 8   | 7    | 6    | 5     | 4    | 3    | 2    | 1 | 0 |

| _     | T — | _  | _  | _  | 1  | _ | [ _ | PTIM | PTRM | PTCG  | PTOS | PTCS | HLCK | _ | _ |

| Bit(s) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-8   | Reserved (TROPIC MPU timer control).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7      | Host Programmable Timer Interrupt Mask (PTIM): This bit controls the timer interrupt operation. When this bit is on, the timer interrupts the Host when the programmable count expires. When the bit is off, the timer will not interrupt the Host, and the timer status must be obtained by polling either HISR bit 4 or TVR(7-0). The timer interrupt, like all Host interrupts, is also subject to the interrupt enable bit (HISR bit 6).                                                                                                                                                                       |

| 6      | Host Programmable Timer Reload Mode (PTRM): If this bit is on, the timer automatically reloads from TVR(15-8) when the countdown expires (reaches zero). When this bit is off, the timer must be reprogrammed or restarted after each countdown. Setting bit 6 while the count is counting reloads TVR(7-0) with the initial count in TVR(15-8).                                                                                                                                                                                                                                                                   |

| 5      | Host Programmable Timer Count Gate (PTCG): This bit enables/disables timer counting and also allows reloading of the initial countdown from TVR(15-8). Setting the bit to 1 enables the timer and starts counting. Resetting to 0 disables the timer and halts decrementing of the timer count. The countdown may be resumed by writing a 1 back to this bit, since the count contained in the timer is not changed when the gate bit is cleared. However, if a gate set is received when the gate bit is already on and timer count is 0, the countdown value reloads from TVR(15-8) and a full countdown begins. |

| 4      | Host Programmable Timer Overrun Status (PTOS): This bit is set when an overrun condition is detected with the Host timer interrupt. If the timer interrupt has not been reset before the end of the next timing period, the overrun bit is set at the end of that period. Once set, this status bit remains active until reset to zero by the Host.                                                                                                                                                                                                                                                                |

| 3      | Host Programmable Timer Count Status (PTCS): This bit is Host Read-only and is set by TROPIC when the timer contains a nonzero countdown value (the timer is loaded but not necessarily counting). If this bit is 1, the nonzero timer counter value can be obtained by reading TVR(7–0). Otherwise, reads to the TVR(7–0) return zeroes. When the timer countdown is halted by clearing of TCR bit 5 and the count value is not zero, this bit will remain active (set to 1).                                                                                                                                     |

| 2      | Host Interlock (HLCK): This interlock allows TROPIC's internal diagnostic routine to check the functional capability of the Host timing facility without interference from the Host. When set to 1, this bit prevents Host MMIO writes from updating the contents of the TVR register and the Host portion (except this bit) of TCR(7-0). This bit will be set only when TROPIC's internal diagnostic procedures require exclusive use of the Host programmable timer.                                                                                                                                             |

| 1-0    | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

### **TIMER VALUE REGISTER (TVR)**

This register contains the Host timer initial countdown value in TVR(15-8) and the current Host timer count in TVR(7-0) (referred to as "the timer"). Reading TVR(15-8) always returns the last value written to it (zero following initial power-on). Both TVR(15-8) and TVR(7-0) are cleared after power-on reset. For each byte, possible values range from 10 ms (x01) to 2.55 seconds (xFF) in 10 ms increments.

If the timer contains zeros, writing a byte to TVR(15–8) transfers that value to the timer. Counting is then subject to the state of the TCR(5) gate bit. A read of TVR(7–0) returns the actual contents of the Host timer counter at the time the read is received by TROPIC. Writes to TVR(7–0) are ignored.

If the counter is loaded (nonzero), a write to the TVR(15-8) register will not cause the timer to be reloaded. The loading of the new TVR(15-8) value to the timer is governed by the state of the TCR gate and reload bits (TCR bits 5 and 6).

The TCR(3) count status bit and the TCR(5) gate bit are used with TVR(7-0). When the timer is loaded (the TCR(3) count status bit is 1), the value returned from TVR(7-0) is the actual timer count at the time of the read. If the TCR(3) gate bit is 1, then the counter will be counting and the value returned will reflect the current instantaneous counting state.

| x1E0F |                             |    |    |    |    |   |   |   | x1E0E |       |         |         |       |   |   |  |

|-------|-----------------------------|----|----|----|----|---|---|---|-------|-------|---------|---------|-------|---|---|--|

| 15    | 14                          | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6     | 5     | 4       | 3       | 2     | 1 | 0 |  |

| L     | Timer Initial Count (TINIT) |    |    |    |    |   |   |   |       | Timer | Current | Count ( | TCUR) |   |   |  |

| Bit(s) | Description                                                           |  |

|--------|-----------------------------------------------------------------------|--|

| 15-8   | Host Programmable Timer Initial Count (TINIT): See description above. |  |

| 7-0    | Host Programmable Timer Current Count (TCUR): See description above.  |  |

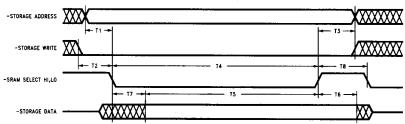

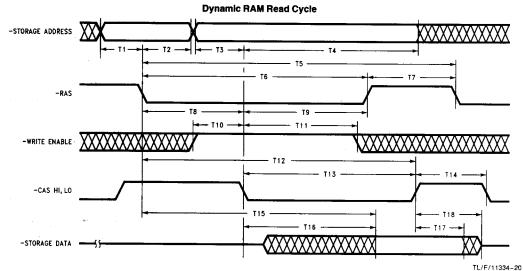

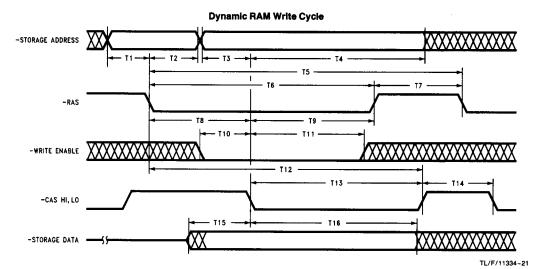

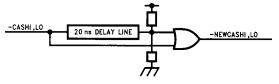

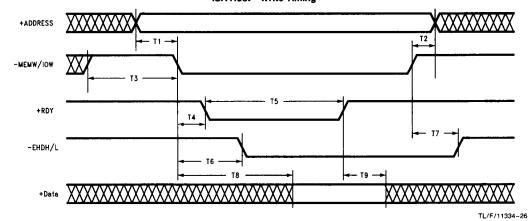

#### SHARED RAM PAGE REGISTER (SRPR)