# TVP9520/25 VIDEO PROCESSING CHIPSET

## Overview

- Supports 8, 16, 24, and 32 bits/pixel

- Supports display resolutions for NTSC/PAL(Overscan/ Underscan), VGA & Enhanced VGA

- Hardware supports scalable full motion video; window clipping functions

- Multiple frame capture and hidden Capture

- Live multi-picture

- VGA/XGA graphics/text overlay

- Advanced chroma keying

- Digital special effects processing (crossfading, linear blending, solarization, etc.)

- Advanced genlock circuit allows overlay from multiple video sources

- Software controlled contrast, brightness, saturation and hue

- Supports interlaced input and interlaced or noninterlaced output; programmable sync polarity

- Supports up to 4MB of 256Kx4 or 256Kx8 enhanced page mode VRAM. Minimum memory configuration is four 256Kx4 or two 256Kx8 VRAMs

- Displayable memory maps of 512x512, 512x1024, 1024x512, and 1024x1024

- TARGA+® register compatible

- Compatible with ISA, EISA, and MCA bus

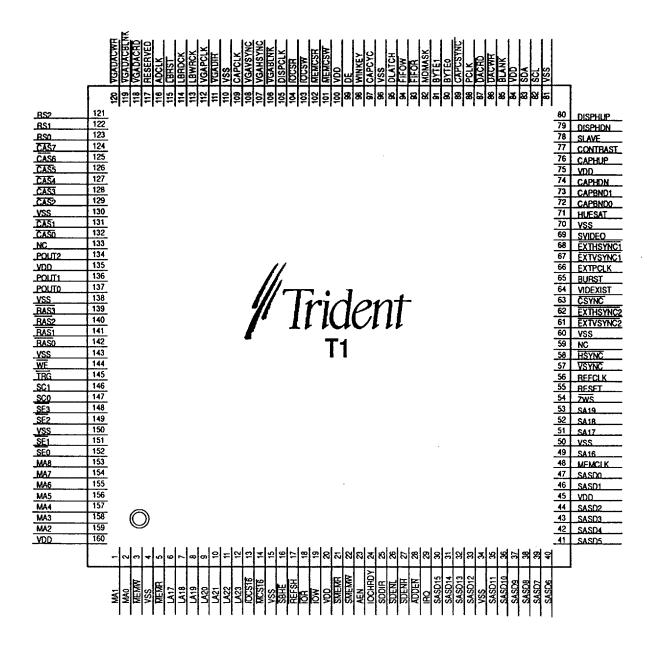

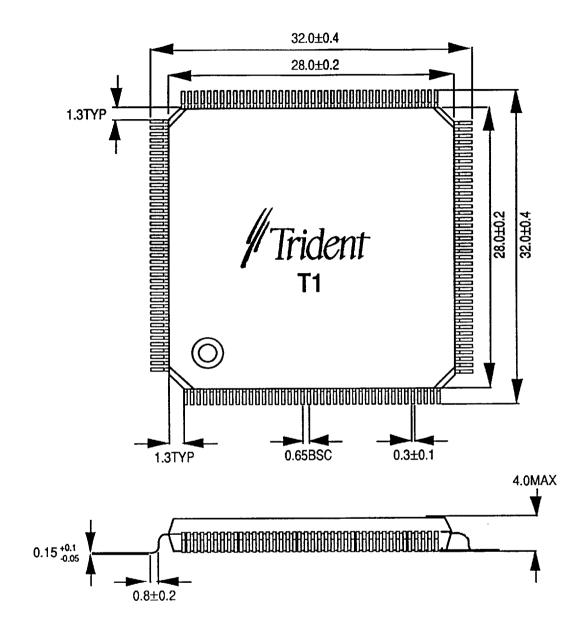

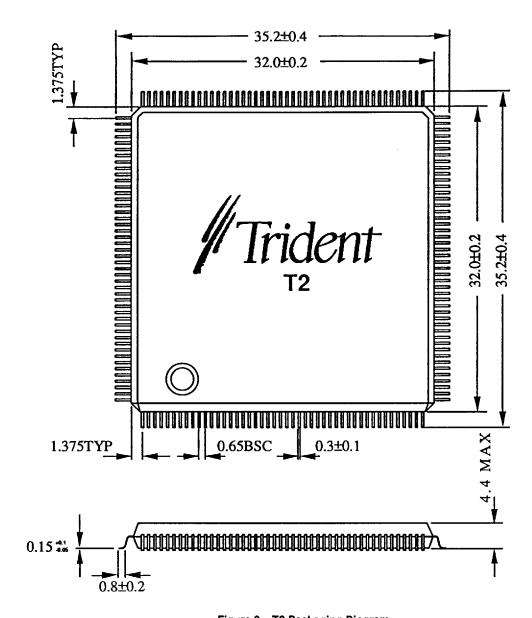

- T1 160 Pin PQFP; T2 184 Pin PQFP Package

## **General Description**

Trident's TVP9520/25 Video Processing Chipset offers scalable full motion video windowing, multiple frame capture, VGA/XGA graphics and text overlay, digital special effects processing, advanced chroma keying and up to 16.7 million displayable colors. TVP9520/25 is the new standard for high quality, cost effective, live video production on the PC desktop.

TVP9520/25 offers advanced proprietary functions and performance beyond its 8, 16, 24, or 32 bits of TARGA+® compatibility. Unique features include enhanced zoom, panning and mosaic, XGA overlay, linear scalable window operations (full screen to single pixel), plus the ability to perform real-time overlay and special effects.

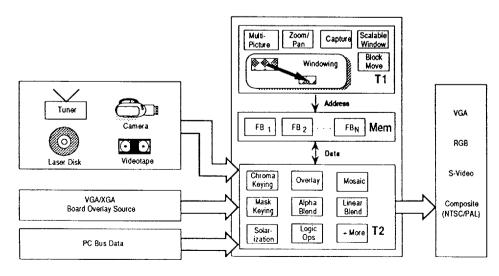

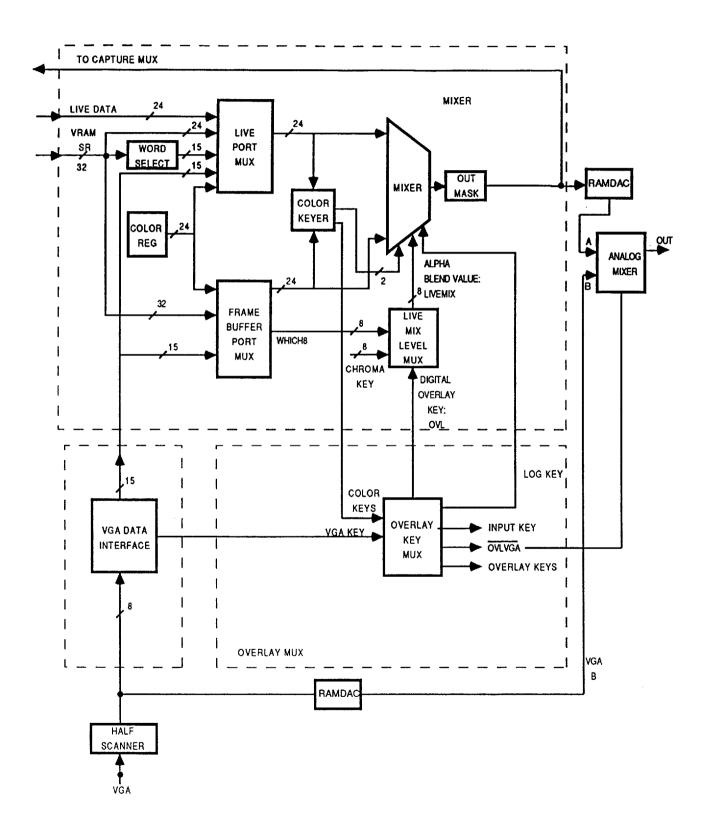

TVP9520/25 can combine VGA/XGA text and graphics with input from one of two software selectable sources, such as video camera, laser disk, VCR, TV tuner, RGB Camera, or one of two frame buffer images. It can then be output to a VGA monitor, TV monitor, projection TV or recorded to videotape. Figure 1 is a high level TVP9520/25 functional flow diagram.

Figure 1. TVP9520/25 Functional Flow Diagram

### TVP9520/25 DATA SHEET

# **Functional Block Description**

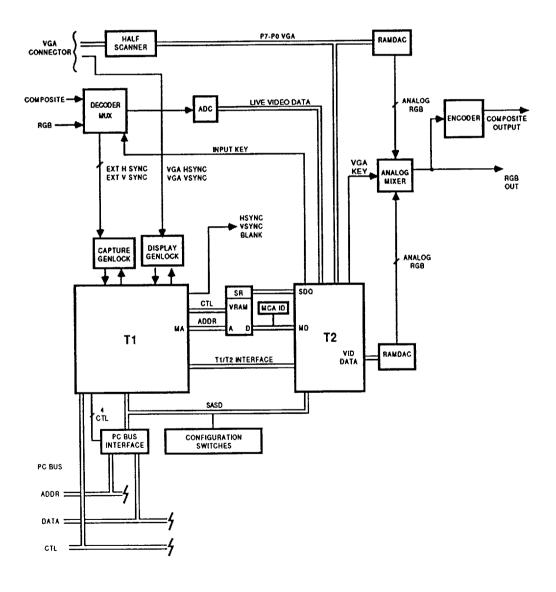

TVP9520/25 chipset consists of two VLSI ASICs: T1 and T2. Figure 2 shows their application in a typical board design.

The TVP9520/25 chipset can be used with ISA or EISA bus PCs (PC/AT) or with Micro Channel Adapter

(MCA) bus PCs (PS/2). The chipset is configured at the board level for a bus type using a simple pullup/ pulldown technique described in the next section.

All internal functions and functional blocks in the TVP9520/25 chipset are controlled through a set of internal registers which are accessed through the PC's I/O space. The TVP9520/25 register set is a superset of the Truevision TARGA+® register set.

Figure 2. TVP9520/25 Chipset Application Diagram

### P 9 5 2 2 5 D A

### T1

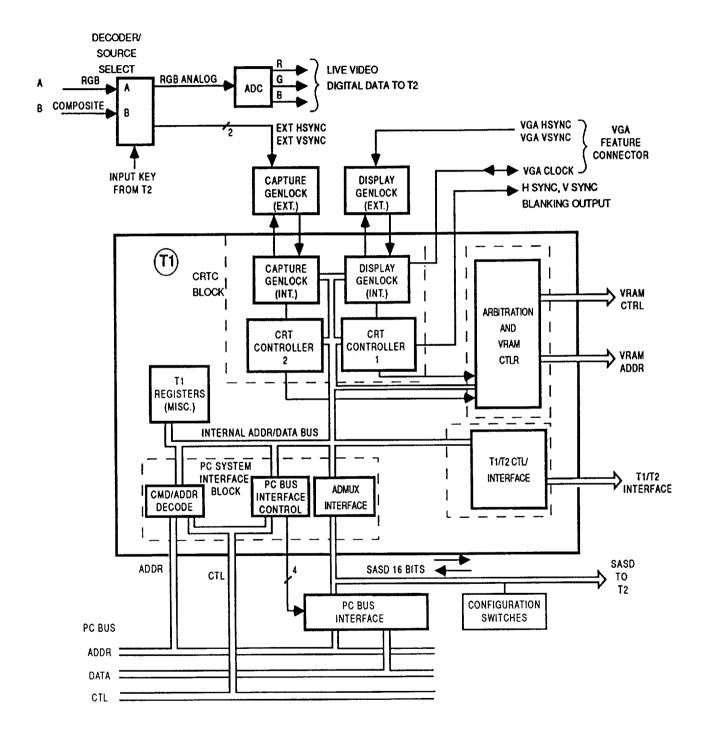

T1's main functional blocks, shown in Figure 3, are the PC System Interface, the CRT Controller (CRTC), the Arbitration and VRAM Controller, and T1/T2 Control/Interface block.

### PC System Interface

The PC System Interface functional block in T1 has three elements: (1) Command/Address Decoder, (2) the PC Bus Interface Controller, and (3) the T1 ADMUX Interface.

### Command/Address Decoder

The Command/Address Decoder analyzes PC bus address and control signals and generates TVP9520/ 25 internal control signals. The decoder has five multifunction pins which can be connected to either AT bus signals or MCA bus signals. The function of the pins is determined by the bus type for which T1 has been configured. (See later section, Configuring the TVP9520/25 Chipset).

### PC Bus Interface Controller

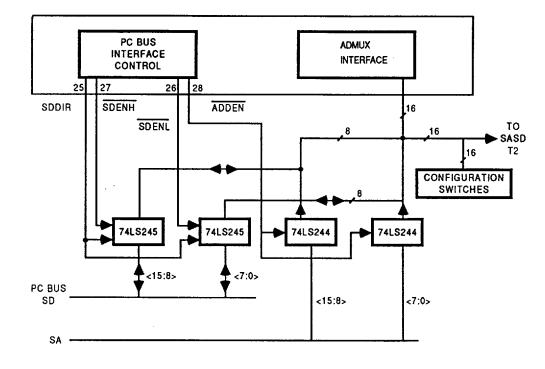

The TVP9520/25 chipset is designed to communicate with the PC bus through external components in a PC Bus Interface that multiplexes 16 address bits and 16 data bits between the PC system bus and TVP9520/ 25's inter-chip 16 bit SASD bus. Typically, only four chips are needed for the PC Bus Interface: two address buffers and two bidirectional data buffers. As shown in Figure 5, the PC Bus Interface Controller provides four signals needed to control these external interface components.

On both T1 and T2 is an interface (ADMUX interface) that handles and synchronizes flow of multiplexed data between the chip's internal address/data bus and the external interchip SASD bus. In addition, T1's ADMUX interface supports auto-configuration by reading the logic status of SASD bus lines immediately after reset and providing the values to the SYSCONFIG register where they are latched. (Reference Configuring the TVP9520/25 Chipset section).

### **CRT Controller (CRTC)**

The CRT Controller block provides display and video input handling functions including genlocking. It generates all necessary timing and control signals, including equalization and serration, and provides horizontal sync, vertical sync, blanking, and composite sync outputs. It also handles synchronization with outside video sources so that TVP9520/25 images may be merged with display information from a seperate VGA or XGA board.

In TARGA+® mode, the CRTC1 provides TARGA+® control functions. In this mode, CRTC1 is used for all video input and display timing functions.

In Trident mode, the CRTC block provides separate controllers for capture and display, and allows use of two separate timebases. Each controller has its own genlock circuitry which interfaces with a minimal number of external components to form a complete genlock subsystem. CRTC2's genlock handles inputs separately and independently from CRTC1's genlock, which provides pixel clocks for use with a VGA or XGA board or outside video sources.

TVP9520/25's two independent CRTCs allow operation in a variety of genlock and scanning modes. For compatibility, TVP9520/25 provides TARGA® and TARGA+® genlock and scan modes, which use a single timebase. However, TVP9520/25 Trident modes offer enhanced operation with dual timebases for more complex applications. For example, interlaced input may be handled while non-interlaced video is output.

### Arbitration and VRAM Controller

The Arbitration unit handles prioritization and arbitration of memory requests. It controls operations such as refresh, CPU requests, access to memory for video capture, block move, and window operations.

The VRAM Controller unit provides the basic control signals needed by VRAM, such as RAS, CAS, and WE. The Controller also generates VRAM addressing for memory access, display under various display modes, and windowing. It controls memory data transfers between VRAM and T2. It supports up to 4MB of memory without an external decoder.

Figure 3. T1 Functional Block Diagram

### T1/T2 Control/Interface

This functional block manages the T1/T2 control/ interface bus.

### **T2**

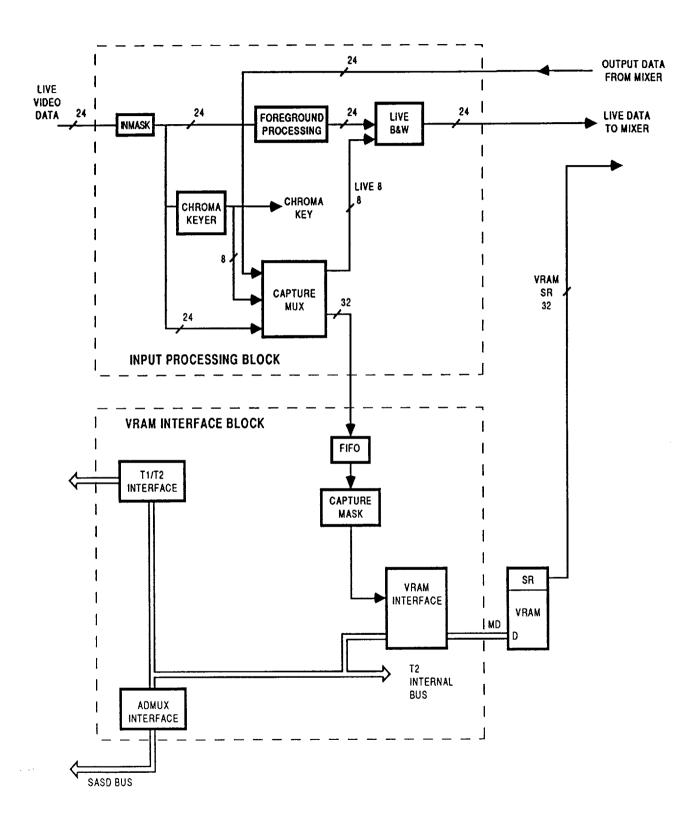

The main functional blocks of T2, shown in Figures 4a & 4b, are the Input Processing block, the VRAM Interface block, the Mixer, the Overlay Controller, and the VGA Interface.

### Input Processing

This block contains a live data input mask, a foreground processor used in blue channel processing, a chroma keyer, the capture data channel multiplexer, and a processor for creation of monochrome data from color data.

### **VRAM** Interface

The VRAM Interface block contains interfaces for the interchip buses, a FIFO for data from the capture mux, a capture data mask, and a VRAM interface that routes data to/from the random-access part of the VRAM, and which also contains a mask (NEWMASK) usable with the VRAM data path.

### Mixer Block

The Mixer provides a variety of pixel data manipulation functions. Its elements support 8, 16, 24, and 32 bit pixel operations including linear blending, alpha blending, logic operations, scalable full motion video, and many more features. All TARGA+® functions are supported.

For additional information on digital special effects, see Detailed Chipset Feature Information on later pages.

### Overlay Controller

The Overlay Controller provides control for an external analog output signal mixer. It supports a wide range of advanced forms of keying, including: keying between two sources, chroma keying, luminance keying, keying on a bitplane, and VGA overlay. Chromakeying may be based on a single color, blue channel data, or a color range. TVP9520/25's advanced chroma processing allows shadows against a blue background to be preserved. The Overlay Controller supports using VGA overlay functions with other forms of keying; this allows many combinations of live video, frame buffer data, and VGA/XGA graphics (from a separate VGA/XGA board).

### **VGA** Interface

The VGA Interface in T2 handles data input from a separate VGA or XGA board. It provides VGA keying control to the Overlay Controller.

Figure 4a. T2 Functional Block Diagram

Figure 4b. T2 Functional Block Diagram

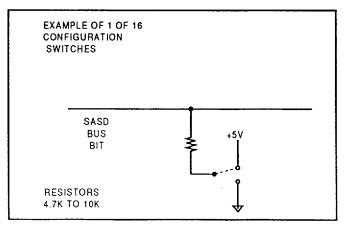

# Configuring the TVP9520/25

Board-level configuration of the TVP9520/25 chipset is performed using a simple technique, illustrated in Figure 5. There are 10 board-level configuration parameters, each mapped to a bit on the SASD bus. A parameter is configured by connecting the bit to which it is mapped either high or low through a 4.7K to 10K pullup or pulldown resistor. This does not affect normal bus activity, but furnishes a logic state that can be read at initialization time. After reset, the SYSCONFIG register reads and latches the state of each SASD bus bit. The bit values are then used by T1 and T2 to determine required configuration. The SYSCONFIG register can also be read by software, providing a means for applications to determine board configuration.

**Table 1. Board-Level Configuration Parameters**

| · · · · · · · · · · · · · · · · · · · | SASD  |                                                                               |

|---------------------------------------|-------|-------------------------------------------------------------------------------|

| NAME                                  | BIT#  | DESCRIPTION                                                                   |

| cio                                   | 15    | contiguous or non-contiguous I/O address.  0 = non-contiguous; 1 = contiguous |

| baseIO                                | 14:12 | these three bits set base I/O address                                         |

| busSize                               | 11    | 0 = 8-bit slot; $1 = 16$ -bit slot                                            |

| AT/MCA                                | 10    | 0 = MCA bus; $1 = AT$ bus                                                     |

| testconf                              | 9     | Set this bit = 1 for normal use                                               |

| switch                                | 8     | General purpose input                                                         |

| biosEnb                               | 7     | 0 = enable BIOS; 1 = disable BIOS<br>(default)                                |

| biosSize                              | 6:5   | Value of bits 6 and 5 selects BIOS size of 4K, 8K, 16K, or 32K                |

| biosBase                              | 4     | Sets BIOS base address of 0C000H or 0D000H                                    |

| biosStart                             | 3:0   | Bits 3-0 set BIOS starting address                                            |

The board-level parameters and SASD bit values are readable as corresponding bits in the SYSCONFIG register (index 59H). For more information, see TVP9520/25 Technical Reference Manual.

## Configuring for AT Bus

1. Set the AT/MCA bit=1 with a pullup on SASD bus bit 10. This causes the following pins of T1 to assume the functions listed in Table 2:

Table 2. AT Bus Configuration

| T1 PIN# | AT BUS FUNCTION |  |

|---------|-----------------|--|

| 5       | MEMR            |  |

| 3       | MEMW            |  |

| 18      | ĪŌR             |  |

| 19      | <del>IOW</del>  |  |

| 23      | AEN             |  |

## Configuring for MCA Bus

1. Set the AT/MCA bit = 0 with a pulldown on SASD bit 10. This causes the following pins of T1 to assume the functions listed in Table 3:

Table 3. MCA Bus Configuration

| T1 PIN# | MCA BUS FUNCTION                 |  |

|---------|----------------------------------|--|

| 5       | M/IO                             |  |

| 3       | <u>50</u>                        |  |

| 18      | M/IO<br><u>\$0</u><br><u>\$1</u> |  |

| 19      | <u>CMD</u>                       |  |

| 23      | CDSETUP                          |  |

2. For Micro Channel applications, TVP9520/25 supports MCA auto-configuration card IDs, which are four-byte values. When a card is enabled for an ID read by CDSETUP, the PC may read the contents of I/O byte registers at 101H and 100H.

The high order four bits of register 101H are hardwired with a value of 8 (the first nibble of a video device ID). The low order nibble of register 101H and the byte in register 100H may be configured by using pullups/

pulldowns as described before, but in this case by placing them on the data bus lines <MD11:MD0> which connect T2 and VRAM.

For example:

to set card ID: 80CFH or 1000 0000 1100 1111 --- MSB-- --- LSB--

set register  $101 = 80H = 1000\ 0000$ set register  $100 = CFH = 1100\ 1111$  This is done by wiring pullups/pulldowns on the MD bus lines as follows:

<MD15:MD12>= pullups are already internally hardwired inside T2 to value of 8; no external configuration is needed.

<MD11:MD8> =0 0 0 0 pulldown all bits <MD7:MD4> =1 1 0 0 pullup <MD7:MD4> pulldown <MD5:MD4> <MD3:MD0> =1 1 1 1 pullup all bits

<MD3:MD0>

Figure 5. Board Level Configuration Of TVP9520/25 Chipset

### Н

# **Pixel Depth**

Table 4 lists the pixel depths and associated colors available for the TVP9520/25.

**Table 4. Pixel Depth Information**

| Depth         | Color                                                              |

|---------------|--------------------------------------------------------------------|

| 8 bits/pixel  | 256                                                                |

| 16 bits/pixel | 32,768 (five bits each R, G, B; one overlay bit)                   |

| 24 bits/pixel | 16,777,216 (eight bits each R, G, B)                               |

| 32 bits/pixel | 16,777,216 (eight bits each R, G, B plus eight bits alpha channel) |

# **Display Resolution**

Table 5 lists typical display resolutions available. All may be converted to non-interlaced display.

**Table 5. Display Resolution**

| Output Format  | Resolution x<br>Bits/Pixel | Minimum<br>Memory |

|----------------|----------------------------|-------------------|

| NTSC Underscan | 512x400x16                 | 512K              |

|                | 512x400x32                 | 1MB               |

|                | 640x480x16                 | 1MB               |

|                | 640x480x32                 | 2MB               |

| NTSC Overscan  | 512x486x16                 | 512K              |

|                | 512x486x32                 | 1MB               |

|                | 648x486x16                 | 1MB               |

|                | 720x486x16                 | 1MB               |

|                | 756x486x16                 | 1MB               |

| PAL Underscan  | 512x476x16                 | 512K              |

|                | 512x476x32                 | 1MB               |

|                | 720x576x16                 | 2MB               |

| PAL Overscan   | 512x576x32                 | 2MB               |

|                | 768x576x16                 | 2MB               |

| VGA Compatible | 512x400x16                 | 512K              |

| -              | 512x496x16                 | 512K              |

|                | 640x400x16                 | 1MB               |

|                | 640x496x16                 | 1MB               |

| Enhanced VGA   | 800x600x16                 | 2MB               |

| Compatible     | 1024x768x16                | 2MB               |

# TVP9520/25 Applications

The TVP9520/25 can be used in the following applications:

- Animation

- Titling

- Inspection

- Security

- Advertising

- · Image Database

- · Desktop Publishing

- Home Video Production

- · Business Presentation

- · Medical Imaging

- · Video Training

- Military Applications

- · Computer-Aided Instruction and Training

## **Design Kits**

A design kit is available for RGB in-out board with S-Video PAL, NTSC daughter boards. Boards based on the Philips digital TV chipset are also available.

## **Detailed Chipset Feature**

### Video Windowing

- Provides source and destination capture windows. The destination window may be scaled linearly to pixel boundaries. Window locations can be defined arbitrarily.

- Provides two programmable CPU hardware windows (x,y independent). The windows may be programmed as read or write. Real time Multiple 90-degree rotation and mirror rotation effects available. Windows are bit maskable.

- · Supports mixer effects within a window

### Frame Capture

- •Capture multiple frames

- Location and size programmable

- Live input video capture is independent of what is displayed on screen

- ·Overlay results may be captured

- Hidden capture live images may be captured in a frame buffer while another captured image is displayed on-screen

- In real mode, pixels in the frame buffer can be accessed through either of two page windows (4K, 8K, 16K, or 32K). In protected mode, memory can be mapped outside the first 1MB system memory for direct access.

### VGA Overlay

- Overlay live video, with two frame buffers and VGA/XGA (can all be simultaneously displayed on a single screen)

- Digital wipe effects between live display and frame buffers

- Overlay video input in background or foreground

- Built-in 1, 2 or 8 bit overlay or alpha channel

### Chroma Keying

- Multiple simultaneous chroma key sources for video and VGA/XGA

- · Chroma key based on a color range

- · Chroma key based on a fixed color

- Chroma key based on blue component of live input

- Preserves shadows during chroma keying

### Digital Special Effects

- Selectable border color or background color via R, G, B color registers

- Linear minifying (or shrinking) of live video and captured frames. Size and location programmable. Mirror effect and real time trailing effects available.

- •Realtime inverse video (complement of selected pixels).

- •Offers color filter to generate real time effects between live/frame buffer, two frame buffers, live and fixed pattern.

- •Zoom. Pixels on the selected screen area enlarged by the given X and Y zoom factors(1X to 64X). X and Y axis processing is independent.

- Mosaic. Mosaic quantizes an image into blocks of size on an axis of (resolution divided by mosaic factor on that axis of 1X to 64X). X and Y axis processing is independent. Also known as tile effect.

- Panning. Move displayed image area along X and (or) Y axis on pixel boundaries. X and Y axis independent.

- •Real-time logic operations (AND, OR, NOR, etc.) between live video and frame buffer

- •Transparency effect. Places a user defined transparency mask shape of a given color or color range over an image

- •Solarization. Reduces the color shades in a given image. Three hardware masks are provided: CPU, Capture and Display. Color reduction performed through a color mask.

- Multiple screens. Supports hidden capture, screen swap, fading effects, etc.

- •Live multi-picture. Multiple versions of a live image or portion of the live image frame buffer are displayed on screen

- •Pseudo color. Convert given color index to a different RGB color via RAMDAC Color Look Up Table (CLUT)

- Linear blending. 256 levels. Two sources. Levels may be chosen in software or with alpha channel. For software method, the same value is used for entire image. For alpha channel method, blending level is defined on a pixel by pixel basis.

- Smooth crossfading. 256 levels. Fade in and out between two sources. Same method for choosing levels as linear blending.

- High speed block move between programmable CPU hardware windows

- VGA/XGA pass through and overlay

### TVP9520/25 DATA SHEET

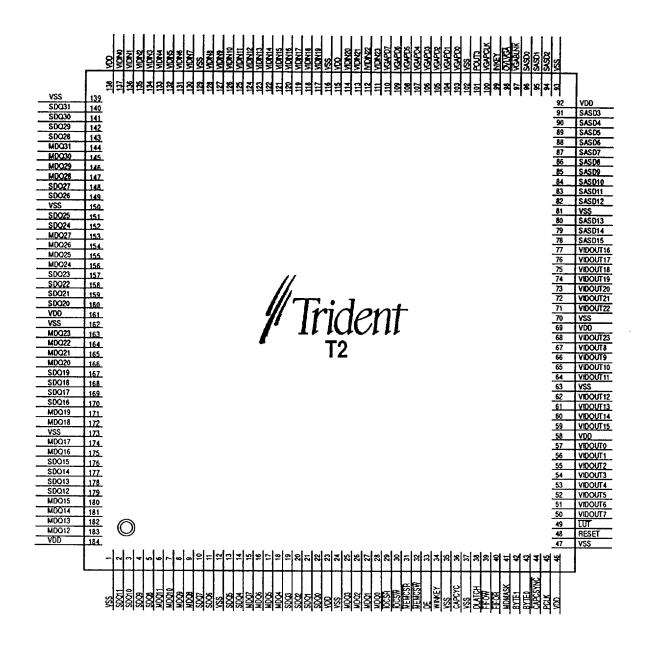

Figure 6. T1 Pinout Diagram

Figure 7. T2 Pinout Diagram

Table 6. T1 Pin Description

| Pin Type | Pin Number        | Descript                                                                                                                             | ion                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| e        |                   |                                                                                                                                      |                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| nals     |                   |                                                                                                                                      |                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| I        | 5                 |                                                                                                                                      |                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | AT bus. Signal used during a memory read<br>eo processing board drive data onto the bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| I        | 3                 | Memory write strobe for AT bus. Signal used during a memory write cycle to request the video processing board accept the data on the |                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| I        | 18                | I/O read                                                                                                                             | strobe                                                                                                                                                                                                                                                                               | for AT I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bus. Signal used during an I/O read cycle to ssing board drive data onto the bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| I        | 19                | I/O writ                                                                                                                             | e strob                                                                                                                                                                                                                                                                              | e for AT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bus. Signal used during an I/O write cycle to sing board accept the data on the system data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| I        | 23                |                                                                                                                                      | enable                                                                                                                                                                                                                                                                               | e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0        | 24                | Logical                                                                                                                              | 0 info                                                                                                                                                                                                                                                                               | rms CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | nnected to IOCHRDY signal on AT Bus.<br>that a memory operation is in progress and<br>it states are required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| I        | 21                | ality as                                                                                                                             | MEMI                                                                                                                                                                                                                                                                                 | ₹, except                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | robe for AT bus. Signal has same functionit is active only within the first 1MB of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| I        | 22                | System ality as                                                                                                                      | memoi<br>MEM\                                                                                                                                                                                                                                                                        | ry write s<br>W, except                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | trobe for AT bus. Signal has same function-<br>t it is active only within the first 1MB of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Signals  |                   | ·                                                                                                                                    |                                                                                                                                                                                                                                                                                      | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| I/O      | 5                 | memory                                                                                                                               | y cycle                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | y cycle or I/O cycle. A logical 1 indicates a gress. A logical 0 indicates an I/O cycle is in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| I        | 18, 3             | The log<br>M/IO, i                                                                                                                   | ical va<br>ndicate                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0 and \$1, along with the logical value of of a Microchannel bus cycle. Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|          |                   | M/IO                                                                                                                                 | $\overline{S0}$                                                                                                                                                                                                                                                                      | <u>\$1</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|          |                   | 0                                                                                                                                    | 0                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Reserved<br>I/O Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|          |                   | <del>-</del>                                                                                                                         | _                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | I/O Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |                   |                                                                                                                                      | _                                                                                                                                                                                                                                                                                    | =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |                   | =                                                                                                                                    | -                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |                   | _                                                                                                                                    | _                                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Memory Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          |                   | 1                                                                                                                                    | l<br>t                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Memory Read<br>Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          | <del> </del>      | 1                                                                                                                                    | l .                                                                                                                                                                                                                                                                                  | <u>.</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| τ        | 10                | C                                                                                                                                    | * 1                                                                                                                                                                                                                                                                                  | CN(D) =:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | not on Mioro Channel bus. Cissal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| I        | 19                |                                                                                                                                      |                                                                                                                                                                                                                                                                                      | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | nal on Micro Channel bus. Signal used to information valid. For write operations, data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          | I I I Signals I/O | I 5 I 3 I 18 I 19 I 23 O 24 I 21 I 22 Signals I/O 5                                                                                  | I 5 Memory cycle to system I 18 I/O reach request lines. I 19 I/O write request lines. I 23 Address O 24 Open de Logical that address system I 21 System ality as system I 22 System ality as system Signals I/O 5 M/IO in memory progress I 18, 3 The log M/IO, it table be served. | I 5 Memory read socycle to request I 3 Memory write cycle to request system data lir I 18 I/O read strobe request the vidines.  I 19 I/O write strobe request the vidines.  I 23 Address enable O 24 Open drain ou Logical 0 inform that additional I 21 System memorality as MEMI system address.  I 22 System memorality as MEMI system address.  Signals  I/O 5 M/IO indicate memory cycle progress.  I 18, 3 The logical van M/IO, indicate table below.  M/IO SO  O 0 O 0 O 1 O 1 O 1 O 1 | I 5 Memory read strobe for cycle to request the vide of cycle to request the vide system data lines.  I 18 I/O read strobe for AT request the video proces lines.  I 19 I/O write strobe for AT request the video proces lines.  I 23 Address enable  O 24 Open drain output. Con Logical 0 informs CPU that additional CPU was ality as MEMR, except system address space.  I 22 System memory read strobe for AT request the video proces lines.  I 21 System memory read strobe for AT request the video proces lines.  I 22 System memory read strobe for AT request the video proces lines.  I 22 System memory read strobe for AT request the video proces lines.  I 21 System memory read strobe for AT request the video proces lines.  I 22 System memory read strobe for AT request the video proces lines.  I 1 23 Address enable  O 24 Open drain output. Con Logical 0 informs CPU was ality as MEMR, except system address space.  I 22 System memory write sality as MEMW, except system address space.  Signals  I/O 5 M/IO indicates memory memory cycle is in progregress.  I 18, 3 The logical values of Si M/IO, indicate the start table below.  M/IO SO SI II  O 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 |

Table 6. T1 Pin Description-Continued

| Pin          | Pin Type    | Pin Number             | Description                                                                                                                                                                                                                                                              |  |  |

|--------------|-------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|              | -           |                        | is valid after the leading edge of $\overline{CMD}$ but before the trailing edge of $\overline{CMD}$ . Tri-state output.                                                                                                                                                 |  |  |

| CD SETUP     | I           | 23                     | This signal is driven active during the system configuration period When activated, the signal is used to obtain the ID and configuration data of an adapter located in the specified Micro Channel slot.                                                                |  |  |

| CD CHRDY     | 0           | 24                     | Channel Ready signal. A logical 0 informs CPU that a memory or I/O operation is in progress and that additional CPU wait states are required.                                                                                                                            |  |  |

| c. Common Bu | s Signals I | For AT & MCA           |                                                                                                                                                                                                                                                                          |  |  |

| RESET        | I           | 55                     | System reset (active high). At the falling edge of Reset configuration information is latched to the internal TVP9520/25 registers (SYSCONFIG (Index=59h) and Micro Channel ID register). The information is carried on SASD15-SASD0 & MD11-MD0 during the reset period. |  |  |