# Vero Component Specification Version 2.0.1

Document Number BOC-CS-08943

April 18, 1995

Contact: Robert Eng Owner: G. C. Keller

Co-Processor Hardware Development Dept. 22U Internal Zip 2111 Boca Raton

Unclassified

# **Preface**

This document describes the functions of the Vero VLSI component. The main intention of this chip is to provide an efficient means of interfacing several relatively slow serial communication chips to a high-speed bursting CFE bus. This is done through a dual-bus structure, eight independent DMA channels, linked-list chaining and automatic appended I/O operations.

#### **Comments**

Any comments and/or suggestions should be directed to Robert Eng.

# **Acknowledgements**

This document would not have been possible without the help of:

Jay Ackerman, Serafin Garcia, Gary Hoch, Toan Pham and Eric Stelzer.

## **Revisions**

- 01-22-91 to 03-07-91. Original input to the document.

- 03-14-91 to 04-09-91. Version 0.2.2 updates.

- Added address parity checking to Local Bus

- New definition for Burst Last signal

- New definition for Exception signal

- New AIB Data Steering table

- New AIB Ready signal definition

- New AIB Detect signal definition

- New AIB Clock signal definition

- Added Local Bus Exception to Miami sourced interrupts

- Added Local Bus Exception to Brighton sourced interrupts

- Rearranged Brighton interrupt table

- Added Local Bus Configuration register

- Added full 64KB DMA byte count capability

- Rearranged TQC, MPR, and CPR in CDT register map

- Added restriction to usage of DCCR and GDCR channel enable command

- Changed buffer queuing to allow 4K-1 buffers instead of 4K

- Corrected Queuing flow example

- Added 2 Local Bus input interrupt signals

- Added a high priority AIB interrupt input

- Changed interrupt vector assignments

- Added Interrupt Status register

- Added bits to AIB Command/Status register

- Added AIB presence detect bit to PDR

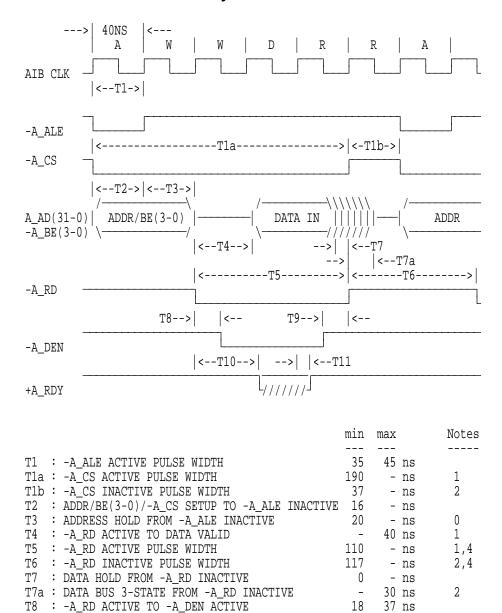

- Changed AIB Slave Read and Write cycles to drive Chip Select sooner

- 08-01-91 to 08-23-91. Version 0.3 updates.

- Changed to Toshiba technology VLSI

- Changed ground to power pin ratio

- Added AIB wrap capability

- Added AIB Wrap Enable signal

- Changed AIB INT signal description

- Rearranged Brighton interrupt code table

- Changed signal description for all LSSD test pins

- Added Local Bus Exception and AIB Bus parity status to DISR

- Added gate array ID and queuing enable/disable function to LBCR

- Rearranged Interrupt vector assignments

- Removed generic RHPI and EOI functions of interrupt controller

- Added AIB INT0 EOI command

- Added AIB INT1 EOI command

- Added wrap buffer enable and wrap mode bits to ACSR

- Added AIB Wrap Control register

- Added AIB Wrap Address/Data register

- 09-01-91 to 01-24-91. Version 0.4 updates.

- Changed format of document to Bookmaster.

- Changed signal description section to table format.

- Changed timings to reflect 25MHz performance.

- Changed timings for AIB Bus (no revision code used here)

- Added Pin name/Pin number cross reference appendix.

- Added Local Bus Timing appendix.

- Added ICT I/O Mapping appendix.

- 02-11-92 to 04-08-92. Version 0.4.1 updates.

- Removed revision code 1, 2, and 3 from document.

- Changed Queue Tail Pointer register to 'read only' in 1.7, "Vero Register Address Map" on page 19.

- Changed Interrupt Status register to 'read only' in 1.7, "Vero Register Address Map" on page 19.

- Added Bit 31 in 2.2.1, "Channel Control Register (CCR)" on page 23.

- Updated definition of Bit 0 (enable/disable) in 2.2.1, "Channel Control Register (CCR)" on page 23.

- Clarified definition of GDCR stop command in 2.2.3, "Global DMA Command Register (GDCR)" on page 27.

- Updated Queue Count initialization requirements in 2.2.5, "Transfer/Queue Count Register (TQC)" on page 29.

- Changed QTP to 'read only' in 2.2.10, "Queue Tail Pointer Register (QTP)" on page 33.

- Added Section 2.3.1, "Linked List Chaining/Stopping Matrix" on page 35.

- Added more description in 2.4, "Queuing Operation (NOT Supported)" on page 36.

- Changed DISR to 'read only' in 2.5.1, "DMA Interrupt Status Registers (DISR)" on page 40.

- Changed Queue underrun status bit definition in 2.5.1, "DMA Interrupt Status Registers (DISR)" on page 40.

- Changed bit names to QE and PE in 2.6.2, "Local Bus Configuration register (LBCR)" on page 42.

- Changed polarity of queuing enable bit in 2.6.2, "Local Bus Configuration register (LBCR)" on page 42.

- Changed polarity of LED enable value in 5.1.2, "LED Enable Register (LER)" on page 62.

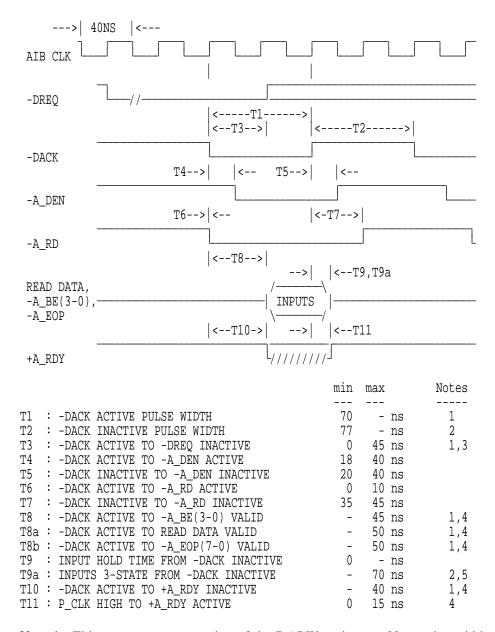

- Changed T7 min to 0ns in B.2.1, "AIB Slave Read Cycle" on page 72.

- Changed T7 min to 0ns in B.2.3, "AIB Interrupt Acknowledge Cycle" on page 76.

- Documented Local Bus timings for CFE incompatibility in Appendix C, "Local Bus Timings" on page 79.

- March 17, 1993. Version 1.1.0 updates.

- Note that Version 1.0.0 was never formally released

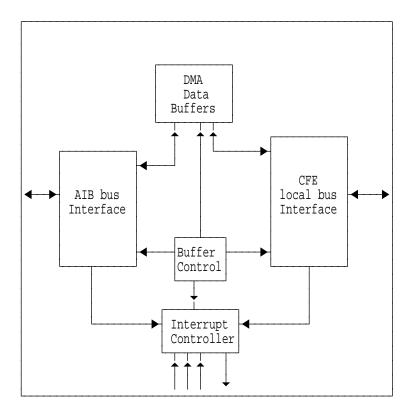

- added block diagram (Figure 1 on page 12)

- changed local bus signal name L\_PAR to L\_ADP (for consistency with Miami and Brighton)

- removed A\_RDY support during DMA

- removed AIB wrap support

- clarified A\_DETECT use

- clarified Brighton and Miami interrupt pins

- added secondary address select

- removed TC followed by EOP support

- corrected conflicting AIB OP information

- clarified when writing QR causes interrupt

- removed APR bit from ACSR

- removed DFCR register (had no function)

- clarified use of PDR

- the RESET COMMAND values are in the process of being verified and should not be relied upon

- July 15, 1993. Version 2.0.0 updates.

- Clarified XINT bus is active low

- Clarified present dectect bits are non-inverted

- Clarified Queue Pointer Address in QR is invalid when read

- Indicated Queueing is not supported

- Changed RESET COMMAND values

- Changed CS active and inactive pulse width values

- Clarified the use of bit 31 and bit 0 of CCR

- Added active time for -A\_RESET signal

- Changed max DMA byte count from '64kb' to '64kb-1'

- April 18, 1995. Version 2.0.1 updates.

- Declassified document.

- Changed contact person to Robert Eng.

- Reworded note not to write zero DMA byte count and to initialize DMA byte count for all DMA channels; added note to linked list chaining description not to write zero DMA byte count.

- Added Electrical Characteristics section to Appendix (temperature, power, voltage).

- Added Packaging section to Appendix.

# Contents

| 1.0 Vero Component Overview                              |   |

|----------------------------------------------------------|---|

| 1.1 General                                              |   |

| 1.2 RAS Highlights                                       |   |

| 1.3 Performance                                          |   |

| 1.4 Sustained Throughput                                 |   |

| 1.5 Vero Block Diagram                                   |   |

| 1.6 Vero Signal Description                              |   |

| 1.6.1 Vero Local Bus Signals (CFE Bus)                   |   |

| 1.6.2 Vero AIB Bus Signals                               |   |

| 1.6.3 Vero Interrupt Controller Signals                  |   |

| 1.6.4 Vero Miscellaneous Signals                         |   |

| 1.6.5 Vero Clocks and Reset                              |   |

| 1.7 Vero Register Address Map                            |   |

| 1.7.1 Vero Primary and Secondary Address Map Information | 1 |

| 2.0 Vero DMA Controller                                  | 2 |

| 2.1 General                                              |   |

| 2.2 Channel Descriptor Table                             |   |

| 2.2.1 Channel Control Register (CCR)                     |   |

| 2.2.2 DMA Channel Command Registers (DCCR 0-7)           |   |

| 2.2.3 Global DMA Command Register (GDCR)                 |   |

| 2.2.4 Memory Pointer Register (MPR)                      |   |

| 2.2.5 Transfer/Queue Count Register (TQC)                |   |

| 2.2.6 Chain Pointer Register (CPR)                       |   |

| 2.2.7 AIB Address 1/2 Register (AIB_ADDR 1/2)            |   |

| 2.2.8 AIB_OP1 DATA Register (AIB_OP1)                    |   |

| 2.2.9 AIB_OP2 DATA Register (AIB_OP2)                    |   |

| 2.2.10 Queue Tail Pointer Register (QTP)                 |   |

| 2.3 Linked List Chaining (LLC)                           |   |

| 2.3.1 Linked List Chaining/Stopping Matrix               |   |

| 2.4 Queuing Operation (NOT Supported)                    |   |

| 2.4.1 Queuing Register (QR)                              |   |

| 2.4.2 Queuing Status register (QSR)                      |   |

| 2.5 DMA Interrupts                                       |   |

| 2.5.1 DMA Interrupt Status Registers (DISR)              |   |

| 2.6 DMA Miscellaneous Registers                          |   |

| 2.6.1 DMA FIFO Residual Count registers (DFRC0-7)        |   |

| 2.6.2 Local Bus Configuration register (LBCR)            |   |

|                                                          |   |

| 3.0 Vero Interrupt Controller                            |   |

| 3.1 General                                              |   |

| 3.2 Programmable Options                                 |   |

| 3.2.1 Interrupt Initialization register (IIR)            |   |

| 3.2.2 Interrupt Mask register (IMR)                      |   |

| 3.2.3 Interrupt Status register (ISR)                    |   |

| 3.3 Commands                                             |   |

| 3.3.1 AIB INTO End-of-Interrupt (EOI0) command           |   |

| 3.3.2 AIB INTO End-of-Interrupt (EOI1) command           | 5 |

| 4.0 Vero AIB Bus Interface                               | 5 |

| 4.1 General                                              |   |

|                                                          |   |

| 4.1.1 AlB Arbiter                                     |

|-------------------------------------------------------|

| 4.2 AIB Initialization registers                      |

| 4.2.1 Chip Select Definition registers (CSD0-4)       |

| 4.2.2 DMA Acknowledge Pulse Width registers (DAPW0-7) |

| 4.2.3 AIB Command/Status register (ACSR)              |

| 4.2.5 AID Command/Status register (ACSK)              |

| 5.0 Vero Miscellaneous Registers 6                    |

| 5.1.1 Presence Detect Register (PDR)                  |

|                                                       |

| 5.1.2 LED Enable Register (LER)                       |

| Appendix A. Vero Pin Name/Number Cross Reference      |

|                                                       |

| Appendix B. AIB Bus Timings                           |

| B.1 DMA Cycle Timings                                 |

| B.1.1 DMA Read Cycle                                  |

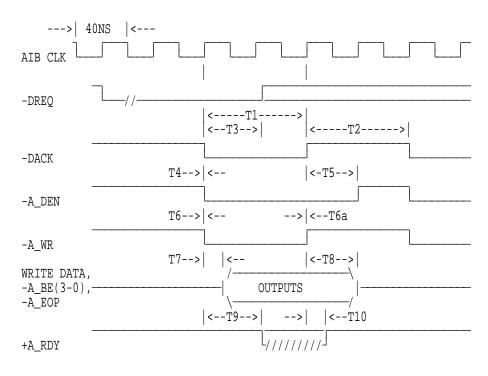

| B.1.2 DMA Write Cycle                                 |

| B.2 AIB Slave Cycle Timings                           |

| B.2.1 AIB Slave Read Cycle                            |

| ·                                                     |

|                                                       |

| B.2.3 AIB Interrupt Acknowledge Cycle 7               |

| Appendix C. Local Bus Timings                         |

| Tippendir Co Escal Bus Timings                        |

| Appendix D. In-Circuit Test I/O Mapping               |

| Tippendia D. In Official Test 1/O Happing             |

| Appendix E. Pre-Assembly Bake Requirement 8           |

| Appendix F. Electrical Characteristics                |

| F.1 D.C. Specifications                               |

| F.1.1 Operating Temperature                           |

| F.1.2 Power Dissipation 9                             |

| F.1.3 Operating Voltage 9                             |

| 1.1.5 Operating voltage                               |

| Annendix G. Packaging                                 |

# **Figures**

| 1.       | Major Functional Blocks in Vero      |

|----------|--------------------------------------|

| 2.       | Linked List Chaining                 |

| 3.       | CCR Chaining/Stopping Matrix         |

| 4.       | Package Information                  |

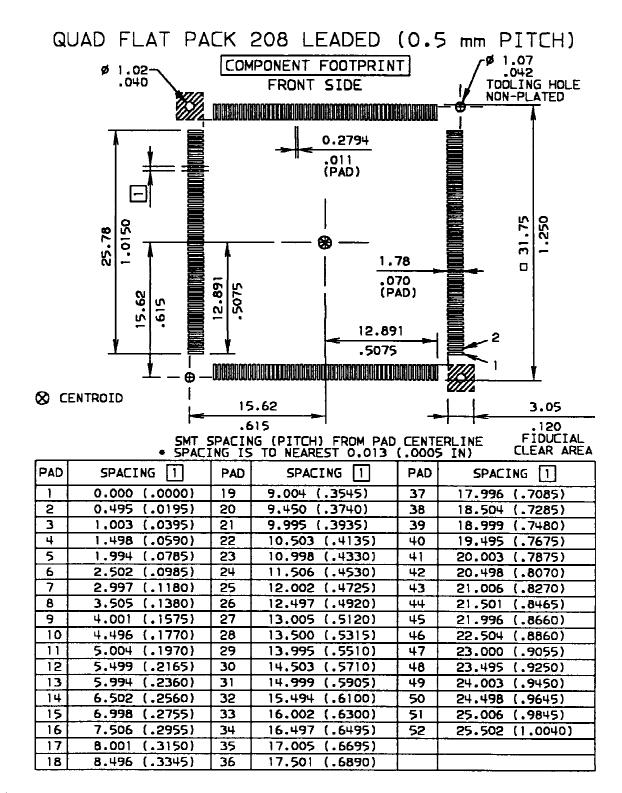

| 5.       | Circuit Board Footprint              |

|          |                                      |

|          |                                      |

| Ta       | bles                                 |

| ıa       | DIES .                               |

| 1.       | Vero Local Bus Signals               |

| 2.       | Vero AIB Bus Signals                 |

| 3.       | Vero Interrupt Controller Signals    |

| 4.       | Vero Miscellaneous Signals           |

| 5.       | Vero Clocks and Reset                |

| 6.       | Vero DMA Registers                   |

| 7.       | Vero Interrupt Registers             |

| 7.<br>8. | Vero AIB Registers                   |

|          |                                      |

| 9.       | Vero Miscellaneous Registers         |

| 10.      | Vero Channel Descriptor Table (CDT)  |

| 11.      | Vero DMA Channel Vector Assignment   |

| 12.      | Vero DMA Channel Vector Assignment   |

| 13.      | Vero Pin Name/Number Cross Reference |

# 1.0 Vero Component Overview

# 1.1 General

The major functions of the Vero module are highlighted below.

- Toshiba (0.8 micron) 12.8mm Semi-custom chip; 278,964 transistors

- 8 channel dual-bus DMA controller

- Common Front End (CFE) Local Bus interface

- Application Interface Bus (AIB bus) interface

- Interrupt controller (80960 expanded mode interrupt support)

- 208 pin PQFP; 174 signal I/O, 25 Ground, 8 Vdd

- 25MHz operation

# 1.2 RAS Highlights

- Address/data parity generation and checking on Local Bus

- Data parity generation and checking on AIB Bus

- · No write only registers

#### 1.3 Performance

The design point of the Vero module is to provide a high performance DMA subsystem for Juno Adapter daughter card designs. In addition, the 80960 support functions of interrupt controller and AIB Bus interface are integrated into the module. The DMA unit is capable of supporting 0 wait state Local Bus accesses for durations of 16-byte bursted transfers. This translates into a peak bandwidth of approximately 57MB/s. In the Juno Adapter implementation however, the Brighton module will induce wait states into Vero's bus cycle that reduce its Local Bus bandwidth capability down to about 33MB/s. This is not to say that Vero can sustain 33MB/s on the Local Bus. Vero's sustained rate on the Local Bus will be a function of other masters such as Miami also accessing the Local Bus.

In addition to being a Local Bus master, the Vero module is also an AIB Bus master for DMA operations. Here, the DMA is capable of running continuous 160ns bus cycles to 4-byte wide devices. This means that for a 4-byte wide device capable of supporting a cycle time of 160ns, a bursted rate of 25MB/s is possible.

# 1.4 Sustained Throughput

The throughput of the Vero chip is dependent on specific AIB implementations. It is intended that AIB's capable of bursted bandwidths of 25MB/s and sustained bandwiths of at least 10MB/s be possible using the Vero module. Other factors, however, can influence the real data throughput of the module. These include:

- · AIB device buffer size

- · Frequency of linked list chaining

- Frequency of DMA executed AIB I/O operations (AIB OP's)

- · Local bus utilization by other master devices

# 1.5 Vero Block Diagram

Figure 1. Major Functional Blocks in Vero

# 1.6 Vero Signal Description

The following tables provide a description of each signal in the Vero module. See Appendix A, "Vero Pin Name/Number Cross Reference" on page 63 for module pin number information.

# 1.6.1 Vero Local Bus Signals (CFE Bus)

| Table 1. Vero Local Bus Signals |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|---------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name                            | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| L_AD(31-0)                      | I/O  | Local Address/Data(31-0) are used for both address generation and data transfer on the Local Bus. The address is driven by Vero when it owns the Local Bus and received otherwise. Data is driven by the device providing the data.                                                                                                                                                                                                                                                                   |  |

| L_ADP(3-0)                      | I/O  | Local Bus Address/Data Parity(3-0) are used to generate and check data parity on the Local Bus.                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| L_W/-R                          | I/O  | Local Write/-Read is used for Local Bus transfers to establish the direction of data flow. This signal is driven when Vero is the Local Bus master and received otherwise.                                                                                                                                                                                                                                                                                                                            |  |

| -L_RDY                          | I/O  | -Local Ready indicates the termination of a data transfer. This signal is driven by Vero as a slave and received when Vero is the Local Bus master.                                                                                                                                                                                                                                                                                                                                                   |  |

| -L_BLAST                        | О    | -Local Burst Last is driven by Vero as a master to indicate the last transfer of a burst access.                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| -L_ADS                          | I/O  | -Local Address Strobe indicates valid address and the start of a new bus access. This signal is driven by Vero as a master and received by Vero as a slave.                                                                                                                                                                                                                                                                                                                                           |  |

| -L_BE(3-0)                      | I/O  | <b>-Local Byte Enables(3-0)</b> select which of the four bytes addressed are active during an access. These signals are driven by Vero as a master and received by Vero as a slave.                                                                                                                                                                                                                                                                                                                   |  |

| -L_REQ                          | О    | <b>-Local Bus Request</b> is driven by Vero to request use of the Local Bus for transfers to and from the Vero DMA channels.                                                                                                                                                                                                                                                                                                                                                                          |  |

| -L_GRANT                        | I    | -Local Bus Grant is received by Vero to detect that a Vero bus request has been granted.                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| -L_EXCPT                        | I/O  | -Local Exception is received by Vero when it is the Local Bus master if the slave detects a critical error, ie. Local Bus parity error. Vero will halt the current transfer and post an interrupt in the appropriate DMA interrupt status register (see 2.5.1, "DMA Interrupt Status Registers (DISR)" on page 40). As a slave on the Local Bus Vero drives this signal when it detects bad data parity on a write to one of its internal registers. No interrupt or status is reported in this case. |  |

# 1.6.2 Vero AIB Bus Signals

| Table 2 (Page 1 of | 2). Vero AI | B Bus Signals                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|--------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name               | Type        | Description                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| A_AD(31-0)         | I/O         | AIB Address/Data(31-0) are the multiplexed address and data bits for the AIB interface. For DMA data transfer to a DMA slave AIB device these lines are data only. All DMA data transfers use implicit addressing of the I/O device with the DACK signals. For 80960 data transfer to the AIB an address is generated on AD0-18 during the first clock cycle and then data is presented on subsequent cycles. |  |

| A_PAR(3-0)         | I/O         | AIB Data Parity(3-0) are the data parity data bits that are driven by the device supplying data during a data transfer cycle. Each bit is the generated odd parity bit for the corresponding byte of data. Vero generates the parity bits during writes and can check them during reads.                                                                                                                      |  |

| -A_ALE             | 0           | -AIB Address Latch Enable is provided during 80960 data transfer to allow an external address latch to demultiplex the AD0-18 signals.  Address is valid before and after the falling edge of this signal.                                                                                                                                                                                                    |  |

| -A_BE(3-0):        | I/O         | -AIB Byte Enables(3-0) are driven along with address during 80960 data transfer to the AIB. These four signals indicate to the AIB which data bytes are valid for a given cycle for write operations. They are used during read operations to tell the AIB which data bytes are considered to be valid for the read access.                                                                                   |  |

|                    |             | During DMA read operations to a DMA slave AIB device, these signals are driven by the DMA device to indicate to the DMA controller which data bytes are valid for that cycle. During DMA write operations, these signals are driven by the the DMA controller to indicate to the device how many data bytes are valid for that cycle.                                                                         |  |

| -A_WR              | 0           | -AIB Write is driven active during a write operation to an AIB slave device.                                                                                                                                                                                                                                                                                                                                  |  |

| -A_RD              | 0           | -AIB Read is driven valid during a read operation to an AIB slave device.                                                                                                                                                                                                                                                                                                                                     |  |

| -A_DEN             | 0           | -AIB Data Enable is driven active during the data phase of a cycle to an AIB slave device. For reads, it is an indication that it is now alright to enable data on to the bus. For writes, it is an indication that data is now valid on the bus.                                                                                                                                                             |  |

| -A_CS(0-4)         | O           | -AIB Chip Select(0-4) are driven active when a valid address decode is detected for the address ranges defined in the CSD0-4 registers.                                                                                                                                                                                                                                                                       |  |

| +A_RDY             | I           | +AIB Ready is used to pace the cycle if the active cycle time for an AIB slave device is greater than the programmed cycle time (see 4.2.1, "Chip Select Definition registers (CSD0-4)" on page 54). The AIB bus is normally 'ready', and this signal is driven low by the slave device to extend the cycle time. A_RDY is not supported during DMA transfers.                                                |  |

| -A_RESET           | 0           | -AIB Reset is used to reset the AIB. It is driven active for 60ns after the rising edge of the -RESET input signal, and can also be driven active under program control of the 80960 to reset just the AIB.                                                                                                                                                                                                   |  |

| -A_ERROR           | I           | -AIB Error input is driven by the AIB when any AIB defined critical error occurs. This will cause vector #232 to be generated. (see Table 12 on page 44).                                                                                                                                                                                                                                                     |  |

| Table 2 (Page 2 of 2). Vero AIB Bus Signals |      |                                                                                                                                                                                                                                                                                                                                                  |  |

|---------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name                                        | Туре | Description                                                                                                                                                                                                                                                                                                                                      |  |

| A_CLK                                       | О    | AIB Clock is the 25MHz AIB reference clock.                                                                                                                                                                                                                                                                                                      |  |

| -D_REQ(0-7)                                 | I    | <b>-DMA Request(0-7)</b> are the eight DMA request signals that AIB devices use to request DMA service. These signals are driven active asynchronously and driven inactive in response to the device receiving the corresponding DACK signal.                                                                                                    |  |

| -D_ACK(0-7)                                 | 0    | <b>-DMA Acknowledge(0-7)</b> are the eight DMA acknowledge signals that the DMA controller drives to the AIB Bus when the corresponding DREQ is being serviced. The duration of these signals are individually programmable within the DAPW registers to allow for both fast and slow devices to coexist on the AIB with minimal external logic. |  |

| -D_EOP(0-7)                                 | I/O  | <b>-DMA End-of-Process(0-7)</b> used to signal various termination conditions for the DMA channels.                                                                                                                                                                                                                                              |  |

|                                             |      | For a DMA transmit channel, EOP can be either a synchronous output or an asynchronous input. As an output, EOP is driven active synchronous with the data DACK transfer on which a DMA terminal count condition occurs.                                                                                                                          |  |

|                                             |      | For a DMA receive channel, EOP can be either a synchronous input or an asynchronous input. Either case can optionally cause a DMA channel to flush the current buffer, stop, interrupt, or chain. There is a separate EOP signal for each DMA channel.                                                                                           |  |

| -A_DETECT                                   | I    | -AIB Detect input must be driven low to allow VERO AIB bus to function. The state of this signal is readable in the 5.1.1, "Presence Detect Register (PDR)" on page 61.                                                                                                                                                                          |  |

# 1.6.3 Vero Interrupt Controller Signals

| Name           | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PXINT(7-0)     | 0    | <b>Processor Interrupt (7-0)</b> form an interrupt vector bus that is compatible with the 80960CA expanded mode interrupt structure. Vero internally manages the prioritization of interrupt input signals and translates those inputs into specific interrupt vectors which are placed on this bus. This bus is active low.                                                                                                                                                                                                                                                                              |  |

| -A_INT(3-0)    | I    | -AIB Interrupts(3-0) are four separate interrupt input signals that are driven active by devices on the AIB when interrupt service by the 80 is requiredAIB_INT(0) and -AIB_INT(1) can be optionally programmed to require the interrupting device to supply an 8-bit interruvector when the corresponding INTACK signal is driven active. Also these two inputs can be used as direct interrupt inputs with the vector being automatically supplied by the Vero chipAIB_INT(2) and -AIB_INT(3) are always used as direct interrupt inputs with the vector automatically being supplied by the Vero chip. |  |

|                |      | When operating -AIB_INT(0) or -AIB_INT(1) in interrupt acknowledge mode, the interrupt must be cleared at its source, AND the appropriate EOI to the interrupt controller must be issued, or interrupts below that prioritization level will be locked out (see 3.3.1, "AIB INTO End-of-Interrupt (EOI0) command" on page 50 and 3.3.2, "AIB INTO End-of-Interrupt (EOI1) command" on page 50).                                                                                                                                                                                                           |  |

| -A_INTACK(1-0) | O    | -AIB Interrupt Acknowledge(1-0) are two separate output signals to the AIB that are coupled to each of the -AIB_INT(0) and -AIB_INT(1) signals. When a device uses the -AIB_INT(1-0) signals and the Vero chip is programmed to request an external vector, it must be capable of responding to the corresponding -AIB_INTACK(1-0) signal by driving an 8-bit interrupt vector on lines A_AD(7-0) during the interrupt acknowledge cycle.                                                                                                                                                                 |  |

| -L_INT(1-0)    | I    | <b>-Local Bus Interrupts(1-0)</b> are two separate interrupt input signals for devices that may reside on the Local Bus (or elsewhere).                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|                |      | These inputs must be held active until the interrupt has been acknowledged by a read or write to an interrupt device status register, which clears the interrupt at its source.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| M_INT(3-0)     | I    | -Miami Interrupts(3-0) are four encoded interrupt inputs that can interface to the Miami chip. These signals correspond to certain interrupts as shown in Table 12 on page 44. If unused these signals should be pulled up to +5 V.                                                                                                                                                                                                                                                                                                                                                                       |  |

| B_INT(3-0)     | I    | -Brighton Interrupts(3-0) are four encoded interrupt inputs that can interface to the Brighton chip. These signals correspond to certain interrupts as shown in Table 12 on page 44. If unused these signals should be pulled up to +5 V.                                                                                                                                                                                                                                                                                                                                                                 |  |

| -WDOG          | 0    | -Watch Dog Error can be used to provide an output signal to the Miami chip when the watchdog timer interrupt is issued. It goes low when B_INT(3-0)='0000'.                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

# 1.6.4 Vero Miscellaneous Signals

| Table 4. Vero Miscellaneous Signals |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|-------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name                                | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| PD(11-8) and PD (6-0)               | I    | Presence Detect(11-8) and PD (6-0) are used as dedicated digital inputs to Vero. (see 5.1.1, "Presence Detect Register (PDR)" on page 61).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| -LED_EN                             | О    | <b>-LED Enable</b> is a signal dedicated to enabling an external light emitting diode for diagnostic purposes. (see 5.1.2, "LED Enable Register (LER)" on page 62).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| PRI/-SEC_ADDR                       | I    | Primary/-Secondary Address Select is a dedicated input for selecting the address map on the Local Bus for Vero. This input will allow for two (2) Vero chips to be attacted to the CFE Bus. This pin should be pulled up to +5 external to the chip in order to select the primary address. This pin should be driven low external to the chip in order to select the secondary address. The primary address map will be from 1FF00000 h to 1FF8FFFF h. The secondary address map will be from 1FE00000 h to 1FE8FFFF h. (see 1.7.1, "Vero Primary and Secondary Address Map Information" on page 19).  Note: This spec lists all addresses as primary addresses. For secondary addresses use 1FExxxxxx instead of 1FFxxxxx. |  |

# 1.6.5 Vero Clocks and Reset

| Table 5 (Page 1 of 2). Vero Clocks and Reset |      |                                                                                                                                                                                                    |  |

|----------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name                                         | Type | Description                                                                                                                                                                                        |  |

| L_OSC                                        | I    | <b>Local Oscillator</b> is the Local Bus input reference clock. All internal functional non-overlapping clocks are derived from this oscillator. All CFE Bus signals are referenced to this clock. |  |

| TST_CLKA                                     | I    | <b>LSSD A_Clock</b> is used during LSSD testing of the chip. This pin should be pulled up to $+5$ v external to the chip during normal operation.                                                  |  |

| TST_CLKB                                     | I    | <b>LSSD B_Clock</b> is used during LSSD testing of the chip. This pin should be pulled up to +5 v external to the chip during normal operation.                                                    |  |

| TST_CLKC                                     | I    | <b>LSSD C_Clock</b> is used during LSSD testing of the chip. This pin should be pulled up to +5 v external to the chip during normal operation.                                                    |  |

| RAMTSTCLK                                    |      | <b>LSSD Ram_Clock</b> is used during LSSD testing of the chip. This pin should be pulled up to +5 v external to the chip during normal operation.                                                  |  |

| RAMTSTEN                                     | I    | Ram Test Enable is used to enable testing of the internal RAM's during LSSD test. This pin should be pulled up to +5 v external to the chip during normal operation.                               |  |

| Table 5 (Page 2 of 2). Vero Clocks and Reset |      |                                                                                                                                                                                                                                                                                                             |  |

|----------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name                                         | Type | Description                                                                                                                                                                                                                                                                                                 |  |

| DI                                           | I    | <b>Driver Inhibit</b> is used to tri-state all I/O and outputs of the chip. This pin should be pulled up to +5 v external to the chip during normal operation. This pin is tied low at the same time that the IN CIRCUIT TEST pin is tied high to tri-state all internal off chip drivers.                  |  |

| ICT_EN                                       | I    | <b>In-Circuit Test</b> places the chip in an I/O mapping mode for in-circuit testing (see Appendix D, "In-Circuit Test I/O Mapping" on page 81). This pin should be pulled up to +5 v external to the chip during normal operation. The DRIVER INHIBIT pin must be tied high to put the chip into ICT mode. |  |

| COMP_RES                                     | I    | <b>Compensation Resistor</b> is a chip input used to adjust the speed of all internal off-chip drivers. This signal should be pulled up to +5 v through a 909 +/- 1% ohm resistor.                                                                                                                          |  |

| -RESET                                       | I    | Reset is the reset input signal to the chip.                                                                                                                                                                                                                                                                |  |

# 1.7 Vero Register Address Map

The memory map of all registers addressable within the Vero module is shown below. Detailed information is found in the indicated section. Each register is 4 byte aligned in the address space and should be accessed using 80960 'word' load (ld) and 'word' store (st) instructions.

All registers, when read, will return '0' values in those bits that are undefined for a specific register.

At the end of each register description section, that registers RESET conditions are shown. RESET COMMAND refers to the value that the register bits assume if a DMA channel is reset using either the DMA Channel Command Register (see 2.2.2, "DMA Channel Command Registers (DCCR 0-7)" on page 26) or the Global DMA Command Register (see 2.2.3, "Global DMA Command Register (GDCR)" on page 27). Also, a 'U' in the "Reset Conditions" section means undefined, and an 'S' means the value stays the same as before the reset command.

#### 1.7.1 Vero Primary and Secondary Address Map Information

This document will only reference the primary addresses for the Vero registers. The primary and secondary addresses for the Vero registers are:

Primary Address Map: 1FF8000 h to 1FF8FFFF h Secondary Address Map: 1FE8000 h to 1FE8FFFF h

| Table 6. Vero DMA Registers          |                      |                |         |  |  |

|--------------------------------------|----------------------|----------------|---------|--|--|

| Name                                 | Local Bus<br>Address | Access<br>Type | Section |  |  |

| DMA Channel 'x' AIB_ADDR 1/2         | 1FF8x000h            | r/w            | 2.2.7   |  |  |

| DMA Channel 'x' AIB_OP1 Data         | 1FF8x004h            | r/w            | 2.2.8   |  |  |

| DMA Channel 'x' AIB_OP2 Data         | 1FF8x008h            | r/w            | 2.2.9   |  |  |

| DMA Channel 'x' Memory Pointer       | 1FF8x00Ch            | r/w            | 2.2.4   |  |  |

| DMA Channel 'x' Transfer/Queue Count | 1FF8x010h            | r/w            | 2.2.5   |  |  |

| DMA Channel 'x' Chain Pointer        | 1FF8x014h            | r/w            | 2.2.6   |  |  |

| DMA Channel 'x' Channel Control      | 1FF8x018h            | r/w            | 2.2.1   |  |  |

| DMA Channel 'x' Queue Tail Pointer   | 1FF8x01Ch            | ro             | 2.2.10  |  |  |

| DMA Channel 'x' Command              | 1FF8x020h            | r/w            | 2.2.2   |  |  |

| DMA Channel 'x' Queuing              | 1FF8x024h            | r/w            | 2.4     |  |  |

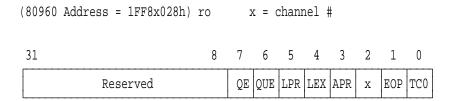

| DMA Channel 'x' Interrupt Status     | 1FF8x028h            | ro             | 2.5.1   |  |  |

| DMA Channel 'x' Fifo Residual Count  | 1FF8x02Ch            | ro             | 2.6.1   |  |  |

| Global DMA Command                   | 1FF88000h            | r/w            | 2.2.3   |  |  |

| Local Bus Configuration              | 1FF88008h            | r/w            | 2.6.2   |  |  |

| Queuing Status                       | 1FF8800Ch            | r/w            | 2.4.2   |  |  |

| Note: 'x' = DMA channel number.      | •                    | •              | •       |  |  |

| Table 7. Vero Interrupt Registers |                      |                 |         |  |

|-----------------------------------|----------------------|-----------------|---------|--|

| Name                              | Local Bus<br>Address | Access<br>Type  | Section |  |

| Interrupt Initialization          | 1FF88010h            | r/w             | 3.2.1   |  |

| Interrupt Mask                    | 1FF88014h            | r/w             | 3.2.2   |  |

| Interrupt Status                  | 1FF88018h            | ro              | 3.2.3   |  |

| AIB INT0 End-of-Interrupt         | 1FF89000h            | wo<br>(command) | 3.3.1   |  |

| AIB INT1 End-of-Interrupt         | 1FF8A000h            | wo<br>(command) | 3.3.2   |  |

| Table 8. Vero AIB Registers   |                      |                |         |  |  |  |

|-------------------------------|----------------------|----------------|---------|--|--|--|

| Name                          | Local Bus<br>Address | Access<br>Type | Section |  |  |  |

| Chip Select Definition 0      | 1FF8B000h            | r/w            | 4.2.1   |  |  |  |

| Chip Select Definition 1      | 1FF8B004h            | r/w            | 4.2.1   |  |  |  |

| Chip Select Definition 2      | 1FF8B008h            | r/w            | 4.2.1   |  |  |  |

| Chip Select Definition 3      | 1FF8B00Ch            | r/w            | 4.2.1   |  |  |  |

| Chip Select Definition 4      | 1FF8B010h            | r/w            | 4.2.1   |  |  |  |

| DMA Acknowledge Pulse Width 0 | 1FF8B030h            | r/w            | 4.2.2   |  |  |  |

| DMA Acknowledge Pulse Width 1 | 1FF8B034h            | r/w            | 4.2.2   |  |  |  |

| DMA Acknowledge Pulse Width 2 | 1FF8B038h            | r/w            | 4.2.2   |  |  |  |

| DMA Acknowledge Pulse Width 3 | 1FF8B03Ch            | r/w            | 4.2.2   |  |  |  |

| DMA Acknowledge Pulse Width 4 | 1FF8B040h            | r/w            | 4.2.2   |  |  |  |

| DMA Acknowledge Pulse Width 5 | 1FF8B044h            | r/w            | 4.2.2   |  |  |  |

| DMA Acknowledge Pulse Width 6 | 1FF8B048h            | r/w            | 4.2.2   |  |  |  |

| DMA Acknowledge Pulse Width 7 | 1FF8B04Ch            | r/w            | 4.2.2   |  |  |  |

| AIB Command/Status            | 1FF8C000h            | r/w            | 4.2.3   |  |  |  |

| Table 9. Vero Miscellaneous Registers |                      |                |         |  |  |  |

|---------------------------------------|----------------------|----------------|---------|--|--|--|

| Name                                  | Local Bus<br>Address | Access<br>Type | Section |  |  |  |

| Presence Detect                       | 1FF8D000h            | ro             | 5.1.1   |  |  |  |

| LED Enable                            | 1FF8D004h            | r/w            | 5.1.1   |  |  |  |

# 2.0 Vero DMA Controller

#### 2.1 General

The functions of the DMA portion of the Vero module are highlighted below.

- 8 independent DMA channels

- split bus implementation (32-bit AIB Bus to 32-bit Local Bus)

- support of 8/16/32 bit AIB Bus devices

- 16 byte buffer per channel

- 16 byte burst capability on Local Bus (57 MB/s peak bandwidth)

- 32-bit 4GB addressability on Local Bus

- 16-bit 64KB addressability on AIB Bus for AIB OP's

- separate DREQ and DACK signals for each DMA channel

- programmable DACK cycle time

- 64KB byte count capability

- 8 word descriptor block for each channel

- linked list chaining of buffers on all channels

- chaining support for end-of-process and terminal count condition

- buffer queuing (up to 4K-1 buffers) on all channels

- automatic storage of residual transfer count on chain event

- · automatic storage of AIB OP reads on chain event

- up to 2 programmable auto I/O operations on chain event

- 7 interrupt sources for each channel

Each of the 8 DMA channels are of equal function. Each channel can be programmed to support data transfer, 1) from the AIB Bus to the Local Bus (receive) or, 2) from the Local Bus to the AIB Bus (transmit). The service priority is fixed with CH0 having highest priority and CH7 having lowest priority.

Each channel is controlled by an 8 word Channel Descriptor Table (CDT). The program normally writes the desired CDT register values to memory resident structures called Channel Descriptor Blocks (CDB's). The program then writes the starting address of a CDB to the Queuing Register (see 2.4, "Queuing Operation (NOT Supported)" on page 36). At this point, the CDB is automatically fetched from memory and loaded into the CDT. Chains of CDB's are linked using this queuing mechanism. Alternately, the CDT registers can be programmed directly.

Once enabled, a channel will service DMA requests from the AIB Bus until one of a number of programmable conditions is reached. If the DMA channel is programmed to stop on one of these conditions, the channel can be re-enabled with a write to the Channel Control Register (CCR), or by queuing another buffer. Any condition that can stop the channel can also interrupt the 80960. Also, the channel has the ability to interrupt without stopping the channel. All of the options are programmable in the CCR and are described later.

The two types of DMA requests that come from the AIB Bus can be classified as a Transmit request (TR) or a Receive request (RR).

Once a TR is received, the DMA controller arbitrates for control of the Local Bus, and when granted control, bursts 16 bytes of data from memory into that channel's FIFO buffer. The data is then transferred to the requesting device across the AIB Bus until the FIFO buffer is empty. This allows data transfer to the AIB device to occur in the background of Local Bus activity.

For a receive DMA channel, the DMA controller will receive up to 16 bytes of data across the AIB Bus. It then arbitrate for control of the Local Bus. Once granted, the DMA controller bursts all 16 bytes into

memory. This, again, allows data transfer from the AIB device to occur in the background of Local Bus activity.

**DMA FIFO Buffer:** As mentioned above, data transfer from Local Bus to AIB Bus is not direct, but rather, is buffered in a set of fifo's. There is a 16 byte deep fifo associated with each DMA channel that acts as an intermediate storage area for data. The fifos support high speed access so that all accesses to the Local Bus will move data into and out of the fifos instead of directly to the AIB Bus, which might support only slower devices. This allows all Local Bus DMA data transfer initiated by Vero to be high speed bursted accesses.: The fifo's are configured such that AIB Bus accesses and Local Bus accesses can occur simultaneously. One DMA channel can be performing a read or write on the AIB Bus, while at the same time, another channel is performing a read or write on the Local Bus.

# 2.2 Channel Descriptor Table

Table 10 shows the organization of the channel descriptor table for one of the DMA channels. This table is duplicated for each of the 8 DMA channels. The table exists in the address space of the 80960 and is accessible via 32-bit 'load' and 'store' type instructions.

| Table 10. Vero Channel Descriptor Table (CDT) |                      |            |  |  |  |  |

|-----------------------------------------------|----------------------|------------|--|--|--|--|

| Register Name                                 | Local Bus<br>Address | Valid Bits |  |  |  |  |

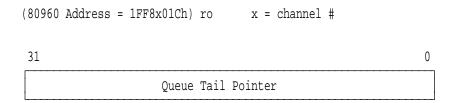

| Queue Tail Pointer (QTP)                      | 1FF8x01Ch            | 31-0       |  |  |  |  |

| Channel Control Register (CCR)                | 1FF8x018h            | 21-0       |  |  |  |  |

| Chain Pointer Register (CPR)                  | 1FF8x014h            | 31-0       |  |  |  |  |

| Queue Count Register (TQC)                    | 1FF8x010h            | 27-16      |  |  |  |  |

| Transfer Count Register (TQC)                 | 1FF8x010h            | 15-0       |  |  |  |  |

| Memory Pointer Register (MPR)                 | 1FF8x00Ch            | 31-0       |  |  |  |  |

| AIB OP2 Data Register (AIB_OP2)               | 1FF8x008h            | 31-0       |  |  |  |  |

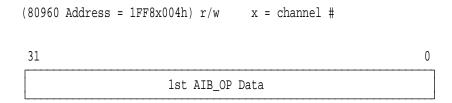

| AIB OP1 Data Register (AIB_OP1)               | 1FF8x004h            | 31-0       |  |  |  |  |

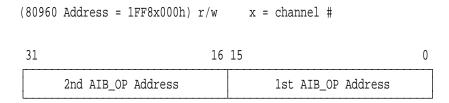

| AIB OP2 Address Register (AIB_ADDR2)          | 1FF8x000h            | 31-16      |  |  |  |  |

| AIB OP1 Address Register (AIB_ADDR1)          | 1FF8x000h            | 15-0       |  |  |  |  |

| Note: 'x' = DMA channel number.               | ·                    | ·          |  |  |  |  |

## 2.2.1 Channel Control Register (CCR)

**Description:** The CCR register controls the operational personality for a DMA channel.

#### **Register Format**

| (80960 Address = 1FF8x018h) $r/w$ x = channel # |                  |                               |           |          |                              |          |           |          |                            |            |              |            |            |

|-------------------------------------------------|------------------|-------------------------------|-----------|----------|------------------------------|----------|-----------|----------|----------------------------|------------|--------------|------------|------------|

| 15 14<br>channe<br>stoppi<br>option             | el c<br>.ng   in | 11<br>hanne<br>terru<br>ption | el<br>ipt | cł       | 8<br>nanne<br>naini<br>ptior | ing      | 6         | 5        | 4<br>char<br>defir<br>opti | nitio      | 2<br>on      | 1          | 0          |

| STP STP 2 1                                     | STP INT 0 2      | INT<br>1                      | INT<br>0  | LCH<br>2 | LCH<br>1                     | LCH<br>0 | POI<br>SI |          | -                          | EOP<br>AEN | TR<br>SYN    | '          | EN/<br>DIS |

| 31 30                                           |                  |                               |           |          |                              |          | 22        | 21<br>Al |                            | 19         | 18<br>Al     |            | 16         |

|                                                 |                  | Reser                         | rved      |          |                              |          |           | cont     | ite<br>crol                |            | pera<br>cont |            | n          |

| GEN  <br>STA                                    |                  | Reser                         | rved      |          |                              |          |           | WR<br>1  | WR<br>0                    | OP<br>#2   | OP<br>#1     | #IO<br>OPS | #IO<br>OPS |

#### **Bit Descriptions**

- Bit 31. General purpose status bit. This bit can be used for any application dependent purpose. It has no function internal to the chip. It is updated by I/O writes, and during list chaining fetches.

- Bits 30-22. Reserved. Always program these bits to '0'.

- Bits 21-20. These two bits are encoded to indicate what data will be written to the AIB Bus on the second of two AIB OP's, if the first of the two AIB OP's is a read.

```

B21 B20

--- 0 0 -- Write the value of AIB_OP2 Data Register

0 1 -- Write the value that was read on first OP

1 0 -- Write the complement of value read on first OP

1 1 -- Reserved

```

- Bit 19. AIB OP #2, read or write. This bit is coupled with bits 16 and 17. It defines the second IO operation to the AIB Bus after a chain event to be a read or write. 0 = read. 1 = write. If the operation is a write, the data written is defined by bits 20 and 21 of the CCR. If the operation is a read, the data will be stored in memory.

- Bit 18. AIB OP #1, read or write. This bit is coupled with bits 16 and 17. It defines the first IO operation to the AIB Bus after a chain event to be a read or write. 0 = read. 1 = write. If the operation is a write, the data written is defined by bits of the AIB\_OP1 register. If the operation is a read, the data will be stored in memory.

- Bits 17-16. Number of IO operations to AIB Bus upon chain event. These two bits are encoded to provide the DMA controller with the ability to execute up to 2 discrete IO operations to the AIB Bus following the recognition of a chain event. The address to which the first IO operation occurs is defined

by bits 0-15 in the AIB\_ADDR 1/2 register. The address to which the second IO operation occurs is define by bits 16-31 in the AIB\_ADDR 1/2 register.

```

00 = No IO operation upon chain event.

01 = One IO operation upon chain event.

10 = Two IO operations upon chain event.

11 = Reserved.

```

• Bit 15-13. Encoded DMA channel stopping options.

| STP2 | STP1 | STP0 | Stopping Option |

|------|------|------|-----------------|

|      |      |      |                 |

| 0    | 0    | 0    | Do not stop     |

| 0    | 0    | 1    | TC=0            |

| 0    | 1    | 0    | EOP             |

| 0    | 1    | 1    | TC=0 "or" EOP   |

| 1    | 0    | 0    | Reserved        |

| 1    | 0    | 1    | Reserved        |

| 1    | 1    | 0    | Reserved        |

| 1    | 1    | 1    | Reserved        |

When a channel is stopped, the CCR enable/disable bit is reset. Also, a chaining condition takes precedence over a stopping condition if both occur at the same time since the chaining condition causes a new CCR enable/disable bit to be fetched from memory.

• Bit 12-10. Encoded DMA interrupt options.

| INT2 | INT1 | INT0 | Interrupt Option |

|------|------|------|------------------|

|      |      |      |                  |

| 0    | 0    | 0    | Disabled         |

| 0    | 0    | 1    | TC=0             |

| 0    | 1    | 0    | EOP              |

| 0    | 1    | 1    | TC=0 "or" EOP    |

| 1    | 0    | 0    | Reserved         |

| 1    | 0    | 1    | Reserved         |

| 1    | 1    | 0    | Reserved         |

| 1    | 1    | 1    | Reserved         |

• Bit 9-7. Encoded list chaining enabling options.

| LCH2 | LCH1 | LCH0 | Chaining Option |

|------|------|------|-----------------|

|      |      |      |                 |

| 0    | 0    | 0    | Disabled        |

| 0    | 0    | 1    | TC=0            |

| 0    | 1    | 0    | EOP             |

| 0    | 1    | 1    | TC=0 "or" EOP   |

| 1    | 0    | 0    | Reserved        |

| 1    | 0    | 1    | Reserved        |

| 1    | 1    | 0    | Reserved        |

| 1    | 1    | 1    | NOP             |

The chaining NOP selection, when detected, immediately causes the next CDB in memory to fetched without processing the CDB containing the NOP.

• Bit 6-5. DMA port size. These two bits define the data port size of the DMA device.

| PS1 | PS0 | Data Port Size |

|-----|-----|----------------|

|     |     |                |

| 0   | 0   | 8-bit          |

| 0   | 1   | 16-bit         |

| 1   | 0   | 32-bit         |

| 1   | 1   | Reserved       |

• Bit 4. End-of-Process direction control. If this bit is set to a '1', the EOP signal is an input. If this bit is set to a '0', the EOP signal is an output.

If the channel is a transmit DMA channel, and this bit is '0', then the EOP signal is driven synchronously with the last byte transferred when TC=0. For a transmit channel, if this bit is '1', then EOP is an asynchronous input that can causing chaining based on how bits 7-9 are programmed. Asynchronous EOP's must only occur on 16-byte boundaries for Tx DMA.

If the channel is a receive DMA channel, and this bit is '0', then the EOP signal is disabled as an input. For a receive channel, if this bit is '1', then EOP is an input that can causing chaining based on how bits 7-9 are programmed.

- Bit 3. EOP asynchronous input enable. When this bit is set to '1' the Vero chip is enabled to detect an asynchronous EOP input. When reset, the chip will not detect asynchronous EOP inputs. The Vero chip is ALWAYS enabled to detect synchronous EOP inputs.

- Bit 2. DMA transfer synchronization option. When this bit is set to '0' all DMA transfers are synchronized by the DREQ input pins of the Vero chip. The DREQ signal must become active for a DMA transfer to occur. When this bit is set to '1' DMA transfers are not synchronized to the DREQ input pins. DMA transfers will begin as soon as the CCR bit 0 is enabled and will continue until a channel stopping condition is reached.

- Bit 1. -Receive/+transmit indicator. 0 = channel is servicing receive DMA requests; 1 = channel is servicing transmit DMA requests. For receive requests, data transfer is FROM AIB Bus TO Local Bus. For transmit requests, data transfer is FROM Local Bus TO AIB Bus.

- Bit 0. +Enable/-disable channel. 0 = channel disabled to service DMA requests; 1 = channel enabled to service DMA requests. This bit can be used to disable the channel at any time. Re-enabling the channel will cause the DMA operation to start where it left off. Also, any programming option that disables the channel will be reflected in this bit. This bit is updated with its corresponding bit during list chaining reads from memory. This bit can also be set/reset via the DCCR. (see2.2.2, "DMA Channel Command Registers (DCCR 0-7)" on page 26)

If queuing is disabled in the LBCR (see 2.6.2, "Local Bus Configuration register (LBCR)" on page 42), then this bit can not be set unless a non-zero value has been previously written to the Queue Count portion of the TQC register (see 2.2.5, "Transfer/Queue Count Register (TQC)" on page 29).

**Note:** This bit or bit 0 of the DCCR registers alone should not be used as a status bit to determine if Vero is disabled, stopped, or reached the end of a chain. Instead the user should use both bit 31 and bit 0 of the CCR to determine the status of Vero during a linked list chaining. The following is an example assuming that bit 31 and bit 0 of the CCR are set in the main CDB's and are reset in the dummy CDB's

| Bit 31 | Bit 0 | Vero status |

|--------|-------|-------------|

| 1      | 1     | Running     |

| 1      | 0     | Chaining    |

| 0      | 0     | Stopped.    |

#### **Reset Conditions**

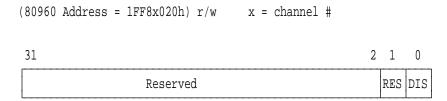

## 2.2.2 DMA Channel Command Registers (DCCR 0-7)

**Description:** The DCCR supports two commands. One allows for the bit manipulation of the CCR enable/disable bit. This bit allows CCR bit 0 to be set/reset without affecting the other CCR bits. A second command allows internal logic to be reset to a known state if an error condition causes a channel to stop before completion. A separate command register exists to control each DMA channel.: The command to enable a channel should not be issued with the same write that releases the channel from a reset command.

#### **Register Format**

#### **Bit Descriptions**

- Bit 7-2. Reserved. Always read as '0'.

- Bit 1. Reset channel command. Setting this bit to '1' causes a channel to be reset as shown by the Reset Command for each register. The channel is held in the reset state until the bit is set back to '0'.

- Bit 0. Disable channel command. Bit 0 = '0' defines the command to disable the channel. Bit 0 = '1' defines the command to enable the channel. Bit 0 of the CCR, if read, will reflect a disable command if it is issued through the DCCR.

When a channel is disabled, any internally pending operations are performed before the channel stops servicing DMA requests.

#### **Reset Conditions**

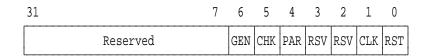

## 2.2.3 Global DMA Command Register (GDCR)

**Description:** The GDCR allows two commands to be issued globally to all DMA channels at once. It allows all DMA channels to be 'stopped' with one command or all DMA channels to be reset with one command. The 'stopped' state of each channel is reflected in the EN/DIS bit of the CCR.: The command to re-start all channels should not be issued with the same write that releases all channels from a reset command.

#### **Register Format**

#### **Bit Descriptions**

- Bits 7-2. Reserved. Always read as 0.

- Bit 1. Reset all channels command. Setting this bit to '1' causes all the channels to be reset as shown by the Reset Command for each register. All channels are held in the reset state until the bit is set back to '0'.

- Bit 0. Stop all channels command. If written to a '1' all channels are stopped. If written to a '0' all channels are re-started.

When a channel is 'stopped', all internally pending operations are performed before the channel stops servicing DMA requests.

#### **Reset Conditions**

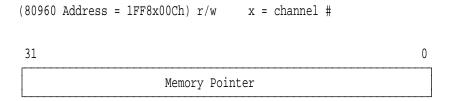

# 2.2.4 Memory Pointer Register (MPR)

**Description:** The MPR contains the 32-bit Local Bus address of the next data byte to be DMA'ed. There are no alignment restrictions on the address programmed into this register.

#### **Register Format**

#### **Reset Conditions**

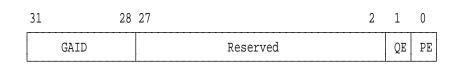

## 2.2.5 Transfer/Queue Count Register (TQC)

**Description:** The TQC register contains two separate count values. Bits 0-15 contains the current DMA transfer count in bytes. Values from 0001h to FFFFh can be programmed. This allows DMA transfers of from '1' to '64KB-1' to be transferred. This register is automatically saved into memory when a chain event occurs. This is shown in Figure 2 on page 34. When a receive DMA channel has been programmed with a port size of 32-bits, transfer count values 0001h, 0002h and 0003h are illegal and should not be programmed. When a receive DMA channel has been programmed with a port size of 16-bits, a transfer count value of 0001h is illegal and should not be programmed.

For a transmit DMA channel, a TC=0 condition is always defined as the transfer count value going from 0001h to 0000h. For a receive DMA channel, a TC=0 condition depends on the port size. For a 32-bit port a TC=0 condition is when the transfer count value is less than 4. For a 16-bit port a TC=0 condition is when the transfer count value is less than 2. For an 8-bit port a TC=0 condition is when the transfer count value is 0000h.

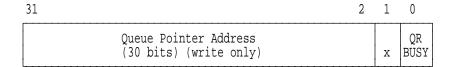

Bits 16-27 of this register contains a count of the number of CDB's that have been queued by the Queuing Register (QR). This allows up to '4K-1'(or 'FFF'h) CDB's to be queued per DMA channel. Each time the QR is written, this register is incremented by one. **The queue count should never be allowed to increment from 'FFF'h to '000'h.** Each time a CDB finishes processing (a stop condition or a chain condition defines the end of a CDB) this register is decremented by one. Software must initialize the Queue Count to '000'h if queuing is enabled in the LBCR (see 2.6.2, "Local Bus Configuration register (LBCR)" on page 42). If queuing is disabled in the LBCR then the Queue Count must be written to a non-zero value or the CCR enable/disable will not be able to be set to '1' to enable the DMA channel.

If the queue count register equals '0001'h and a chain event occurs, it will decrement to '0000'h. This means that another CDB has not been queued fast enough. In this case, the channel is automatically stopped and an error interrupt (queue underrun) is posted.

#### Register Format

(80960 Address = 1FF8x010h) r/w

x = channel #

31

28 27

16 15

0

Reserved

Queue Count

DMA Byte Count

#### **Reset Conditions**

**Note:** Never write a zero value to the DMA byte count portion, either directly or by linked list chaining. Also, a non-zero value must be written to the DMA byte count portion of this register for all DMA channels whenever a hardware reset has occurred.

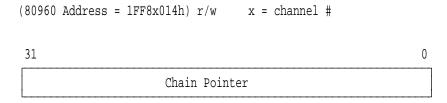

# 2.2.6 Chain Pointer Register (CPR)

**Description:** The CPR contains the 32-bit address pointer that points to the memory location where the DMA controller will fetch the CDB for the next buffer when a chain event occurs. The lower 2 bits of this register should always be programmed to '00' so that the chain pointer is 4 byte aligned. The following two conditions define a chaining event.

- 1. terminal count has been reached and list chaining for terminal count is enabled in the CCR,

- 2. an End-Of-Process condition has occurred and list chaining for end-of-process is enabled in the CCR.

**Note:** The CPR should always point to a valid memory location. This location should contain a valid "dummy" CDB with the channel control set to stop the channel and disable list chaining.

#### **Register Format**

#### **Reset Conditions**

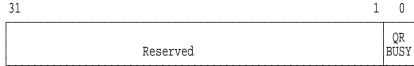

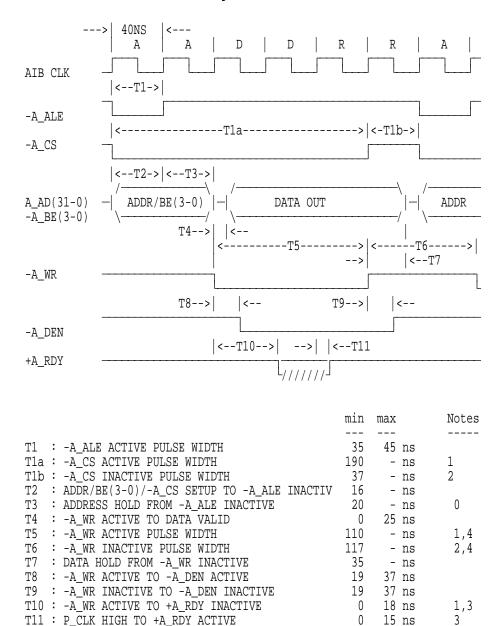

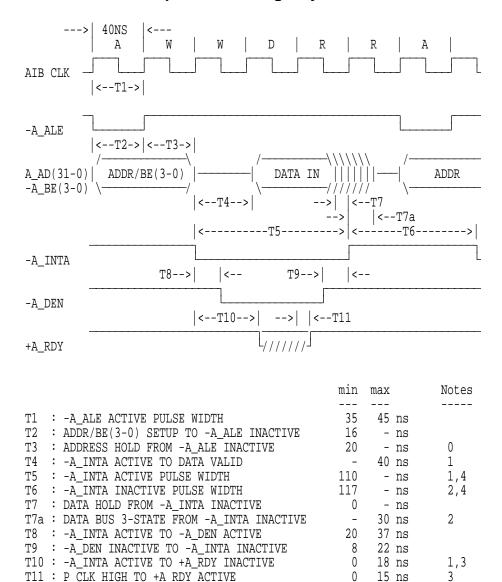

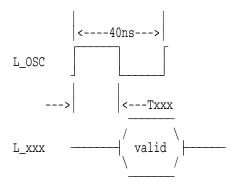

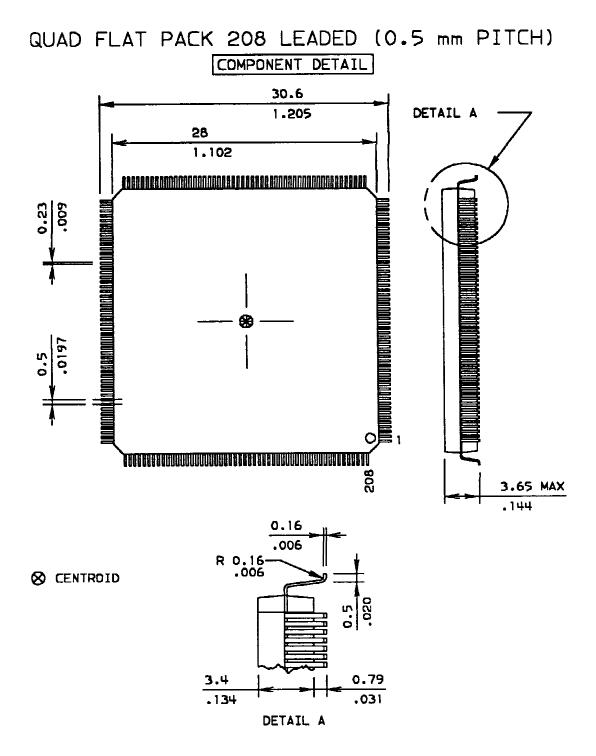

## 2.2.7 AIB Address 1/2 Register (AIB\_ADDR 1/2)