#### CHAPTER 6

#### RASTER SUBSYSTEM

The Raster Subsystem contains a Raster Engine chip which is responsible for performing low level pixel rendering operations. The Raster Subsystem also contains two hardware cursor chips which are used to draw block glyph or cross hair cursors. The Raster Engine is instructed by the Geometry Engine to draw lines and horizontal spans. The Geometry Engine also instructs the Raster Engine to perform pixel read and write DMA operations. The Raster Engine provides the control signals for reading and writing the pixel values into the frame buffer bitplanes, the Window ID (WID) bitplanes, the Pop Up (PUP) overlay bitplanes, the User Auxiliary (UAUX) bitplanes and the optional Z buffer bitplanes if installed.

The following sections describe the external interfaces, the major components, the registers, the basic operations and the programming considerations for the Raster Subsystem.

### External Interfaces

The Raster Subsystem has external interfaces with the Host System (via the Host Interface Subsystem and the Geometry Subsystem), the Geometry Subsystem and the Display Subsystem. The following paragraphs describe these external interfaces.

#### Host Interface

The Raster Subsystem has an interface with the Host System over the Utility Bus. The host can read and write the cursor glyph and the cursor registers in the two cursor chips. The host can also have the Geometry Subsystem initiate bitplane pixel DMA operations over the Geometry data bus. The host software can use the GE\_LOADRE token to load values into some of the Raster Engine registers.

# Geometry Subsystem Interface

The Geometry Subsystem uses the REptr register in the HQ1 chip to address the various Raster Engine registers. The data is then written into or read from the Raster Engine registers using the Geometry data bus. The GE5 microcode can also initiate DMA transfers between the bitplanes and the GE5 data RAM or the host system RAM. The HQ1 chip in the Geometry Subsystem also controls the host data transfers to and from the registers in the two cursor chips.

# Display Subsystem Interface

The Raster Subsystem receives timing control signals from the Display State Machine in the Display Subsystem. In response its bitplanes and cursor chips send data to the Display Subsystem to be converted to analog RGB signals for output to the high resolution color monitor.

# Major Components

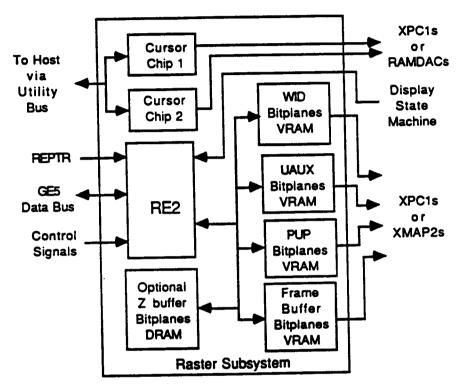

The major components of the Raster Subsystem are shown in the block diagram of Figure 6.1. The Raster Engine 2 (RE2) is a proprietary Silicon Graphics chip which performs the low level pixel rendering operations as instructed by the Geometry Subsystem. The Cursor chips are used to display two single color cursors or a single multicolor cursor. The cursor can be either a user defined glyph pattern or a cross hair pattern.

Figure 6.1 Raster Subsystem Block Diagram

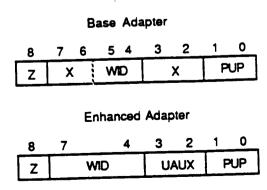

The frame buffer bitplanes are used to store the pixel image to be displayed on the monitor. The Window ID (WID) bitplanes are used for pixel write clipping and to index into the mode registers in the XPC1 or XMAP2 chips in the Display Subsystem to control pixel display formats. The PUP and UAUX bitplanes are used to hold overlay and underlay pixel data. The PUP bitplanes are managed by the host window manager software and are used to draw menus and other overlays. The UAUX bitplanes are controlled by the various graphics applications to display overlays or underlays. The Z buffer bitplanes are used for doing Z axis depth comparison for hidden line removal.

The number of bitplanes available on the MGR adapter depends on the whether the base configuration or the enhanced configuration is being used. For the base configuration, the MDE1 daughter board is installed so the base configuration has 8 bitplanes of Frame Buffer VRAM, 2 bitplanes of WID VRAM and 2 bitplanes of PUP VRAM. For the enhanced configuration the MEV2 daughter board is installed so the enhanced configuration has 24 bitplanes of Frame Buffer VRAM, 4 bitplanes of WID VRAM, 2 bitplanes of PUP VRAM and 2 bitplanes of UAUX VRAM. Both the base and enhanced configuration can have the optional MZB1 card installed with the 24 bitplanes of Z buffer DRAM. If the MZB1 daughter card is not installed then no Z buffer hidden line removal is available.

The following paragraphs describe the major components of the Raster Subsystem.

## Raster Engine 2 (RE2)

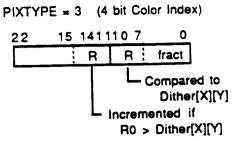

The RE2 performs scan conversion of lines and spans into pixels and controls all memory timings for writing these pixel values into the pixel bitplanes. The GE5, in the Geometry Subsystem, loads a bank of registers on the RE2 chip to indicate what kind of drawing operation is desired. The RE2 then iterates the x,y and z values and the red, green and blue colors to form the individual pixels values which it then writes into the pixel bitplanes. The RE2 can flat shade or Gouraud shade RGB or color index values while at the same time performing pixel write conditioning checks and pixel write mask operations. The RE2 can apply stipple patterns as it draws antialiased lines. The RE2 can also apply patterns as it draws spans. The RE2 provides support for 8, 12 and 24 bit RGB pixels and it also provides support for 4, 8 or 12 bit color index pixels. The RE2 also provides double buffer support for the 12 bit RGB and the 4 or 12 bit color index pixels. The color index pixels and the 12 bit RGB pixels can have a dithering operation performed on the color values which are used to calculate the Frame Buffer pixel values. The RE2 also provides support for 16 different raster operations which are performed on a bit by bit basis. The following paragraphs describe the main features of the RE2 chip.

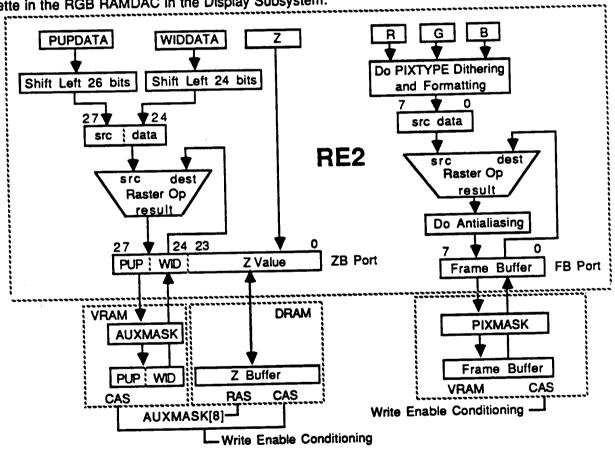

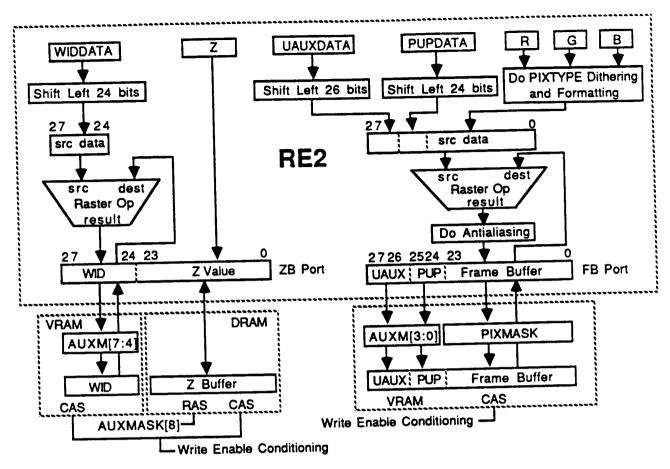

### **RE2 Architecture**

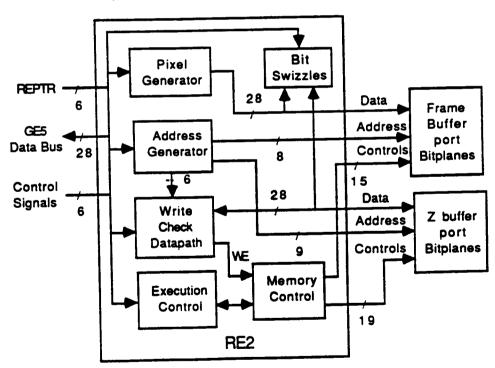

The RE2 consists of five major units as shown in the block diagram of Figure 6.2. The following paragraphs give a brief description of these five units.

Figure 6.2 RE2 Block Diagram

The Pixel Generator consists of three color components interpolators, a dither matrix and a pixel packing multiplexer. The color component interpolaters contain a digital differential analyzer (DDA) and a dithering circuit. The interpolator for red is also used for the color index values. This unit is responsible for calculating the Frame Buffer pixel values. These values are then used as part of the source data for the Raster operations. The color component interpolators add delta color values to the current color values and then performs the dithering calculations. The resulting color

values are then packed based on the current pixel type and is placed in the source buffer for the Raster Operation. The result is then written into the Frame Buffer bitplanes.

The Address Generator consists of 2 DDAs, one for X and one for Y. This unit generates the addresses used to access the various bitplanes. The address generator adds the delta x and y values to the current x and y values to form the pixel address of the next pixel to be accessed.

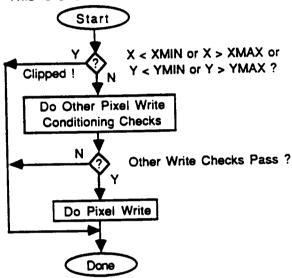

The Write Check Datapath unit consists of the DDA used for calculating Z values. This unit also contains the circuits for Z value comparisons, for window ID checks and for pattern and stipple checks. The delta Z value is added to the current z value to obtain the new z value. The new z value is then compared to the current z value in the Z buffer bitplanes at the x and y location. If the comparison fails the pixel is not written. The WID checking hardware is used to compare a current WID value with the WID value in the WID bitplanes at the x and y location. If the WID check is enabled and the WID comparison fails then the pixel is not written. The pattern checking can be used to enable or disable pixel writes for shaded spans. The stipple checks can be used to enable or disable pixel writes for lines.

The Execution Control unit determines the type of operation that the Raster Engine is performing. Possible operations include pixel write, Z write, memory refresh and display refresh. This unit controls the operation of the Memory Control unit.

The Memory Control unit generates the memory control signals for the various bitplanes.

The bit swizzles unit is used to shift the various pixel data bits left into the appropriate data bit locations for writing into the bitplanes. It also shifts the bits right as needed to right justify the bits which are read from the various bitplanes.

The RE2 basic operations section of this chapter discusses the operations performed by the RE2 in much greater detail.

#### Instruction Set

The RE2 has an Instruction Register and 56 microcode visible control registers. The GE5 microcode loads instructions into the Instruction Register to specify the operation that the Raster Engine will perform next. The 56 control registers are loaded with the data needed to perform the operation. When the Instruction Register is loaded by the Geometry Engine, the values in the control registers are loaded into the Raster Engine's execution units and the new instruction begins executing.

The control registers that are frequently loaded have input buffers. These control registers can be loaded while the Raster Engine is drawing. The control registers without input buffers can be loaded only when the Raster Engine is idle. The sequence of steps for issuing an instruction is:

- 1. Update control registers that have input buffers

- 2. If necessary, update control registers that do not have input buffers

- 3. Store instruction opcode in the Instruction Register

This sequence of steps gives the maximum overlap between Raster Engine execution and Geometry Engine execution. The GE5 microcode should try to update control registers that do not have input buffers only while the RE2 is idle. If the RE2 is not idle, the microcode will be stalled until the RE2 becomes idle.

The Registers section of this chapter defines the registers and the RE2 basic operations section of this chapter describes the use of the RE2 instructions and the control registers to perform the RE2 operations.

### Pixel Bitplanes

The MGR uses 1 Megabit VRAM chips to create the frame buffer bitplanes, PUP bitplanes, UAUX bitplanes and WID bitplanes. The MGR uses 1 Megabit DRAM chips to create the Z buffer bitplanes. The component timing restrictions require the VRAM and DRAM chips to be organized into five pixel pipelines to create a 1280 x 1024 pixel screen display. The pixels on each scan line are organized in an interleaved manner in groups of five pixels. The first pixel in each group of five pixels is contained in VRAM 0. The second pixel in each group of five pixels in is contained in VRAM 1. The third pixel in each group of five pixels is contained in VRAM 2. The fourth pixel in each group of five pixels is contained in VRAM 3 and finally the fifth pixel in each group of five pixels is contained in VRAM 4. Each VRAM chip provides 256 x 1024 x 4 pixels. The Z buffer pixels are organized in the same manner. The x = 0 and y = 0 pixel location is defined to be the lower left corner of the screen. The RE2 chip controls the storage of pixels into the VRAM chips and also the transfer of pixels out of the VRAM chips to the Display Subsystem.

The RE2 TOPSCAN register is used to specify the top scan line number to be displayed. This allows the VRAM configuration to support multiple different screen formats. The MGR adapter has four different display timings built into the Display State Machine (DSM) in the Display Subsystem. The four timings include the 1280 x 1024 noninterlaced and interlaced timings, the NTSC timing and the PAL timing. The TOPSCAN register must be set appropriately by the host software for each of the different timings.

The DSM controls the display timing for transfering pixels out of the VRAM to the Display Subsystem for display on the attached monitor. For each line on the raster display the DSM issues an transfer request to the RE2. The RE2 then uses the value in the TOPSCAN register to transfer the top scan line in the five VRAMs into their internal shift registers. The TOPSCAN register also contains the number of columns on each scan line. The DSM then generates a shift clock to the VRAM for each pixel on the scan line. Each shift clock pulse causes a pixel to be shifted out of the appropriate VRAM to the display subsystem for display. This process is repeated for each scan line on the screen. After the RE2 causes the current row to be transferred into the shift register in the VRAM it then decrements the TOPSCAN register so that it can access the next scan line row down the screen. After the bottom scan line on the screen has been displayed the DSM generates a vertical retrace to the monitor. After the vertical retrace period has completed the next raster image is scanned in the same manner as before.

The Z Buffer pixels are used only by the RE2 when it performs the Z value depth comparisons and the Z values are not shifted out to the Display Subsystem. This allows the Z buffer pixels to be stored in DRAM chips rather than the dual ported VRAM chips. The following paragraphs discuss the bitplane layouts in the base and the enhanced adapters.

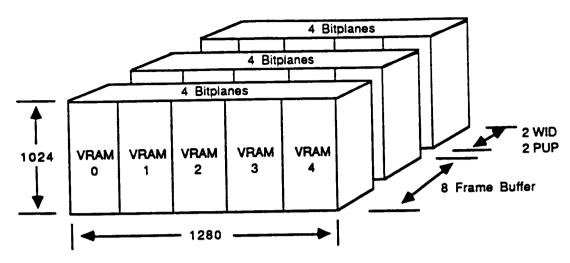

# Base Adapter Pixel Bitplanes

The base configuration of the MGR adapter contains 8 Frame Buffer bitplanes, 2 PUP bitplanes and 2 WID bitplanes as shown in Figure 6.3. These bitplanes are contained in fifteen VRAM chips. As described above the VRAMs are interleaved in five pixel groups. Each VRAM provides 256 x 1024 x 4 pixels. The 2 PUP bitplanes and the 2 WID bitplanes are grouped in the same five VRAMs. The chip layout shown in Figure 6.3 does not show the five pixel interleaving well. As described above, each VRAM contains every fifth pixel on each scan line. The first pixel is in VRAM 0 and the fifth pixel is in VRAM 4. This is repeated for each group of five pixels on each scan line.

Figure 6.3 Base Configuration VRAM Layout

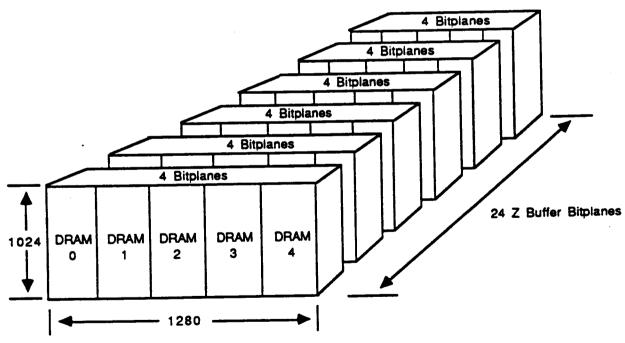

The base configuration of the adapter can also have an optional 24 bit Z buffer card installed. The Z buffer values are stored in DRAM chips rather than in VRAM chips. The layout of the Z Buffer is shown in Figure 6.4. The Z buffer DRAM chips are organized in the same five pixel interleaving that is used for the VRAM chips. Each DRAM chip contains 256 x 1024 Z values. Each DRAM chips provides 4 bits of the 24 bit Z value. This means that 30 DRAM chips are required for the Z Buffer.

Figure 6.4 Z Buffer DRAM Layout

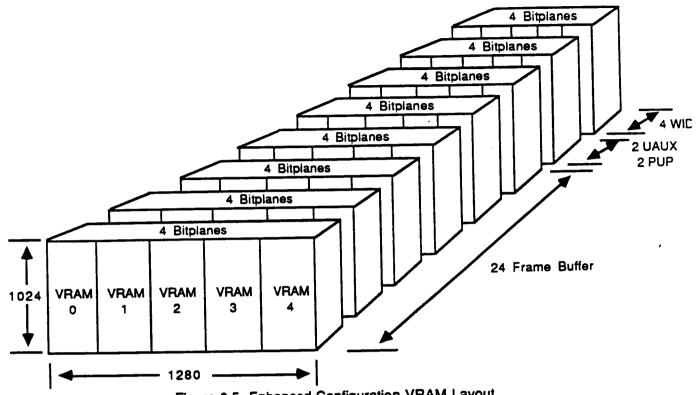

# **Enhanced Adapter Pixel Bitplanes**

The enhanced configuration of the MGR adapter contains 24 Frame Buffer bitplanes, 2 PUP bitplanes, 2 UAUX bitplanes and 4 WID bitplanes as shown in Figure 6.5. These bitplanes are contained in 40 VRAM chips. As described above the VRAMs are interleaved in five pixel groups.

Each VRAM provides 256 x 1024 x 4 pixels. The 2 PUP bitplanes and the 2 UAUX bitplanes are grouped in the same five VRAMs.

Figure 6.5 Enhanced Configuration VRAM Layout

# Frame Buffer Bitplanes

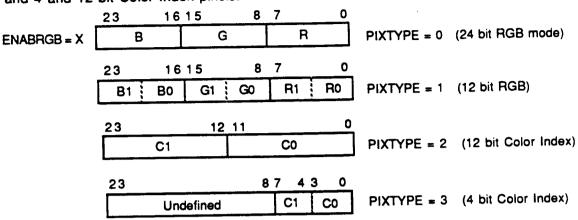

The Frame Buffer bitplanes are used by the host software to hold the normal display pixels which are transferred to the Display Subsystem for display. The RE2 supports both color index and RGB pixel formats as well as single and double buffer formats. The following pixel types are supported:

- 4 bit color index double buffer (both configurations, usually only the base configuration)

- 8 bit color index single buffer (base configuration only)

- 12 bit color index double buffer (enhanced configuration only)

- 8 bit RGB single buffer (base configuration only)

- 12 bit RGB double buffer (enhanced configuration only)

- 24 bit RGB single buffer (enhanced configuration only)

The GE\_PIXTYPE token is used to specify the pixel type. For the color index pixels the GE\_COLOR or GE\_COLORF token is used to specify the color index value. For RGB pixels the GE\_RGBCOLOR token is used to specify the red, green and blue color values which form the RGB pixels. The GE\_PIXWRITEMASK is used to specify the Frame Buffer pixel write mask. This mask is used to control which bits in the pixel are written. The host software uses the write mask to control whether the front or back buffer is written for double buffer pixels.

#### **PUP Bitplanes**

The PUP bitplanes are normally used by the host window manager software to display overlay or underlay pixels. The value written into the PUP bitplanes is used by the Display Subsystem as an index into the overlay color map. The GE\_COLOR or GE\_COLORF tokens are used to specify the index value. The GE\_AUXWRITEMASK token is used to specify the write mask for the PUP bitplanes. Bits 0 and 1 of the aux write mask are used to mask PUP writes.

### **UAUX** Bitplanes

The UAUX bitplanes are normally used by the user graphics application software to display overlay or underlay pixels. The value written into the UAUX bitplanes is used by the Display Subsystem as an index into the overlay color map. The GE\_COLOR or GE\_COLORF tokens are used to specify the index value. The GE\_AUXWRITEMASK token is used to specify the write mask for the UAUX bitplanes. Bits 2 and 3 of the aux write mask are used to mask UAUX writes. The host software can configure the PUP and UAUX bitplanes as 4 UAUX bitplanes.

### WID Bitplanes

The Window ID bitplanes are used by the host window manager to control pixel clipping for obscured windows. The LSB bit of the WID on the enhanced adapter is also used to perform Z value invalidation for fast Z clear operations. The Window ID is used by the Display Subsystem as an index into the mode registers of the XPC1 or XMAP2 chips to control pixel formatting operations during the pixel display operations. The GE\_COLOR or GE\_COLORF tokens are used to specify the window ID value. The GE\_AUXWRITEMASK token is used to specify the write mask for the WID bitplanes. Bits 4 through 7 of the aux write mask are used to mask WID bitplane writes.

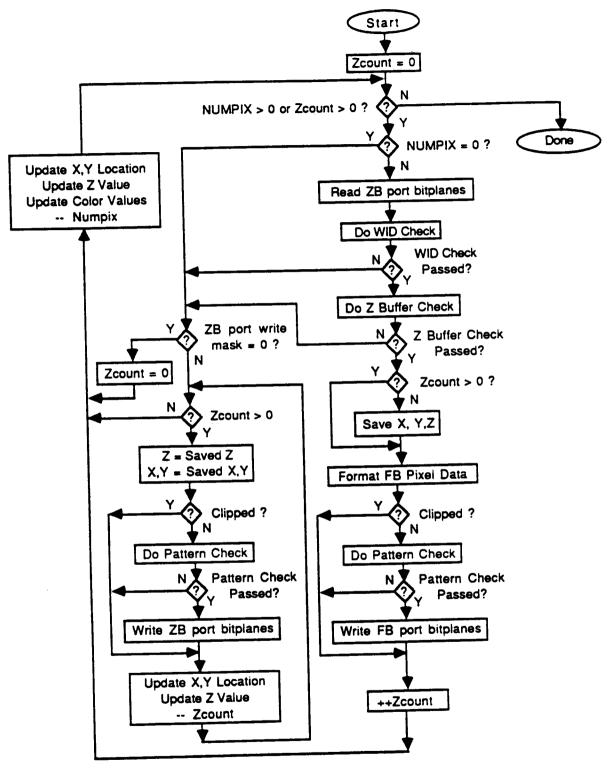

# Z Buffer Bitplanes

The Z buffer bitplanes are used to hold Z values for each pixel. The x and y locations of the pixel are used to select which pixel is written and the z value can be used to perform depth comparison operations. If Z buffer comparisons are enabled then the new Z value is compared to the existing Z value in the bitplanes. If the comparison passes then the new pixel value is written into the Frame Buffer bitplanes, the PUP bitplanes, the UAUX bitplanes and the WID bitplanes subject to the settings of the pixel and aux write masks. The aux write mask bit 8 is used to enable or disable the Z buffer writes. The GE\_ZBUFFER token is used to enable or disable Z buffer checks. The GE\_ZFUNCTION token is used to specify the comparison function. The GE\_AUXWRITEMASK is used to specify the write mask.

### **Cursor Chips**

The Raster Subsystem uses two Brooktree Bt431 cursor controller chips to generate a cursor which can be one of three colors or two separate 1 color cursors. The cursor can be either a user defined 64 x 64 bit glyph pattern or a cross hair pattern. Both the glyph pattern and the cross hair cursor pattern can be displayed simultaneously, with logical OR and exclusive-OR operations supported. Either cursor may be moved off the top, bottom, left or right side of the screen without wrap-around. The cross hair cursor may be implemented as a full screen or full window cross hair cursor.

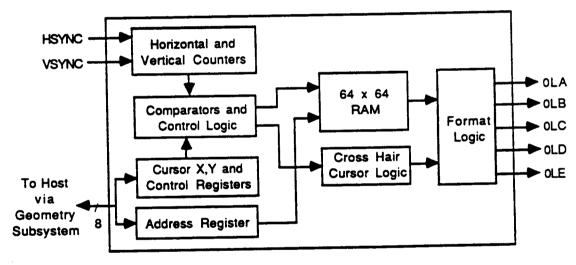

The cursor controller chip block diagram is shown in Figure 6.6. The cursor chip contains an address register and other control registers. The address register is used to select the other registers and the 64 x 64 bit RAM. The cursor chip contains Cursor X and Cursor Y registers which are loaded with the screen location at which the cursor is to displayed. The Horizontal and Vertical counters count the HSYNC and VSYNC signals from the Display State Machine in the Display Subsystem. The comparators and control logic compare the counter values with the Cursor X and Cursor Y values and when they are equal it enables the 64 x 64 bit RAM and cross hair logic circuits to produce the appropriate outputs. The Format logic is used to generate from 1 to 5 output signals that are used to select cursor colors.

Figure 6.6 Cursor Chip Block Diagram

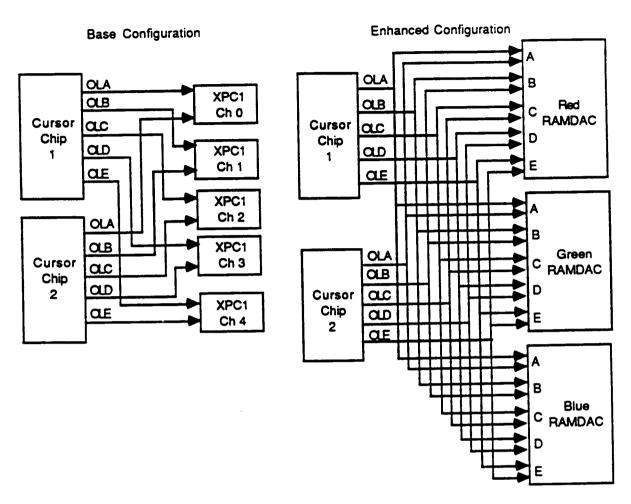

The MGR uses all five cursor output signals. The connections of the outputs from the two cursor chips is shown in Figure 6.7. In the base configuration, the five outputs from both cursor chips are connected to the five XPC1 chips. The cursor inputs to the XPC1 chips have the highest precedence in determine which color value will be displayed. If either cursor output bit is a 1 then the OVL output of the XPC1 chip processing the current pixel will be set to the two cursor chip output values and the OVL bits will be used by the RGB RAMDAC chip to select the cursor color from the overlay palette. If both cursor outputs are zero then the XPC1 will use the contents of the Frame Buffer bitplanes and the PUP bitplanes to determine the pixel color. In the enhanced configuration, the five outputs from both cursor chips are connected directly to the OL inputs of the three RAMDAC chips. The RAMDACs use the cursor inputs to select a value from the overlay palette. If both cursor inputs are zero then the RAMDACs use the color input byte to select a color palette entry. Refer to the Display Subsystem for a detailed description of the use of the cursor output bits.

Figure 6.7 Cursor Output Connections

The following paragraphs describe the host access to the cursor chip registers and the cursor chip basic operations.

# Host Access to the Cursor Chip Registers and Glyph RAM

The cursor controller chip contains Cursor X and Cursor Y registers which are used to position the center of the cursor on the screen. It also has an address register which is used to access the  $64 \times 64$  RAM and the other control registers. The control registers include a command register, a window X register, a window Y register, a window width register and a window height register. The host address map for these registers and the cursor RAM is shown in Table 6.1. The addresses are the offset address from the base address of the MGR adapter.

# Address Register

The address register is a 16 bit wide register which is used to access the other registers and the cursor glyph RAM in the cursor chip. The address register is written as two bytes called address register 0 and address register 1. The host software writes a byte to the addresses shown in Table 6.1 to place the address in the address register. Once the address register has been written the host can then read or write the register or glyph location whose address is in the address register.

| Host Address<br>Cursor Chip 0 | Host Address<br>Cursor Chip 1 | Cursor Address<br>Register 1-0 Value | Source/Destination          |

|-------------------------------|-------------------------------|--------------------------------------|-----------------------------|

| 560 Hex                       | 580 Hex                       | ×                                    | Cursor Address Register 0   |

| 564 Hex                       | 584 Hex                       | ×                                    | Cursor Address Register 1   |

| 568 Hex                       | 588 Hex                       | 000 - 1FF hex                        | Cursor Glyph RAM            |

| 56C Hex                       | 58C Hex                       | 00                                   | Command Register            |

| 56C Hex                       | 58C Hex                       | 01                                   | Cursor X Low Register       |

| 56C Hex                       | 58C Hex                       | 02                                   | Cursor X High Register      |

| 56C Hex                       | 58C Hex                       | 03                                   | Cursor Y Low Register       |

| 56C Hex                       | 58C Hex                       | 04                                   | Cursor Y High Register      |

| 56C Hex                       | 58C Hex                       | 0.5                                  | Window X Low Register       |

| 56C Hex                       | 58C Hex                       | 06                                   | Window X High Register      |

| 56C Hex                       | 58C Hex                       | 07                                   | Window Y Low Register       |

| 56C Hex                       | 58C Hex                       | 0.8                                  | Window Y High Register      |

| 56C Hex                       | 58C Hex                       | 09                                   | Window Width Low Register   |

| 56C Hex                       | 58C Hex                       | 0A hex                               | Window Width High Register  |

| 56C Hex                       | 58C Hex                       | 0B hex                               | Window Heigth Low Register  |

| 56C Hex                       | 58C Hex                       | 0C hex                               | Window Height High Register |

Table 6.1 Cursor Host Address Map

HQMMSB Register must be set to 1

## Cursor Glyph RAM

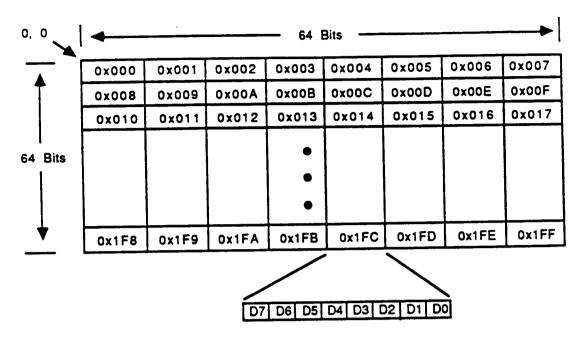

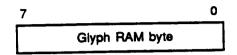

Each cursor chip has a 512 byte RAM which is used to store a 64 x 64 bit cursor glyph. This is also referred to as a block cursor. The glyph contains the cursor pixel bit pattern used to form the block cursor. The host software must initialize the cursor glyph after the MGR adapter is reset. The host software loads the byte address in the address register and then reads or writes the RAM location. After the RAM location has been read or written the address register is incremented. This allows the host software to set the address register to 0 and then do 512 writes to fill the RAM. If the address is 0x1FF it wraps to 0x000 after the read or write operation. The glyph RAM layout is shown in Figure 6.8.

The bit 7 location of byte 0 is the upper left corner of the block cursor as it will be displayed on the screen. The 64 bits in the x direction are contained in 8 bytes. The 64 bits in the y direction are contained in 64 rows of 8 bytes.

The upper left corner of the glyph RAM is the 0, 0 position and the lower left corner of the screen is the 0, 0 position for the graphics drawing operations. This means that the host software must reverse the bit pattern of the glyph in the y direction from the way it would define other bit patterns.

Figure 6.8 Cursor Glyph RAM Layout

## Command Register

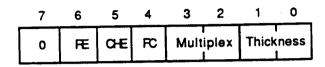

The command register is used by the host software to control the operation of the cursor chip. The command register is used enable either the block cursor or the cross hair cursor or both cursors. When both the block cursor and the cross hair cursor are enabled the command register is used to specify whether the intersecting pixels in the two cursors are logically ORed or exclusively ORed. The command register is also used to specify the pixel width of the cross hair cursor. The output multiplex control bits in the command register are used to select the number of output bits the cursor chip outputs on each clock cycle. The MGR adapter has the five pixel pipelines so the multiplex control bits should be set to for five outputs. The host reads or writes the command register by writing a 0 into the address registers and then reading or writing the cursor command register.

# Cursor X,Y Registers

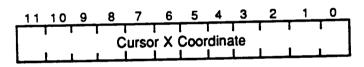

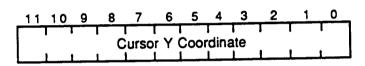

The cursor X,Y registers are used to specify the X and Y location of the center of the cursor glyph or the location where the cross hair cursor intersects. The cursor X and Y registers are 12 bit wide registers and are read or written as a low byte and a high byte. The host software writes a 1 into the address registers and then reads or writes the low byte of the cursor X register. The host then writes a 2 into the address registers and then reads or writes the high byte of the cursor X register. The host software writes a 3 into the address registers and then reads or writes the low byte of the cursor Y register. The host then writes a 4 into the address registers and then reads or writes the high byte of the cursor Y register. The new cursor location takes effect after the high byte of the cursor Y register is written.

# Window X,Y Register

The window X,Y registers are used to specify the X and Y location of the upper left corner of the cross hair cursor window. The cross hair window is used to specify the cursor cross hair cursor clipping rectangle. The window width and height registers are used to specify the window size. The

window X and Y registers are 12 bit wide registers and are read or written as a low byte and a high byte. The host software writes a 7 into the address registers and then reads or writes the low byte of the window Y register. The host then writes a 8 into the address registers and then reads or writes the high byte of the window Y register.

# Window Width and Height Registers

The window width register is a 12 bit register which is used to specify the width of the cross hair cursor window. The host software writes a 9 into the address registers and then reads or writes the low byte of the window width register. The host then writes an 0xA into the address registers and then reads or writes the high byte of the window width register. The window height register is a 12 bit register which is used to specify the height of the cross hair cursor window. The host software writes an 0xB into the address registers and then reads or writes the low byte of the window height register. The host then writes an 0xC into the address registers and then reads or writes the high byte of the window height register. The new window size takes effect after the high byte of the window height register is written.

# **Cursor Chip Basic Operations**

The cursor chip provides the capability to display either a  $64 \times 64$  bit block cursor or a cross hair cursor. Both the block cursor and the cross hair cursor can be displayed at the same time. The MGR adapter contains two cursor chips which allows either two block or cross hair cursors of the same color to be displayed at different locations on the screen or a single block cursor to be displayed on the screen with one to three colors. When both the cross hair cursor and the block cursor are enabled on the same cursor chip the intersecting pixels can be combined with a logical OR or a logical exclusive OR operation. The cursor X,Y registers are used to specify the screen location of the center of the block cursor and the intersection point for the cross hair cursor.

The cross hair cursor is displayed within the cross hair cursor window. The window width and height registers are used to specify the size of the cross hair cursor window. The window X,Y registers are used to specify the upper left corner of the cross hair cursor window. The thickness of the cross hair cursor can be specified in pixels. The width values are 1,3, 5 or 7 pixels and are specified by two bits in the command register.

The horizontal and vertical sync pulses generated by the Display State Machine are used by the cursor chip to determine the cursor outputs. The vertical sync marks the start of a new raster scan and resets the cursors y counter to zero. Each horizontal sync pulse resets the the cursors x counter to zero. The DSM generates pixel clock pulses for each pixel on the current scan line. The upper left corner of the screen is the 0.0 position and the positive x direction is to the right and the positive y direction is down the screen. The cursor compares the counter x,y values with the cursor X,Y register values.

For the block cursor the comparison begins at cursor X - 31 and Y - 31 and continues for the next 64 pixel locations in the x direction and the next 64 scan lines in the y direction. When the location comparison passes the cursor chip checks the contents of the cursor RAM to determine the output value. If the cursor RAM contains a zero bit at the X,Y location the five outputs are all set to zero. If the cursor RAM bit is a one then a one is output on all five outputs. For all screen locations outside the block cursor 64 x 64 bit locations the cursor chip generates zeroes on all five outputs.

For the cross hair cursor the comparisons begin at the window boundaries and are controlled by the cursor X, Y values and the thickness setting. For the pixels that are located on the cross hair cursor x and y locations the cursor chip generates a one on all five outputs. For all pixel locations which are not on the cross hair cursor the cursor chip generates zeroes on all five outputs.

## Registers

The following paragraphs describe the registers for the following Raster Subsystem components:

- RE2 chip

- Cursor chip

#### **RE2** Registers

The RE2 contains an instruction register and 56 control registers which are programmable by the GE5 microcode. The Instruction Register is loaded with the opcode of the command to be executed by the RE2. The other 56 registers are loaded with data which is used by the RE2 during the execution of the command. The host does not have the ability to directly program any of the RE2 registers. The ENABRGB and the TOPSCAN registers are the only registers that the host needs to program. The host uses the GE\_LOADRE token to load these two registers. The other registers are loaded by the microcode and should not be modified by the host software. The following registers have input buffers which allow multiple values to be written into them for multiple command execution:

- ENABRGB register: Specifies if 8 bit RGB pixels are to be used for 8 bitplane configuration

- BIGENDIAN register: Specifies the pixel packing order for the Write Buffer instruction

- FUNC register : Contains the raster op function

- HADDR register: Specifies the starting pixel offset in the first packed word

- NOPUP register: Specifies if 2 PUP and 2 UAUX bits or 0 PUP and 4 UAUX bits are used

- XYFRAC register: Contains the initial XY fractions bits for antialiased lines

- RGB register : Contains initial red, green and blue color values

- YX register : Contains the initial X and Y values

- PUPDATA register : Contains the 2 bit PUP data value

- PATL register : Contains the lower 16 bits of the pattern mask

- PATH register : Contains the upper 16 bits of the pattern mask

- DZI register : Contains the initial integer portion of the Delta Z value

- DZF register : Contains the fraction portion of the Delta Z value

- DR register : Contains the Delta Red value

- DG register : Contains the Delta Green value

- DB register : Contains the Delta Blue value

- Z register: Contains the initial Z value

- R register : Contains the initial Red value

- G register : Contains the initial Green value

- B register: Contains the initial Blue value

- STIP register : Contains the line Stipple pattern

- STIPCOUNT register : Contains the LSB stipple bit repeat count

- DX register : Contains the Delta X value

- DY register : Contains the Delta Y value

- NUMPIX register: Contains the pixel count for the instruction

- X register : Contains the initial X value

- Y register : Contains the initial Y value

- IR register: Contains the instruction to be executed

The following registers do not have input buffers and are generally not changed for each instruction:

- RWDATA register: The Read and Write Buffer instruction data register

- PIXMASK register : Contains the Frame Buffer pixel write mask

- AUXMASK register: Contains the PUP, UAUX, WID and Z buffer bitplanes write mask

- WIDDATA register : Contains the 2 or 4 bit WID data value

- UAUXDATA register : Contains the 2 or 4 bit UAUX data value

- RWMODE register : Specifies the source or destination bitplanes for the Read and Write Buffer instructions

- READBUF register : Selects which frame buffer is read by READBUF instruction

- PIXTYPE register : Selects the frame buffer pixel type

- ASELECT register : Selects the antialiasing weight

- ALIGNPAT register : Controls the pattern alignment

- ENABPAT register : Enables or disables the pattern mask

- ENABSTIP register: Enables or disables the line stipple pattern

- ENABDITH register : Enables or disables color dithering

- ENABWID register: Enables or disables WID checking for shaded span instructions

- CURWID register : Contains the current Window ID

- DEPTHFN register : Specifies the Z or color compare relational function

- REPSTIP register: Specifies the repeat count for all bits in the stipple count except LSB bit

- ENABLWID register: Enables or disables WID checking for Draw Line instructions

- FBOPTION register: Specifies if 8 or 24 bitplanes are installed

- TOPSCAN register: Specifies the number of columns and rows to be displayed on the screen

- ZBOPTION register: Specifies if the Z buffer card is installed or not

- XZOOM register : Specifies the X zoom repeat count for Write Buffer instructions

- UPACMODE register: Specifies the number of pixels/long word for Write Buffer instruction

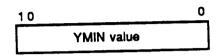

- YMIN register: Contains the bottom boundary of the hardware screen mask

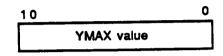

- YMAX register : Contains the top boundary of the hardware screen mask

- XMIN register: Contains the left boundary of the hardware screen mask

- XMAX register : Contains the right boundary of the hardware screen mask

- COLORCMP register : Controls the selection of the Z compare or the color compare

- MEGOPTION register: Specifies if 1 MEG or 256K VRAMs are installed

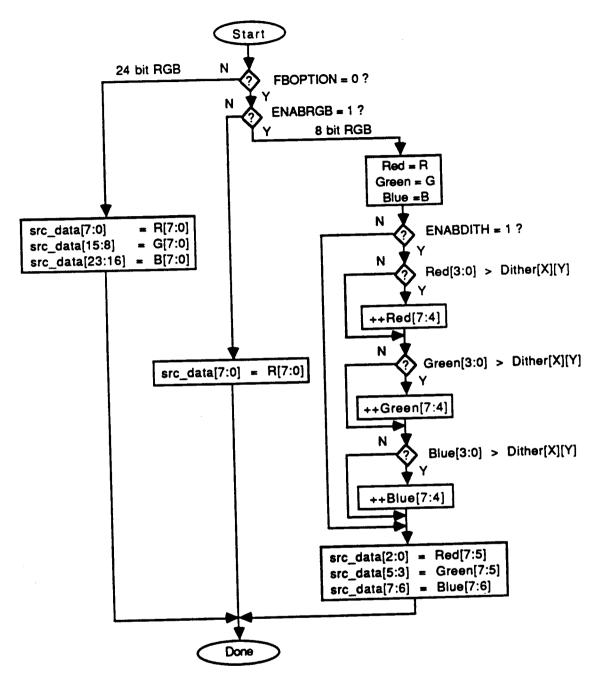

#### **ENABRGB Register**

This is a one bit register which is used to enable 8 bit RGB pixels. This register is ignored on the enhanced adapter when the FBOPTION register is set to one. When the FBOPTION register is set to zero for the base adapter the value in the ENABRGB register is used by the RE2. When this register is set to one the RE2 does the special 233 processing to form the 8 bit RGB pixels from the red, green and blue color bytes. The RE2 takes the most significant 2 bits of the blue color value and places them in the most significant 2 bits of the 8 bit RGB value. The most significant 3 bits of the green value are placed in the middle 3 bits of the 8 bit RGB value and the three most significant bits of the red value are placed in the three LSB bits of the 8 bit RGB value. When the ENABRGB register is zero the 8 bit RGB processing is not performed on the color values. Instead the 8 bit red value is placed in the 8 bit pixel values. The host software must set this register using the GE\_LOADRE token. It can be set at any time after the microcode has been downloaded and the three data parameters have been sent. The format of the 8 bit RGB register is shown in Figure 6.9.

Figure 6.9 ENABRGB Register

REptr index = 4

**Buffered Input Register**

Bit 0 : Enable 8 bit RGB (Write Only). This bit enables or disables 8 bit RGB mode on the base adapter.

FBOPTION = 0

0 - Disable 8 bit RGB mode 1 - Enable 8 bit RGB mode

FBOPTION = 1

X - ENABRGB register is ignored and normal 24 bit RGB processing is performed

#### **BIGENDIAN Register**

This is a 1 bit register that specifies the byte order for packed pixels for the Write Buffer instruction. When this register is set to one then the BIGENDIAN mode is enabled and the pixels are packed in the long words from left to right. When this register is a zero the BIGENDIAN mode is off and the pixels are packed right to left in the long words. Since the Eddy register provides the little endian to big endian byte ordering this register is always set to one for BIGENDIAN mode. The format of this register is shown in Figure 6.10.

Figure 6.10 BIGENDIAN Register

REptr index = 5

**Buffered Input Register**

Bit 0 : Enable Big Endian mode (Write Only). This bit enables or disables Big Endian mode.

- 0 Disable Big Endian mode

- 1 Enable Big Endian mode

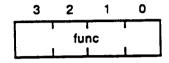

#### **FUNC** Register

This is a 4 bit register which is used to specify the Raster operation which is to be performed on the pixel data. The raster op is performed between the new pixel data (src) and the pixel data in the bitplanes (dst). The format of this register is shown in Figure 6.11.

Figure 6.11 FUNC Register

REptr index = 6

**Buffered Input Register**

Bits 3-0: func (Write Only). These bits specify the raster op function.

| bits | destination value          |

|------|----------------------------|

| 0000 | zero                       |

| 0001 | src AND dest               |

| 0010 | src AND (COMP dest)        |

| 0011 | SIC                        |

| 0100 | (COMP src) AND dest        |

| 0101 | dest                       |

| 0110 | src XOR dest               |

| 0111 | src OR dest                |

| 1000 | (COMP src) AND (COMP dest) |

| 1001 | (COMP src) XOR dest        |

| 1010 | COMP dest                  |

| 1011 | src OR (COMP dest)         |

| 1100 | COMP src                   |

| 1101 | (COMP src) OR dest         |

| 1110 | (COMP src) OR (COMP dest)  |

| 1111 | One                        |

COMP - 1's complement

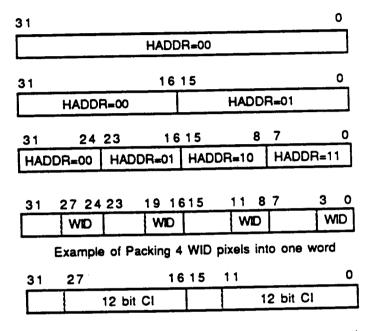

#### **HADDR** Register

This register is used to specify the starting pixel offset in the first long word DMAed to the RE2 to be written to the bitplanes. This register allows the host buffer to start on a byte or short boundary which is not long word aligned. The UPACMODE register specifies how many pixels per long word are in each long word received by the RE2. The format of this register is shown in Figure 6.12

Figure 6.12 HADDR Register

REptr index = 7

**Buffered Input Register**

Bits 1-0: haddr (Write Only). These bits specify the starting pixel location in the first packed long word. The following bit definitions assume big endian mode is selected.

00 - 1st byte or short pixel is starting pixel

01 - 2nd byte pixel is starting pixel

10 - 3rd byte pixel or 2nd short is the starting pixel

11 - 4th byte pixel is starting pixel

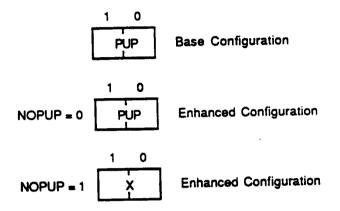

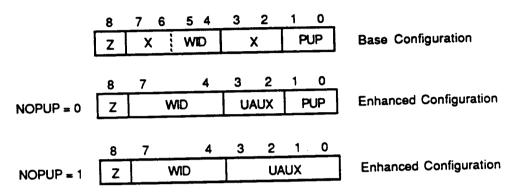

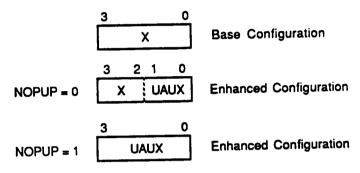

### **NOPUP** Register

This register is used to select either 2 PUP bits and 2 UAUX bits or 0 PUP bits and 4 UAUX bits. This register is only used on the enhanced configuration and is ignored on the base adapter. The format of this register is shown in Figure 6.13.

Figure 6.13 NOPUP Register

REptr index = 8

**Buffered Input Register**

Bit 0: NP (Write Only). This bit specifies the size of the UAUX bits on the enhanced adapter. When this bit is 0 the overlay bits consist of 2 PUP bits and 2 UAUX bits. When this bit is 1 the overlay bits consist of 0 PUP bits and 4 PUP bits. This bit is ignored on the base adapter. This register is always set to 0 in the MGR adapter since the microcode provides the same functionality.

0 - select 2 PUP and 2 UAUX bits

1 - select 0 PUP and 4 UAUX bits

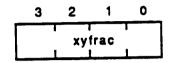

### XYFRAC Register

This register is used to improve the quality of antialiased lines. It is used to specify the initial fraction bits of the x or y axis that is changing slower on the antialiased line. The value in the register affects the value of the antialiasing weight used when drawing the first pixel on the line. This register allows the space between antialiased lines to appear constant on slow moving wireframes with closely spaced lines. The format of this register is shown in Figure 6.14.

Figure 6.14 XYFRAC Register

REptr index = 9

**Buffered Input Register**

Bits 3-0 : xyfrac (Write Only). These bits specify the initial xyfrac value used in antialiased lines.

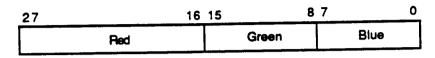

#### **RGB** Register

This register is used to hold the initial red, green and blue color values. This register allows the microcode to load the RGB values faster than using the R, G and B registers independently. This register is the same functionally as the separate R, G and B registers. The format of this register is shown in Figure 6.15.

Figure 6.15 RGB Register

REptr index = 0xA

**Buffered Input Register**

Bits 27-16: red (Write Only). These bits contain the initial red color.

Bits 15-8: green (Write Only). These bits contain the initial green color.

Bits 7-0: blue (Write Only). These bits contain the initial blue color.

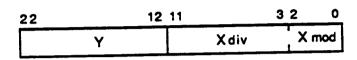

### YX Register

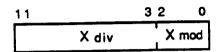

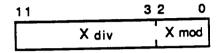

This register contains both the initial Y and X screen locations of the starting pixel location to be read or written by the next instruction. The X value is in the special DIVMOD format in which the X screen location is divided by 5 and the quotient is stored in the upper nine bits and the remainder is stored in the lower 3 bits of the X part of this register. The format of this register is shown in Figure 6.16.

Figure 6.16 YX Register

REptr index = 0xB

**Buffered Input Register**

Bits 22-12: Initial Y (Write Only). These bits contain the initial Y screen location.

Bits 11-0: Initial X (Write Only). These bits contain the initial X screen location.

### **PUPDATA** Register

This register is loaded with the data which is written into the PUP bitplanes. On the enhanced adapter (FBOPTION = 1) the NOPUP register controls whether the 2 PUP bits are used or not. If the NOPUP register is zero then the 2 PUP bits are used as well as 2 bits in the UAUX register. If the NOPUP register is a one then the 2 PUP bits are not used and 4 bits in the UAUX register are used instead. The format of this register is shown in Figure 6.17.

Figure 6.17 PUPDATA Register

REptr index = 0xC

**Buffered Input Register**

Bits 1-0: PUP (Write Only). These bits contain the PUP data bits.

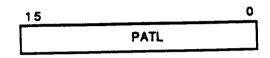

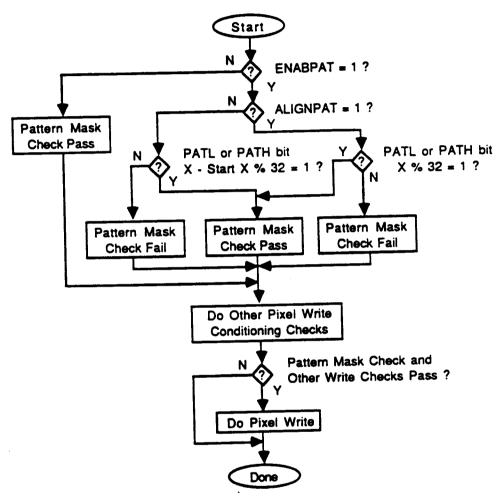

### **PATL** Register

This register contains the lower 16 bits of the 32 bit Pattern Mask register used by the Draw Shaded Span instruction to condition pixel writes with a texture pattern. When pattern masking is enabled with the ENABPAT register the pixels whose pattern mask bits are one are written and pixels whose pattern mask bits are zero are not written. If pattern masking is disabled the pattern mask bits are ignored as shaded span pixels are written. The ALIGNPAT register is used to control the pattern to screen pixels. The format of this register is shown in Figure 6.18.

Figure 6.18 PATL Register

REptr index = 0xD

Buffered Input Register

Bits 15-0: PATL (Write Only). These bits contain the lower 16 bits of the Pattern Mask.

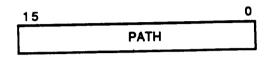

#### **PATH Register**

This register contains the upper 16 bits of the 32 bit Pattern Mask register used by the Draw Shaded Span instruction to condition pixel writes with a texture pattern. When pattern masking is enabled with the ENABPAT register the pixels whose pattern mask bits are one are written and pixels whose pattern mask bits are zero are not written. If pattern masking is disabled the pattern mask bits are ignored as shaded span pixels are written. The ALIGNPAT register is used to control the pattern to screen pixels. The format of this register is shown in Figure 6.19.

Figure 6.19 PATH Register

REptr index = 0xE

Buffered Input Register

Bits 15-0: PATH (Write Only). These bits contain the upper 16 bits of the Pattern Mask.

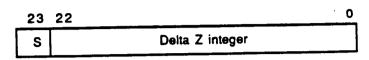

#### **DZI** Register

This register contains the integer portion of the delta Z value. This value is added to the Z value after each pixel is written to get the next Z value. The value in the register is a 24 bit 2's complement integer. The format of this register is shown in Figure 6.20.

Figure 6.20 DZI Register

REptr index = 0xF

**Buffered Input Register**

Bit 23: DZI sign bit (Write Only). This bit contains the sign bit for the integer portion of the delta Z value

Bits 22-0: DZI (Write Only). These bits contain the integer portion of the delta Z value

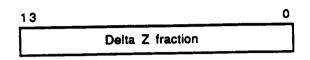

### **DZF** Register

This register contains the fraction portion of the delta Z value. This value is added to the fraction portion of the Z value after each pixel is written to get the next fractional part of the Z value. If the result of adding the two fractional parts is greater than 1 then the integer portion of the Z is incremented. The format of this register is shown in Figure 6.21.

Figure 6.21 DZF Register

REptr index = 0x10

Buffered Input Register

Bits 13-0: DZF (Write Only). These bits contain the fraction portion of the delta Z value

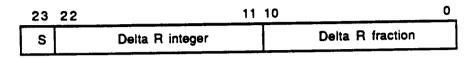

#### **DR** Register

This register contains the delta Red color value which is added to the Red color value after the current pixel is written to get the next Red color value. The integer portion of this register is a 2's complement integer. The integer portion of this register is 12 bits wide because it is used for the color index values for color index pixels. The format of this register is shown in Figure 6.22.

Figure 6.22 DR Register

REptr index = 0x11

**Buffered Input Register**

Bit 23: DR sign bit (Write Only). This bit contains the sign bit for the integer portion of the delta R value

Bits 22-11: DR integer (Write Only). These bits contain the integer portion of the delta R value

Bits 10-0: DR fraction (Write Only). These bits contain the fraction portion of the delta R value

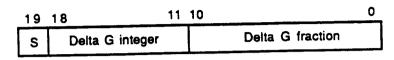

### **DG** Register

This register contains the delta Green color value which is added to the Green color value after the current pixel is written to get the next Green color value. The integer portion of this register is a 2's complement integer. The format of this register is shown in Figure 6.23.

Figure 6.23 DG Register

REptr index = 0x12

**Buffered Input Register**

Bit 19: DG sign bit (Write Only). This bit contains the sign bit for the integer portion of the delta G value

Bits 18-11: DG integer (Write Only). These bits contain the integer portion of the delta G value

Bits 10-0: DG fraction (Write Only). These bits contain the fraction portion of the delta G value

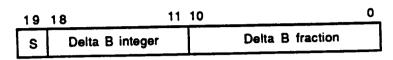

# **DB** Register

This register contains the delta Blue color value which is added to the Blue color value after the current pixel is written to get the next Blue color value. The integer portion of this register is a 2's complement integer. The format of this register is shown in Figure 6.24.

Figure 6.24 DB Register

REptr index = 0x13

**Buffered Input Register**

Bit 19: DB sign bit (Write Only). This bit contains the sign bit for the integer portion of the delta B value

Bits 18-11: DB integer (Write Only). These bits contain the integer portion of the delta B value

Bits 10-0: DB fraction (Write Only). These bits contain the fraction portion of the delta B value

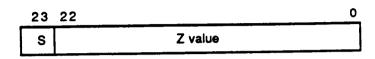

### **Z** Register

This register contains the integer portion of the initial Z value. This value is used for the Z buffer checks and is written to the Z buffer along with the other pixel bits if the Z check passes. The delta Z value is added to the Z value after each pixel is written to get the next Z value. The value in the register is a 24 bit 2's complement integer. The format of this register is shown in Figure 6.25.

Figure 6.25 Z Register

REptr index = 0x14

**Buffered Input Register**

Bit 23: Z sign bit (Write Only). This bit contains the sign bit for the integer portion of the initial Z value

Bits 22-0 : Z (Write Only). These bits contain the integer portion of the initial Z value

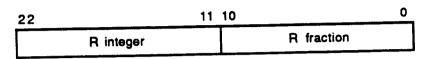

#### R Register

This register contains the initial Red color value which is used as the Red color component of the RGB pixels or as the color index for color index pixels. The delta Red color value is added to the Red color value after the current pixel is written to get the next Red color value. The format of this register is shown in Figure 6.26.

Figure 6.26 R Register

REptr index = 0x15

**Buffered Input Register**

Bits 22-11: R integer (Write Only). These bits contain the integer portion of the Red color value

Bits 10-0: R fraction (Write Only). These bits contain the fraction portion of the Red value

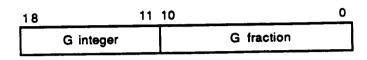

### **G** Register

This register contains the initial Green color value which is used as the green color component of the RGB pixels. The delta Green value is added to the Green color value after the current pixel is written to get the next Green color value. The format of this register is shown in Figure 6.27.

Figure 6.27 G Register

REptr index = 0x16

**Buffered Input Register**

Bits 18-11: G integer (Write Only). These bits contain the integer portion of the Green color value

Bits 10-0 : G fraction (Write Only). These bits contain the fraction portion of the Green color value

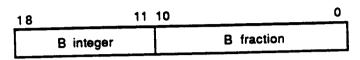

# **B** Register

This register contains the initial Blue color value which is used as the blue color component of RGB pixels. The delta Blue value is added to the Blue color value after the current pixel is written to get the next Blue color value. The format of this register is shown in Figure 6.28.

Figure 6.28 B Register

REptr index = 0x17

**Buffered Input Register**

Bits 18-11: B integer (Write Only). These bits contain the integer portion of the Blue color value

Bits 10-0: DB fraction (Write Only). These bits contain the fraction portion of the B color value

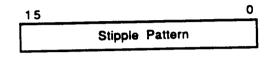

#### STIP Register

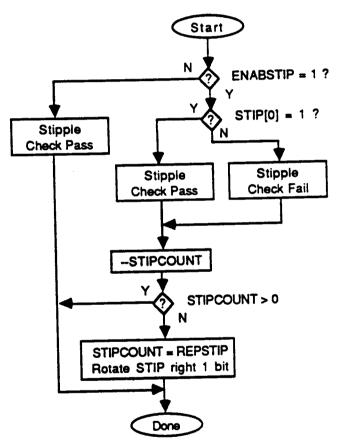

This register is used to hold the 16 bit line stipple pattern. When stipple conditioning is enabled with the ENABSTIP register the LSB bit is used to determine if the pixel is written during Draw Line instructions. If the LSB bit in the STIP register is a one the pixel is written if it is a zero the pixel is not written. The STIPCOUNT register determines how many times the initial LSB bit is used before the STIP register is rotated right one bit. For the remaining bits in the STIP register the REPSTIP register contains the repeat count for how many times each of those bits will be used to condition pixel writes before the STIP register is rotated right again. The format of this register is shown in Figure 6.29.

Figure 6.29 STIP Register

REptr index = 0x18

**Buffered Input Register**

Bits 15-0: Stipple Pattern (R/W). These bits contain the line stipple pattern.

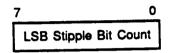

# STIPCOUNT Register

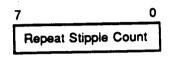

This register contains the repeat count for the LSB bit in the STIP register. When stipple checking is enabled with the ENABSTIP register the STIPCOUNT register determines how many pixel writes will be conditioned by the LSB bit in the STIP register before the STIP register is rotated right. The stipple pattern is used to condition pixel writes for the Draw Line instructions. The format of this register is shown in Figure 6.30.

Figure 6.30 STIPCOUNT Register

REptr index = 0x19

**Buffered Input Register**

Bits 7-0: LSB Bit Stipple Count (R/W). These bits contain the repeat count for the LSB bit in the stipple pattern register.

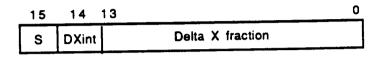

#### **DX** Register

This register contains the delta X value. This value is added to the X value after each pixel is written to get the next X value. If the result of adding the two fractional parts is greater than 1 then the integer portion of the X value is incremented. The integer portion of this register is a 2 bit 2's complement format. The format of this register is shown in Figure 6.31.

Figure 6.31 DX Register

REptr index = 0x1A

Buffered Input Register

Bit 15: DX sign bit (Write Only). This bit contains the sign bit for the delta X value

Bit 14: DX integer (Write Only). This bit contains the integer portion of the delta X value

Bits 13-0: DX fraction (Write Only). These bits contain the fraction portion of the delta X value

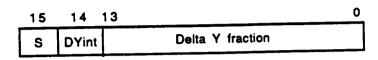

#### DY Register

This register contains the delta Y value. This value is added to the Y value after each pixel is written to get the next Y value. If the result of adding the two fractional parts is greater than 1 then the integer portion of the Y value is incremented. The integer portion of this register is a 2 bit 2's complement format. The format of this register is shown in Figure 6.32.

Figure 6.32 DY Register

REptr index = 0x1B

Buffered Input Register

Bit 15: DY sign bit (Write Only). This bit contains the sign bit for the delta Y value

Bit 14: DY integer (Write Only). This bit contains the integer portion of the delta Y value

Bits 13-0: DY fraction (Write Only). These bits contain the fraction portion of the delta Y value

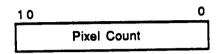

#### **NUMPIX** Register

This register is used as a pixel counter by the RE2. The number of pixels to be read or written during the next instruction are written into this register. As each pixel is read or written the NUMPIX register is decremented. When the count becomes zero the instruction execution terminates. The format of this register is shown in Figure 6.33.

Figure 6.33 NUMPIX Register

REptr index = 0x1C

**Buffered Input Register**

Bits 10-0: Pixel Count (Write Only). These bits contain the pixel count for the current instruction being executed.

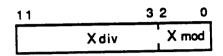

### X Register

This register contains the initial X screen location of the starting pixel location to be read or written by the next instruction. The X value is in the special DIVMOD format in which the X screen location is divided by 5 and the quotient is stored in the upper nine bits and the remainder is stored in the lower 3 bits of this register. The format of this register is shown in Figure 6.34.

Figure 6.34 X Register

REptr index = 0x1D

**Buffered Input Register**

Bits 11-0: Initial X (Write Only). These bits contain the initial X screen location.

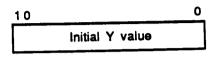

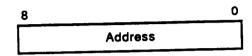

### Y Register

This register contains the initial Y screen location of the starting pixel location to be read or written by the next instruction. The format of this register is shown in Figure 6.35.

Figure 6.35 Y Register

REptr index = 0x1E

**Buffered Input Register**

Bits 10-0: Initial Y (Write Only). These bits contain the initial Y screen location.

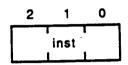

#### iR Register

This register is loaded with the instruction which the microcode wants the RE2 to execute. When the instruction is loaded into the IR register the RE2 will execute it as soon as it completes the previous instruction execution. The format of this register is shown in Figure 6.36.

Figure 6.36 IR Register

REptr index = 0x1F

**Buffered Input Register**

Bits 2-0: Inst (Write Only). These bits contain the instruction to be executed by the RE2.

000 - Undefined

001 - Draw Shaded Span

010 - Draw 1 x 5 Flat Span

011 - Draw 1 x 20 Flat Span (Block Write Mode)

100 - Draw Top of Antialiased Line

101 - Draw Bottom of Antialiased Line

110 - Read Buffer

111 - Write Buffer

#### **RWDATA** Register

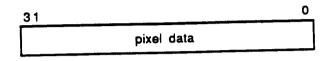

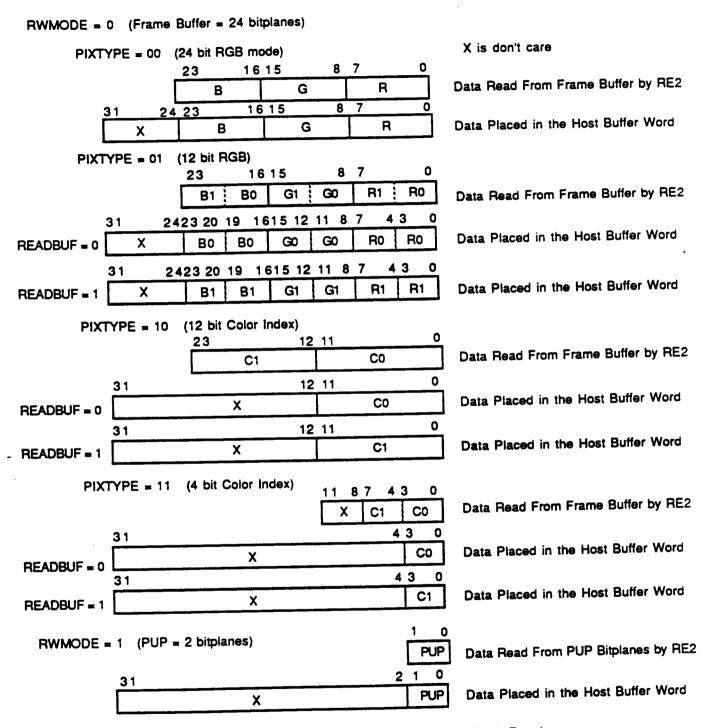

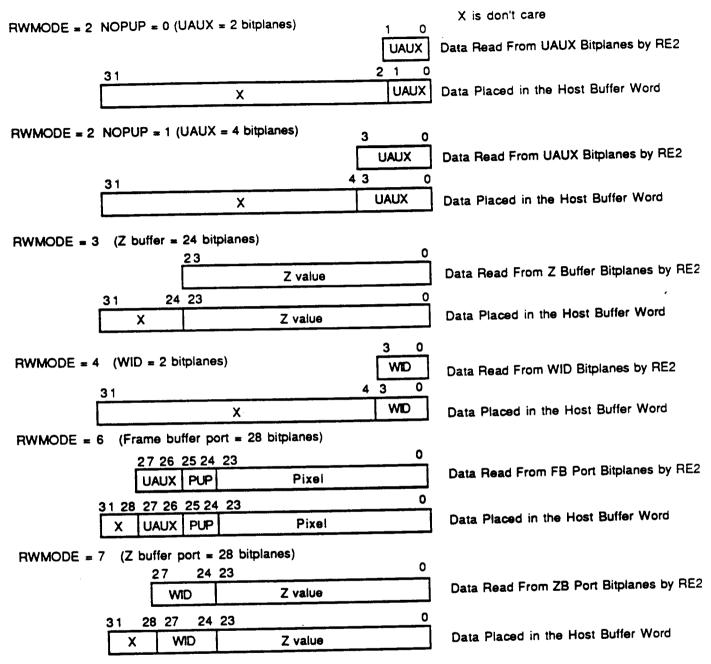

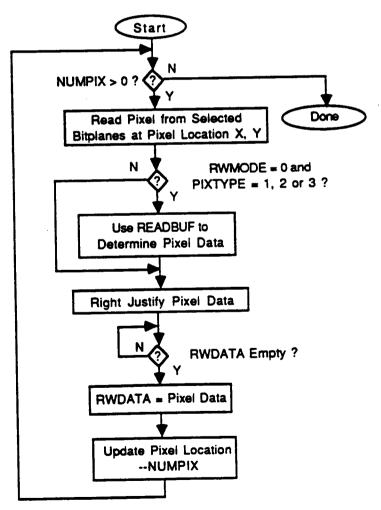

This register is the data register used by the read buffer and write buffer instruction. The data to be written into the bitplanes is written by the DMA hardware into this register and the RE2 then takes the value from the RWDATA register and writes it to the bitplanes selected by the RWMODE register. The read buffer instruction reads the selected bitplanes and places the data into the RWDATA register. The DMA hardware then transfers the data from the register to the host buffer or to the pixel buffer in the GE5 data RAM. The format of the register is shown in Figure 6.37.

Figure 6.37 RWDATA Register

REptr index = 0x20

Unbuffered Input Register

Bits 31-0: pixel data (R/W). These bits contain the pixel data read from the bitplanes or to be written to the bitplanes. For pixel writes all 32 bits can be used while only the right most 28 bits will be used for pixel reads.

# PIXMASK Register

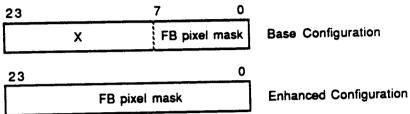

This register contains the Frame Buffer pixel write mask which controls which bits in the pixel data is written into the Frame Buffer bitplanes. The pixel write mask is used to select either a single buffer write or a double buffer write. For the double buffer write the front or back buffer is selected for writing with the value in the pixel write mask. The format of this register is shown in Figure 6.38.

Figure 6.38 PIXMASK Register

REptr index = 0x21

Unbuffered Input Register

Bits 23-0 : pixmask (Write Only). These bits contain the Frame Buffer pixel write mask.

0x0000FF - write to all the base adapter Frame Buffer bitplanes

0xFFFFFF - write to all the enhanced adapter Frame Buffer bitplanes

0xFFFFFF - write to all bits of PIXTYPE = 0 (24 bit RGB)

0x0000FF - write to all bits of PIXTYPE = 0 (8 bit RGB)

0x0F0F0F - write to the front buffer with PIXTYPE = 1 (12 bit RGB)

0xF0F0F0 - write to the back buffer with PIXTYPE = 1 (12 bit RGB)

0x000FFF - write to the front buffer with PIXTYPE = 2 (8 or 12 bit CI)

0xFFF000 - write to the back buffer with PIXTYPE = 2 (8 or 12 bit CI)

0x0000FF - write to the front buffer with PIXTYPE = 3 (4 bit CI)

0x0000FO - write to the back buffer with PIXTYPE = 3 (4 bit CI)

# **AUXMASK Register**

This register contains the write mask which is used to control which bits are written into the PUP bitplanes, the UAUX bitplanes, the WID bitplanes and the Z Buffer bitplanes. For the PUP bitplanes the UAUX bitplanes and the WID bitplanes the bits in the aux mask are used to mask individual bits. For the Z Buffer bitplanes a single mask bit is used to enable or disable writes into all 24 Z Buffer bitplanes. The format of this register is shown in Figure 6.39.

Figure 6.39 AUXMASK Register

REptr index = 0x22

Unbuffered Input Register

Bits 8-0 : auxmask (Write Only). These bits contain the write mask for the PUP bitplanes, the UAUX bitplanes, the WID bitplanes and the Z Buffer bitplanes.

0x003 - to write to just the PUP bitplanes

0x00C - to write to just the UAUX bitplanes

0x00F - to write to just the UAUX bitplanes with NOPUP =1 and FBOPTION = 1

0x0F0 - to write to just the WID bitplanes

0x100 - to write to just the Z Buffer bitplanes

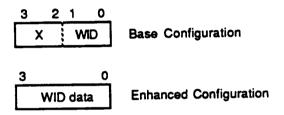

#### WIDDATA Register

This register contains the WID data which is written into the WID bitplanes if the WID mask bits in the AUXMASK register are set to one. The GE\_DRAWMODE token is used to specify the WID draw mode and then the GE\_COLOR or GE\_COLORF tokens are used to specify the index value to be written into the WIDDATA register. The WID data written into the WID bitplanes is used to condition pixel writes for the shaded span, draw line, and write buffer instructions. The LSB bit of the WID data in the WID bitplanes can also be used as a Z buffer invalidate bit for fast Z clears. This condition is enabled or disabled with bit 3 of the DEPTHFN register. The WID data is also used as an index for the mode registers in the XPC1 or XMAP2 chips in the Display Subsystem. The mode registers control the pixel display formatting thus the WID data bits control the pixel formatting for the various on screen windows. The format of the WIDDATA register is shown in figure 6.40.

Figure 6.40 WIDDATA Register

REptr index = 0x23

Unbuffered Input Register

Bits 3-0: WID data (Write Only). These bits contain the Window ID data bits.

#### **UAUXDATA** Register

This register contains the UAUX data which is written into the UAUX bitplanes if the UAUX mask bits in the AUXMASK register are set to one. The GE\_DRAWMODE token is used to specify the OVER draw mode and then the GE\_COLOR or GE\_COLORF tokens are used to specify the index value to be written into the UAUXDATA register. The UAUX data written into the UAUX bitplanes is used as an index for the overlay palette registers in the RGB RAMDAC chip or the overlay color map registers in the XMAP2 chips in the Display Subsystem. The index value selects an overlay or underlay color value if the overlay or underlay conditions are satisfied. The format of the UAUXDATA register is shown in figure 6.41.

Figure 6.41 UAUXDATA Register

REptr index = 0x24

Unbuffered Input Register

Bits 3-0: UAUX data (Write Only). These bits contain the UAUX data bits.

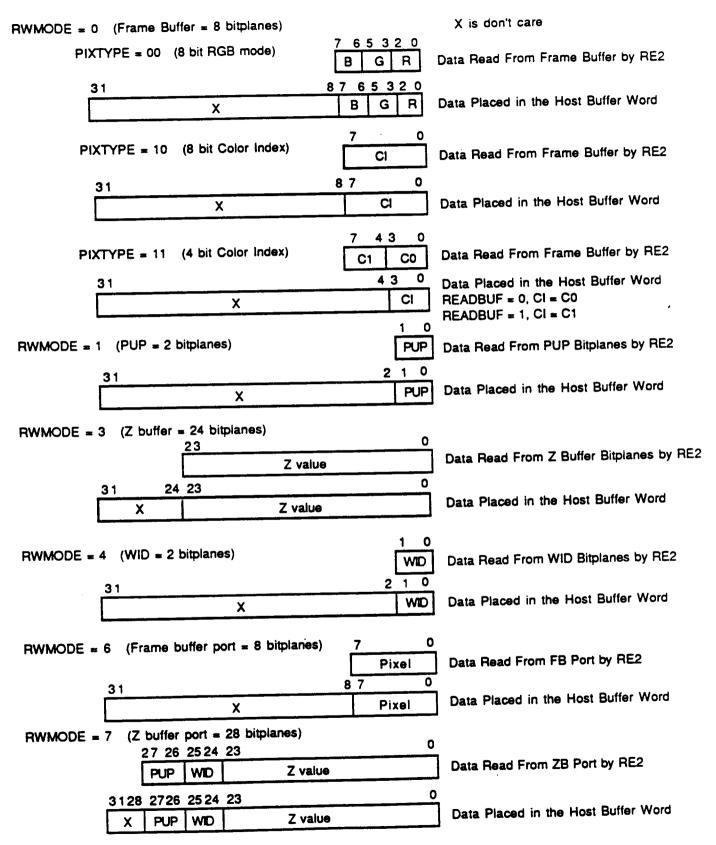

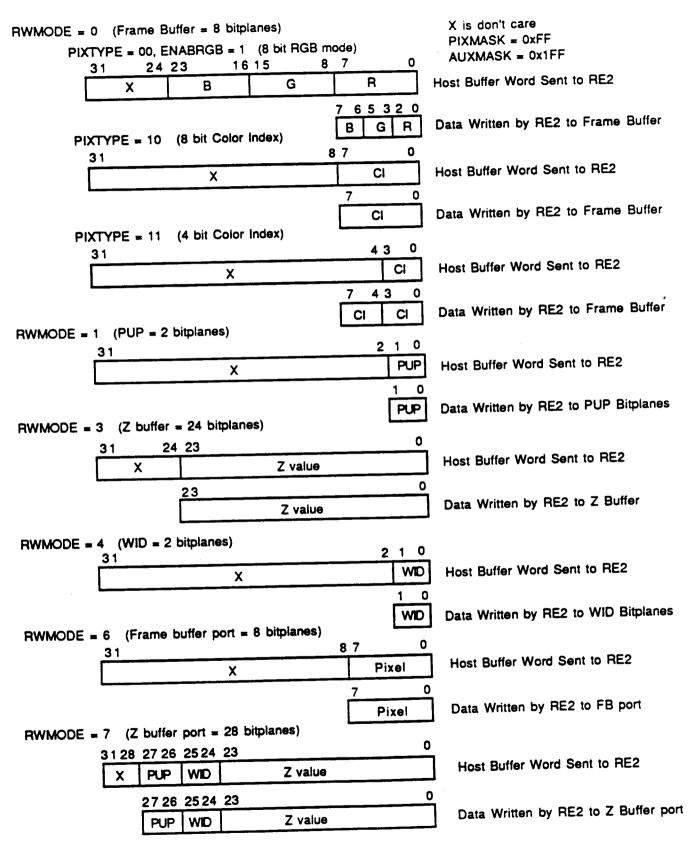

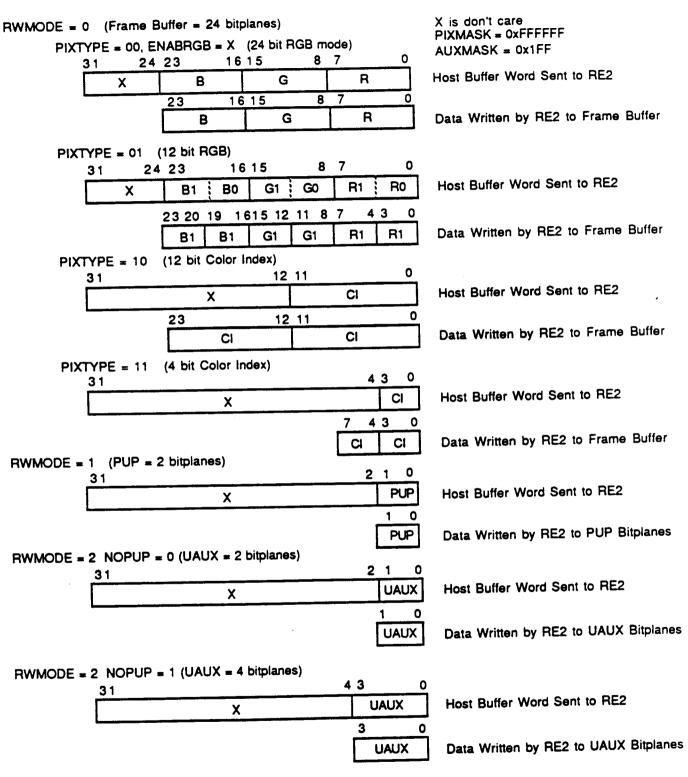

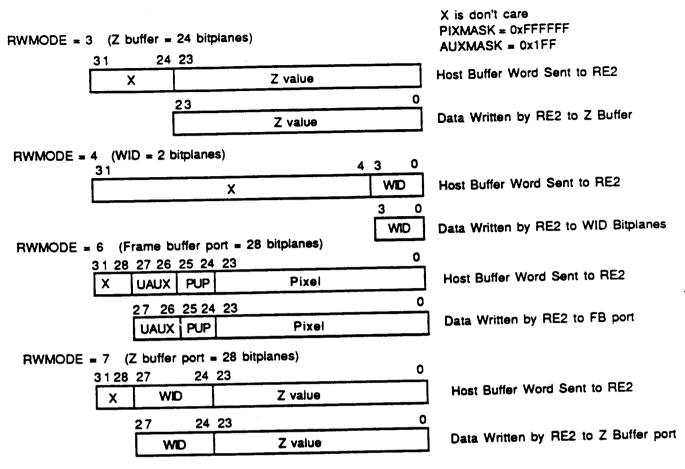

# **RWMODE** Register

This register specifies the source bitplanes for the Read Buffer instruction and specifies the destination bitplanes for the Write Buffer bitplanes. The format of this register is shown in Figure 6.42.

Figure 6.42 RWMODE Register

REptr index = 0x25

Unbuffered Input Register

Bits 2-0: rwmode (Write Only). These bits specify the source or destination bitplanes to be read or written.

000 - Frame buffer bitplanes

001 - PUP bitplanes

010 - UAUX bitplanes

011 - Z buffer bitplanes

100 - Window ID (WID) bitplanes

101 - invalid

110 - Frame buffer port

111 - Z buffer port

### **READBUF Register**

This register specifies which buffer is read by the Read Buffer instruction when the RWMODE register specifies the Frame Buffer as the read source bitplanes. The format of this register is shown in Figure 6.43.

Figure 6.43 READBUF Register

REptr index = 0x26

Unbuffered Input Register

Bit 0 : RB (Write Only). This bit specifies which Frame Buffer bitplane buffer is read by the Read Buffer instruction.

0 - read front buffer 1 - read back buffer

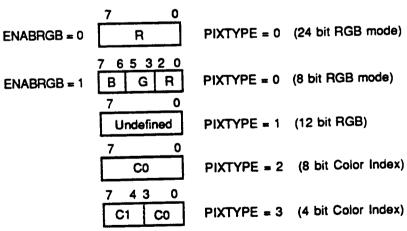

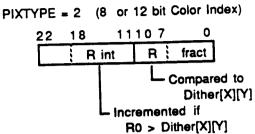

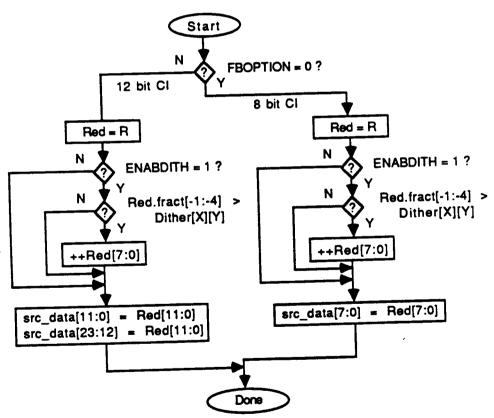

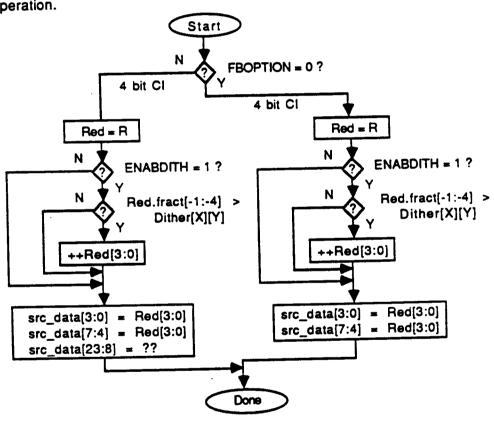

# PIXTYPE Register

This register specifies the type of pixel formatting that is performed on the R, G and B registers to form the Frame Buffer pixel data which is written into the Frame Buffer bitplanes. The format of this register is shown in Figure 6.44.

Figure 6.44 PIXTYPE Register

REptr index = 0x27

Unbuffered Input Register

Bits 1-0: pixtype (Write Only). These bits specify the pixel formatting performed on the color components to form the pixel data written into the Frame Buffer bitplanes.

00 - 8 bit RGB single buffer pixel if FBOPTION = 0

00 - 24 bit RGB single buffer pixel if FBOPTION = 1

01 - 12 bit RGB double buffer pixel (FBOPTION =1 only)

10 - 8 bit CI single buffer pixel (FBOPTION = 0)

10 - 12 bit CI double buffer pixel (FBOPTION = 1)

11 - 4 bit Cl double buffer pixel (FBOPTION = 0 or 1)

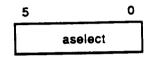

# **ASELECT** Register

This register contains antialiase weight usage control bits. The 3 most significant bits of the fraction part of the X or Y minor axis (slower changing axis) are used to select a 4 bit antialiase weight value which can be used to replace any nibble in the 24 bit Frame Buffer pixel value. The ASELECT register is used to select which of the six nibbles are replaced by the antialiase weight value. A 1 bit in any of the six bits in the ASELECT register causes the weight to replace the corresponding nibble. The format of the register is shown in Figure 6.45.

Figure 6.45 ASELECT Register

REptr index = 0x28

Unbuffered Input Register

Bits 5-0 : aselect (Write Only). These bits contain the antialiase weight replacement control bits.

000000 - No nibbles replaced with the weight 000001 - Replace nibble 0 with weight in 24 bit Frame Buffer pixel 000010 - Replace nibble 1 with weight in 24 bit Frame Buffer pixel 000100 - Replace nibble 2 with weight in 24 bit Frame Buffer pixel 001000 - Replace nibble 3 with weight in 24 bit Frame Buffer pixel 010000 - Replace nibble 4 with weight in 24 bit Frame Buffer pixel 100000 - Replace nibble 5 with weight in 24 bit Frame Buffer pixel 111111 - Replace all six nibbles with weight in 24 bit Frame Buffer pixel 000011 - Replace nibbles 0 and 1 with weight for double buffer 4 bit Cl pixel 001001 - Replace nibbles 0 and 3 with weight for double buffer 12 bit Cl pixel

# **ALIGNPAT** Register

This register controls the pixel alignment of the 32 bit pattern mask. The pattern can be either screen pixel location aligned or relative drawing aligned. The patterned polygons are drawn with screen alignment and characters are drawn with relative alignment. When screen alignment is selected the pattern mask is applied to each group of 32 pixels on the current scan line beginning with the left most pixel. When drawing relative alignment is selected the pattern mask is applied beginning with the starting X, Y pixel location. Each bit in the pattern mask is used by the shaded span instruction to condition a pixel write. If the current bit in the pattern mask is one the pixel is written and if it is zero the pixel is not written. The format of the ALIGNPAT register is shown in Figure 6.46.

Figure 6.46 ALIGNPAT Register

REptr index = 0x29

Unbuffered Input Register

Bit 0 : alignment (Write Only). This bit controls the pattern mask alignment.

0 - use drawing relative alignment (characters)

1 - use screen alignment (textured polygons)

#### **ENABPAT Register**

This register is used to enable or disable the use of the pattern mask for the shaded span and write buffer instructions. When enabled the 32 bit pattern mask contained in the PATH and PATL registers is applied with the alignment specified in the ALIGNPAT register to condition pixel writes. The format of this register is shown in Figure 6.47.

Figure 6.47 ENABPAT Register

REptr index = 0x2A

Unbuffered Input Register

Bit 0 : Enable Pattern (Write Only). This bit is used to enable or disable pattern masking.

0 - disable pattern masking

1 - enable pattern masking

# **ENABSTIP** Register

This register is used to enable or disable the use of the stipple pattern for the draw line instructions. When enabled the 16 bit stipple pattern contained in the STIP register is applied with the repeat counts specified in the STIPCOUNT and REPSTIP registers to condition pixel writes. The format of this register is shown in Figure 6.48.

Figure 6.48 ENABSTIP Register

REptr index = 0x2B

Unbuffered Input Register

Bit 0 : Enable Stip (Write Only). This bit is used to enable or disable the use of the stipple pattern when drawing lines.

0 - disable stipple pattern

1 - enable stipple pattern

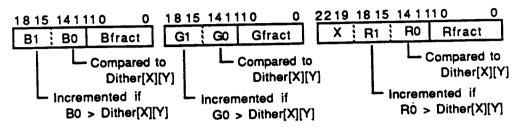

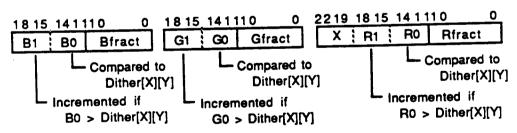

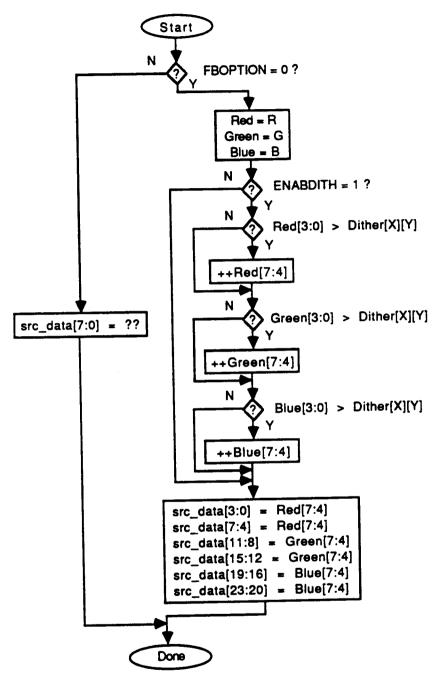

#### **ENABDITH Register**

This register is used to enable or disable the dithering operations during the Frame Buffer pixel calculations. When enabled the dither matrix is indexed by the four MSB fraction bits for color index pixels or the LSB nibble for 12 bit RGB pixels. The dither matrix value is compared to the index value and if the index value is greater than the index value the integer component of the color registers is incremented. The format of this register is shown in Figure 6.49.

Figure 6.49 ENABDITH Register

REptr index = 0x2C

Unbuffered Input Register

Bit 0 : Enable Dither (Write Only). This bit is used to enable or disable the dithering operations.

0 - disable dithering

1 - enable dithering

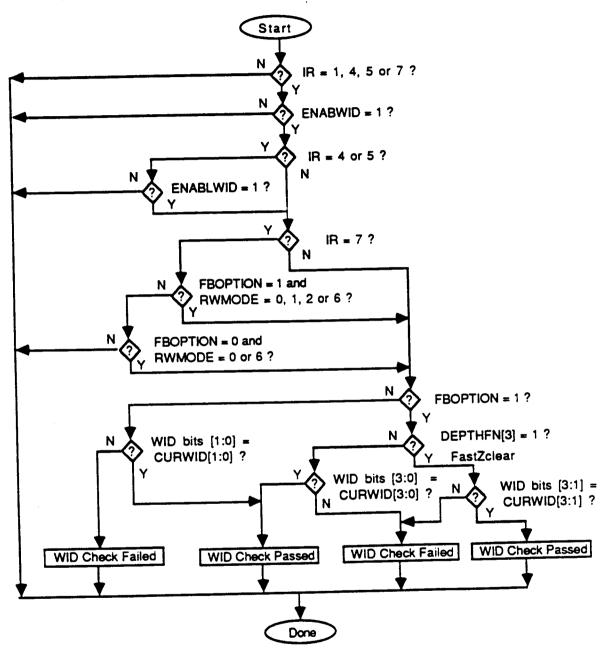

### **ENABWID Register**

This register is used to enable or disable the WID checking for the various instructions which allow WID checking. The ENABLWID register also must be enabled for line drawing WID checking. When enabled the value in the WID bitplanes at the current X, Y location are compared to the value in the CURWID register. If the values are the same the WID check passes. If the values are different the WID check fails. The format of this register is shown in Figure 6.50.

Figure 6.50 ENABWID Register

REptr index = 0x2D

Unbuffered input Register

Bit 0 : Enable WID check (Write Only). This bit is used to enable or disable WID checking.

0 - disable WID checking

1 - enable WID checking

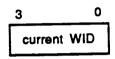

#### **CURWID** Register

This register contains the current WID value which is compared to the WID data in the WID bitplanes when WID checking is enabled. The WID check passes if the WID data value is the same as the value in the CURWID register. If the two values are different the WID check fails. If the WID check passes the pixel write depends on the other pixel write conditioning checks. If the WID check fails the pixel is not written. If WID checking is disabled the WID check automatically passes. The format of this register is shown in Figure 6.51.

Figure 6.51 CURWID Register

REptr index = 0x2E

Unbuffered Input Register

Bits 3-0 : Current WID (Write Only). These bits contain the current WID value to be compared to the WID bitplane data during WID checking operations.

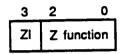

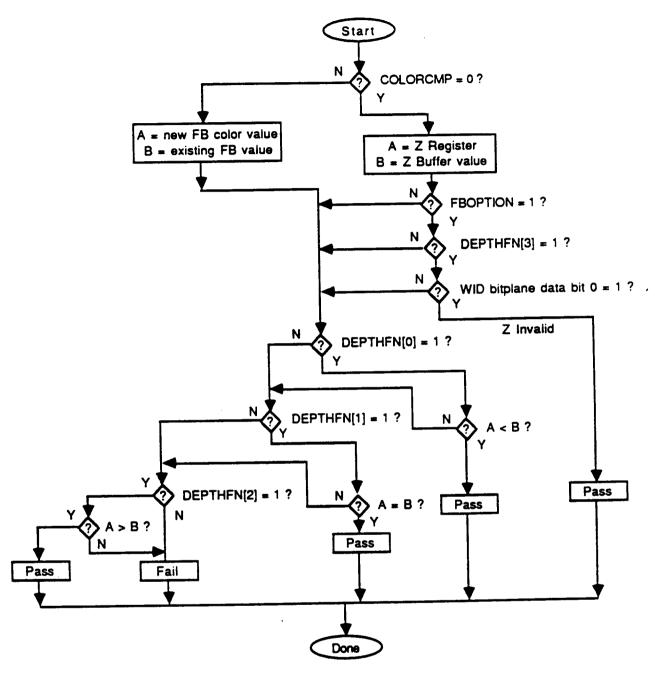

# **DEPTHFN** Register

This register specifies the relational comparison function which is performed by the Z comparator hardware. If the COLORCMP register is zero the new Z value is compared to the Z value in the Z Buffer. If the COLORCMP register is one the new Frame Buffer pixel value is compared to the color value already in the Frame Buffer. Bit 3 of the DEPTHFN register is used to enable or disable the use of the LSB bit of the WID bitplane data to invalidate the Z value for a fast Z clear operation. The format of this register is shown in Figure 6.52.

Figure 6.52 DEPTHFN Register

REptr index = 0x2F

Unbuffered Input Register

Bits 3: Z invalidate (Write Only). This bit specifies if the Z value is valid or not.

0 - disable old Z invalidate

1 - enable old Z invalidate if (WID LSB = 1)

Bits 2-0 : Depth function (Write Only). These bits specify the relational comparison function performed by the Z comparator hardware.

000 - never passes

001 - passes if src < dest

010 - passes if src = dest

011 - passes if src <= dest

100 - passes if src > dest

101 - passes if src <> dest

110 - passes if src >= dest

111 - always passes

# REPSTIP Register

This register contains the repeat count for the bits in the STIP register other than the LSB bit. When stipple checking is enabled with the ENABSTIP register the STIPCOUNT register determines how many pixel writes will be conditioned by the LSB bit in the STIP register before the STIP register is rotated right. The count in the REPSTIP register determines how many pixel writes will be conditioned by the each remaining bit in the STIP register before the STIP register is rotated right. The stipple pattern is used to condition pixel writes for the Draw Line instructions. The format of this register is shown in Figure 6.53.

Figure 6.53 REPSTIP Register

REptr index = 0x30

Unbuffered Input Register

Bits 7-0: Repeat Stipple Count (Write Only). These bits contain the repeat stipple count for all bits in the STIP register except the LSB bit.

# **ENABLWID** Register

This register is used to enable or disable the WID checking for the line drawing instructions. The ENABWID register also must be enabled for the line drawing WID checking to be enabled. When enabled the value in the WID bitplanes at the current X, Y location are compared to the value in the CURWID register. If the values are the same the WID check passes. If the values are different the WID check fails. The format of this register is shown in Figure 6.54.

Figure 6.54 ENABLWID Register

REptr index = 0x31

Unbuffered Input Register

Bit 0 : Enable Line WID Checking (Write Only). This bit is used to enable or disable line WID checking. The ENABWID register must be set to one for this register to take effect.

0 - disable line WID checking1 - enable line WID checking

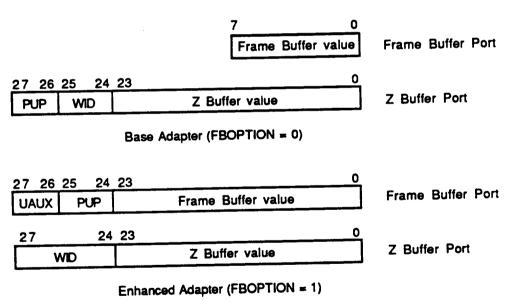

#### **FBOPTION Register**

This register is used to inform the RE2 if the additional Frame Buffer bitplanes card is installed on the adapter. The first data parameter sent down to the microcode after the microcode download is written into the FBOPTION register by the microcode during the adapter initialization. The format of this register is shown in Figure 6.55.

Figure 6.55 FBOPTION Register

REptr index = 0x32

Unbuffered Input Register

Bits 1-0: FO (Write Only). These bits indicate if the additional Frame Buffer bitplanes card is installed on the adapter.

00 - 8 Frame Buffer, 2 PUP and 2 WID bitplanes installed

01 - 24 Frame Buffer, 2 PUP, 2 UAUX and 4 WID bitplanes installed

10 - Undefined

11 - 16 Frame Buffer, 2 PUP, 2 UAUX and 4 WID bitplanes installed (not supported)

# **TOPSCAN Register**

This register is used to specify how many rows and cols are being displayed for the currently selected Display State Machine timing. The row count specifies the top row on the display and thus the first row which will be displayed. Row 0 is always the bottom row displayed on the screen. The col count specifies the number of columns on each scan line. Column 0 is always the left most column displayed on the screen. The col value is the starting col divided by 5. The host software must use the GE\_LOADRE token to load the TOPSCAN register whenever it changes the monitor type in the Display Subsystem. The format of this register is shown in Figure 6.56.

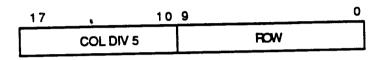

Figure 6.56 TOPSCAN Register

REptr index = 0x33

Unbuffered Input Register

Bits 17-10: col (Write Only). These bits contain the col number of the first pixel to be displayed.

Bits 9-0: row (Write Only). These bits contain the row number of the first pixel to be displayed.

| monitor<br>type | topscan |       |        |

|-----------------|---------|-------|--------|

|                 | ∞l      | tow   |        |

| 60Hz            | 0×00    | 0x3FF | (1023) |

| 30Hz            |         | 0x3FF |        |

| PAL             | 0×00    | 0x23F | (575)  |

| NTSC            | 0×00    | 0x1E4 | (484)  |

#### **ZBOPTION** Register

This register is used to inform the RE2 if the Z Buffer card is installed on the adapter. The second data parameter sent down to the microcode after the microcode download is written into the ZBOPTION register by the microcode during the adapter initialization. The format of this register is shown in Figure 6.57.

Figure 6.57 ZBOPTION Register

REptr index = 0x36

Unbuffered Input Register

Bit 0 : ZO (Write Only). This bit indicates if the Z Buffer card is installed on the adapter.

0 - Z Buffer card not installed

1 - Z Buffer card installed

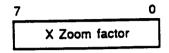

### **XZOOM Register**

This register specifies the x zoom factor which is applied to each pixel written during the execution of the Write Buffer instruction. Each pixel will be written x zoom times along the current scan line. The format of this register is shown in Figure 6.58.

Figure 6.58 XZOOM Register

REptr index = 0x37

Unbuffered Input Register

Bits 7-0: xzoom (Write Only). These bits contain the x zoom factor which is the number of times each pixel is written during the Write Buffer instruction.

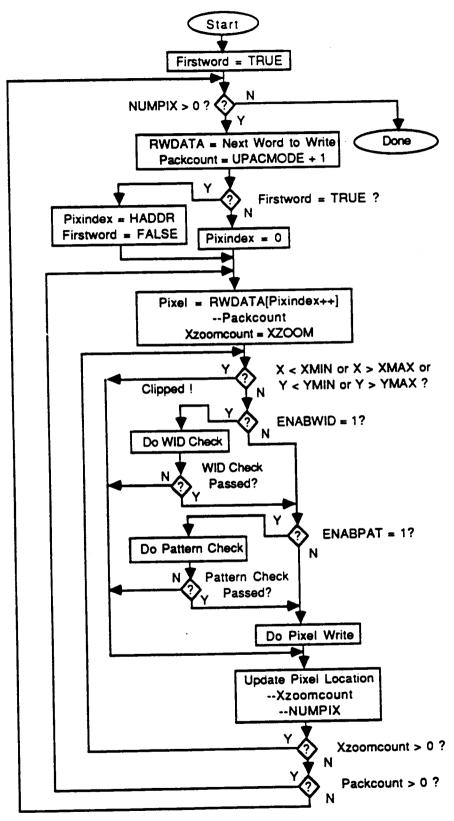

#### **UPACMODE** Register