# Intel Extended Temperature 430TX PCISET: 82439TX System Controller (MTXC) Datasheet

- Supports Mobile and Desktop

- Supports the Pentium<sup>®</sup> Processor www.Data Family Host Bus at 66 MHz and 60 MHz at 3.3V and 2.5V

- PCI 2.1 Compliant

- **Integrated Data Path**

- Integrated DRAM Controller

- 4 Mbytes to 256 MBytes main memory

- 64-Mbit DRAM/SDRAM Technology Support

- FPM (Fast Page Mode), EDO and SDRAM DRAM Support

- 6 RAS Lines Available

- Integrated Programmable Strength for DRAM Interface

- CAS-Before-RAS Refresh, Extended Refresh and Self Refresh for EDO

- **CAS-Before-RAS and Self Refresh** for SDRAM

- Integrated L2 Cache Controller

- 64-MB DRAM Cacheability Direct Mapped Organization—Write

- **Back Only** Supports 256K and 512K Pipelined **Burst SRAM and DRAM Cache**

- SRAM

- Cache Hit Read/Write Cycle Timings at 3-1-1-1

- Back-to-Back Read/Write Cycles at 3-1-1-1-1-1-1

- 64K x 32 SRAM also supported

- Fully Synchronous, Minimum Latency 30/33-MHz PCI Bus Interface

- Five PCI Bus Masters (including PIIX4)

- 10 DWord PCI-to-DRAM Read **Prefetch Buffer**

- 18 DWord PCI-DRAM Post Buffer

- Multi-Transaction Timer to Support **Multiple Short PCI Transactions**

- **Power Management Features**

- PCI CLKRUN# Support

- Dynamic Stop Clock Support

- Suspend to RAM (STR)

- Suspend to Disk (STD)

- Power On Suspend (POS)

- Internal Clock Control

- SDRAM and EDO Self Refresh **During Suspend**

- ACPI Support

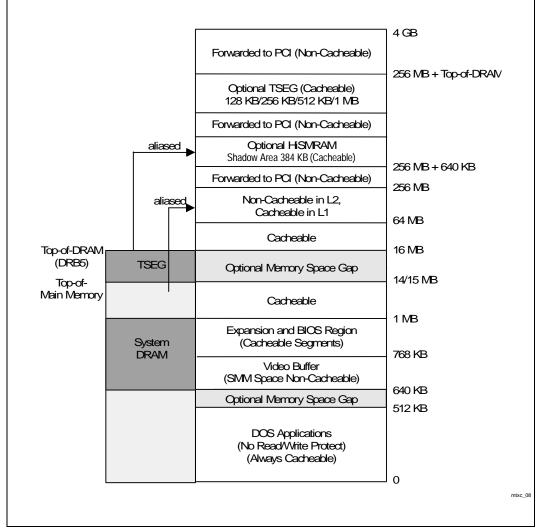

- Compatible SMRAM (C\_SMRAM) and Extended SMRAM (E\_SMRAM) SMM Writeback Cacheable in

- E\_SMRAM Mode up to 1 MB 3.3/5V DRAM, 3.3/5V PCI 3.3/5V Tag

- and 3.3/2.5 SRAM Support

- **Test Features** m

- NAND Tree Support for all Pins

- Supports the Universal Serial Bus (USB)

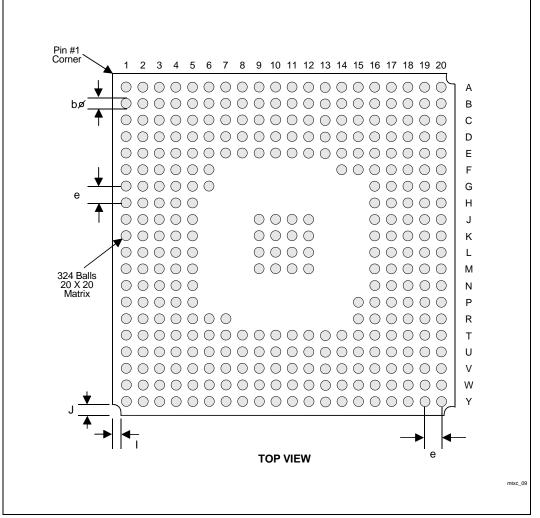

- 324-Pin MBGA 430TX PCIset Xcelerated Controller (MTXC) with integrated Data Paths

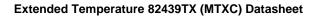

The Intel 430TX PCIset (430TX) consists of the 82439TX System Controller (MTXC) and the 82371AB PCI ISA IDE Xcelerator (PIIX4). The 430TX supports both mobile and desktop architectures. The 430TX forms a Host-to-PCI bridge and provides the second level cache control and a full function 64-bit data path to main memory. The MTXC integrates the cache and main memory DRAM control functions and provides bus e Roya dabad uce, the unagement the lassumes no liability the lassumes no liability the data names are the property to the remeries a state of the state of the the remeries of the line of the state of the the remeries of the line of the state of the state of the the remeries of the line of the state of the state of the the remeries of the state of the state of the state of the the remeries of the state of the state of the state of the state of the the remeries of the state of the s control to transfers between the CPU, cache, main memory, and the PCI Bus. The second level (L2) cache controller supports a writeback cache policy for cache sizes of 256 Kbytes and 512 Kbytes. Cacheless designs are also supported. The cache memory can be implemented with pipelined burst SRAMs or DRAM cache SRAMs. An external Tag RAM is used for the address tag and an internal Tag RAM for the cache line status bits. For the MTXC DRAM controller, six rows are supported for up to 256 Mbytes of main memory. The MTXC is highly integrated by including the Data Path into the same BGA chip. Using the snoop ahead feature, the MTXC allows PCI masters to achieve full PCI bandwidth. For increased system performance, the MTXC integrates posted write and read prefetch buffers. The 430TX integrates many Power Management features that enable the system to save power when the system resources become idle.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by the sale of Intel products. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel retains the right to make changes to specifications and product descriptions at any time, without notice. The Intel #30TX PCIset may contain design defects or errors known as errata. Current characterized errata are available on request. Third-party brands and names are the property of their respective owners.

© INTEL CORPORATION 1999

February 1999

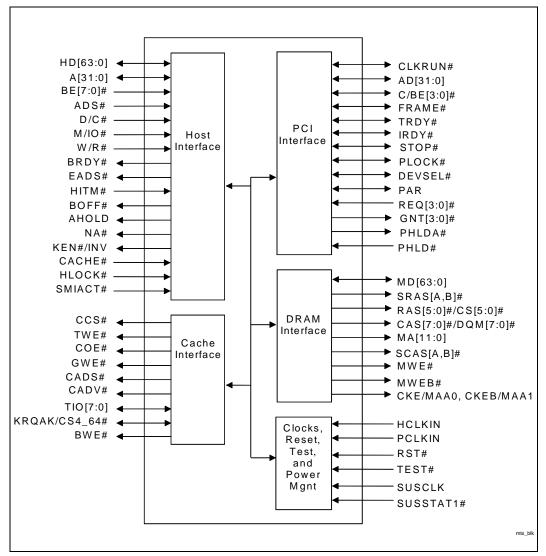

MTXC Simplified Block Diagram

PRELIMINARY

# intപ്പ

# CONTENTS

PAGE

| 1. 0. ARCHITECTURE OVERVIEW                               | 6  |

|-----------------------------------------------------------|----|

| 2. 0. SIGNAL DESCRIPTION                                  | 9  |

| 2.1. MTXC Signals                                         | 9  |

| 2.1.1. HOST INTERFACE                                     | 9  |

| 2.1.2. DRAM Interface                                     | 11 |

| 2.1.3. SECONDARY CACHE INTERFACE                          | 13 |

| 2.1.4. PCI INTERFACE                                      | 14 |

| 2.1.5. TEST AND CLOCK                                     | 15 |

| 2.1.6. POWER MANAGEMENT                                   |    |

| 2.1.7. POWER AND GROUND PINS                              | 15 |

| 2.2. MTXC Strapping Options                               |    |

| 2.3. Power Planes                                         |    |

| 2.4. Power Sequencing Requirements                        |    |

| 2.5. Improving Signal Integrity in Lightly Loaded Systems | 18 |

| 2.6. Signal States During And After A Hard Reset          | 18 |

| 3. 0. REGISTER DESCRIPTION                                |    |

| 3.1. I/O Mapped Registers                                 |    |

| 3.1.1. PM2_CNTRL—PM2 REGISTER BLOCK                       |    |

| 3.1.2. CONFADD—CONFIGURATION ADDRESS REGISTER             |    |

| 3.1.3. CONFDATA—CONFIGURATION DATA REGISTER               |    |

| PCI Configuration Space Mapped Registers                  | 22 |

| 3.1.4. VID—VENDOR IDENTIFICATION REGISTER                 |    |

| 3.1.5. DID—DEVICE IDENTIFICATION REGISTER                 | 25 |

| 3.1.6. PCICMD—PCI COMMAND REGISTER                        | 25 |

| 3.1.7. PCISTS—PCI STATUS REGISTER                         |    |

| 3.1.8. RID—REVISION IDENTIFICATION REGISTER               | 27 |

| 3.1.9. CLASSC—CLASS CODE REGISTER                         | 27 |

| 3.1.10. MLT—MASTER LATENCY TIMER REGISTER                 | 27 |

| 3.1.11. HEDT—HEADER TYPE REGISTER                         |    |

| 3.1.12. BIST—BIST REGISTER                                |    |

| 3.1.13. ACON—ARBITRATION CONTROL REGISTER                 | 28 |

| 3.1.14. PCON—PCI CONTROL REGISTER                         | 29 |

| 3.1.15. CC—CACHE CONTROL REGISTER                         |    |

| 3.1.16. CEC—EXTENDED CACHE CONTROL REGISTER               |    |

| 3.1.17. SDRAMC—SDRAM CONTROL REGISTER                     |    |

| 3.1.18. DRAMEC-DRAM EXTENDED CONTROL REGISTER             |    |

| 3.1.19. DRAMC—DRAM CONTROL REGISTER                       |    |

| 3.1.20. DRAMT—DRAM TIMING REGISTER                        |    |

# intط

## Extended Temperature 82439TX (MTXC) Datasheet

| 3.1.21. PAM—PROGRAMMABLE ATTRIBUTE MAP REGISTERS (PAM[6:0])                | 37 |

|----------------------------------------------------------------------------|----|

| DOS Application Area (00000h–9FFFh)                                        | 39 |

| Video Buffer Area (A0000h–BFFFFh)                                          | 39 |

| Expansion Area (C0000h–DFFFFh)                                             |    |

| Extended System BIOS Area (E0000h–EFFFFh)                                  |    |

| System BIOS Area (F0000h-FFFFFh)                                           |    |

| Extended Memory Area (100000h–FFFFFFh)                                     |    |

| 3.1.22. DRB—DRAM ROW BOUNDARY REGISTERS                                    |    |

| 3.1.23. DRTH—DRAM ROW TYPE REGISTER HIGH                                   | 42 |

| 3.1.24. DRTL—DRAM ROW TYPE REGISTER LOW                                    |    |

| 3.1.25. MTT-MULTI-TRANSACTION TIMER REGISTER (RESERVED TEST MODE REGISTER) |    |

| 3.1.26. ESMRAMC—EXTENDED SYSTEM MANAGEMENT RAM CONTROL REGISTER            | 44 |

| 3.1.27. SMRAMC—SYSTEM MANAGEMENT RAM CONTROL REGISTER                      |    |

| 3.1.28. MCTL—MISCELLANEOUS CONTROL REGISTER                                | 47 |

| 4.0. FUNCTIONAL DESCRIPTION                                                | 48 |

| 4.1. Host Interface                                                        |    |

| 4.2. Secondary Cache Interface                                             |    |

| 4.2.1. CLOCK LATENCIES                                                     |    |

| 4.2.2. SNOOP CYCLES                                                        | 51 |

| 4.2.3. DRAM CACHE SECOND LEVEL CACHE MODE                                  |    |

| 4.3. DRAM Interface                                                        |    |

| 4.3.1. DRAM ORGANIZATION                                                   | 53 |

| 4.3.2. CONFIGURATION REQUIREMENTS                                          | 55 |

| 4.3.3. DRAM ADDRESS TRANSLATION                                            | 59 |

| 4.3.4. DRAM PAGING                                                         | 59 |

| 4.3.5. DRAM TYPES                                                          | 59 |

| 4.3.5.1. FPM Mode                                                          | 59 |

| 4.3.5.2. EDO Mode                                                          | 59 |

| 4.3.5.3. SDRAM Mode                                                        | 59 |

| 4.3.6. AUTO DETECTION                                                      | 61 |

| 4.3.7. DRAM PERFORMANCE                                                    | 61 |

| 4.3.8. DRAM REFRESH                                                        | 64 |

| 4.4. PCI CLK Control (CLKRUN#)                                             | 64 |

| 4.4.1. CLOCKING STATES                                                     | 64 |

| 4.4.2. OPERATION                                                           | 64 |

| 4.5. SMRAM Memory Space                                                    | 64 |

| 4.5.1. COMPATIBLE SMRAM (C_SMRAM)                                          | 64 |

| 4.5.2. EXTENDED SMRAM (E_SMRAM)                                            | 64 |

| 4.5.3. SMRAM PROGRAMMING CONSIDERATIONS                                    |    |

| 4.6. Low Power States                                                      | 66 |

| 4.6.1. CHIP STANDBY                                                        | -  |

| 4.6.2. SUSPEND/RESUME                                                      | 67 |

# PRELIMINARY

# intപ്പ

## Extended Temperature 82439TX (MTXC) Datasheet

| 4.6.2.1. Power Transition Changes                | 68  |

|--------------------------------------------------|-----|

| 4.7. PCI Interface                               | 69  |

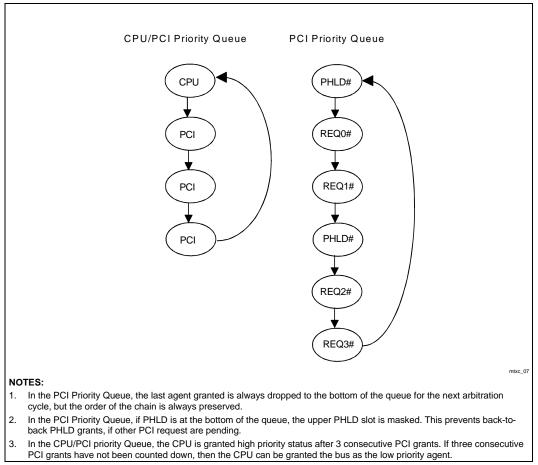

| 4.8. System Arbitration                          | 70  |

| 4.8.1. Priority Scheme and Bus Grant             | 70  |

| 4.8.2. CPU Policies                              | 72  |

| 5. 0. CLOCKS AND RESET                           | 72  |

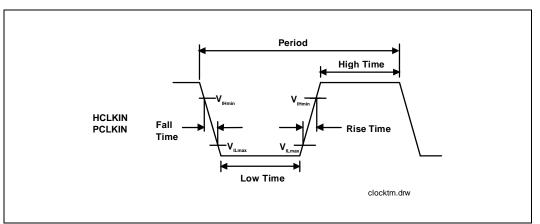

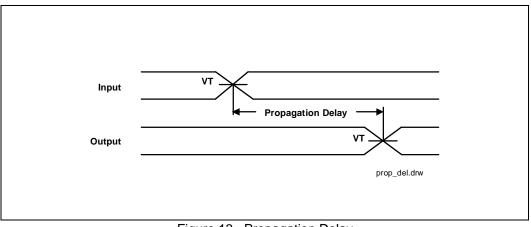

| 5.1. Clock Generation and distribution           | 72  |

| 5.2. RESET Sequencing                            | 72  |

| 6. 0. ELECTRICAL TIMING SPECIFICATIONS           | 72  |

| 6.1. Absolute Maximum Ratings                    | 72  |

| 6.2. Thermal Characteristics                     | 73  |

| 6.3. MTXC DC Characteristics                     | 74  |

| 6.4. MTXC AC Characteristics                     | 79  |

| 7. 0. MTXC Timing Diagrams                       | 85  |

| 8. 0. PINOUT INFORMATION                         | 89  |

| 9. 0. MTXC PACKAGE INFORMATION                   | 94  |

| 10. 0. TESTABILITY                               | 97  |

| 10.1. NAND Tree Mode                             | 97  |

| 10.2. NAND Chain Mode                            | 97  |

| 11. 0. ERRATA                                    | 102 |

| 11.1. SDRAM Speculative Read Enable (SSRE)       | 102 |

| 11.2. Fast Back-to-Back, PCI Peer-to-Peer Cycles |     |

#### 1.0. ARCHITECTURE OVERVIEW

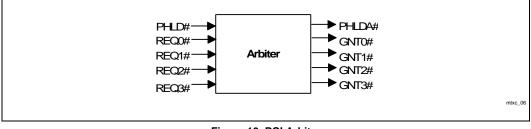

The MTXC host bridge provides a completely integrated solution for the system controller and datapath components in a Pentium processor system. The MTXC Supports all Pentium family processors since P54C, it has 64-bit Host and DRAM Bus Interface, 32-bit PCI Bus Interface, Second level Cache Interface, and it integrates the PCI arbiter.

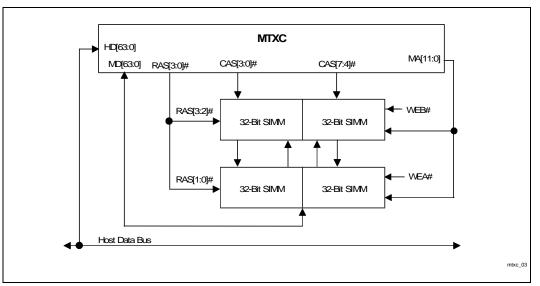

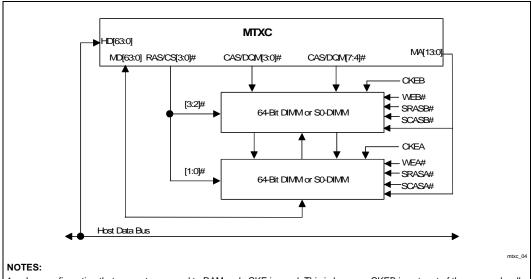

The MTXC interfaces with the Pentium processor host bus, a dedicated memory data bus, and the PCI bus (see Figure 1).

The MTXC bus interfaces are designed to interface with 2.5V, 3.3V and 5V busses. The MTXC implements 2.5V and 3.3V drivers and 5V tolerant receivers. The MTXC connects directly to the Pentium processor 3.3V or 2.5V host bus, directly to 5V or 3.3V DRAMs, and directly to the 5V or 3.3V PCI bus. The 430TX also interfaces directly to the 3.3V or 5.0V TAGRAM and 3.3V Cache.

The MTXC works with the PCI IDE/ISA Accelerator 4 (PIIX4). The PIIX4 provides the PCI-to-ISA/EIO bridge functions along with other features such as a fast IDE interface (PIO mode 4 and Ultra DMA/33), Plug-n-Play port, APIC interface, PCI 2.1 Compliance, SMBUS interface, and Universal Serial Bus Host Controller functions.

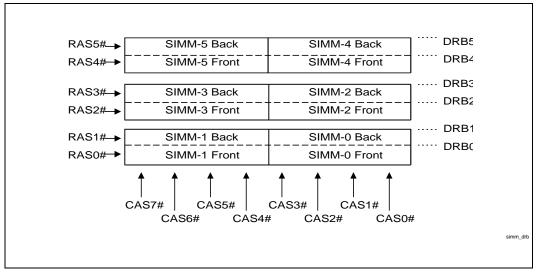

#### DRAM Interface

The DRAM interface is a 64-bit data path that supports Standard (or Fast) Page Mode (FPM), Extended Data Out (EDO) and Synchronous DRAM (SDRAM) memory. The DRAM controller inside the MTXC is capable of generating 3-1-1-1 for posted writes for any type of DRAM that is used. While read performance is 6-1-1-1 for SDRAM, 5-2-2-2 for EDO, and 6-3-3-3 for FPM.

The DRAM interface supports 4 Mbytes to 256 Mbytes with six RAS lines. The MTXC supports 4-Mbit, 16-Mbit, and 64-Mbit DRAM and SDRAM technology, both symmetrical and asymmetrical. Parity is not supported, and for loading reasons, x32 and x64 SIMMs/DIMMs/SO-DIMMs should be used.

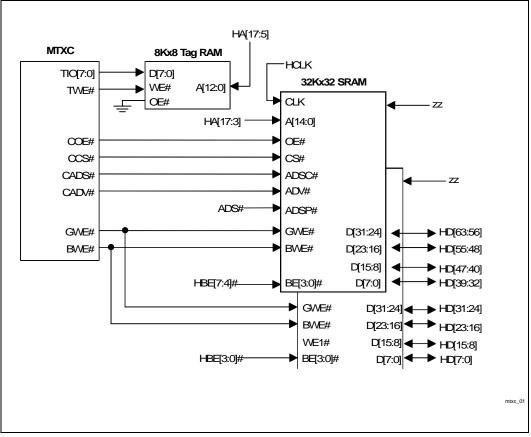

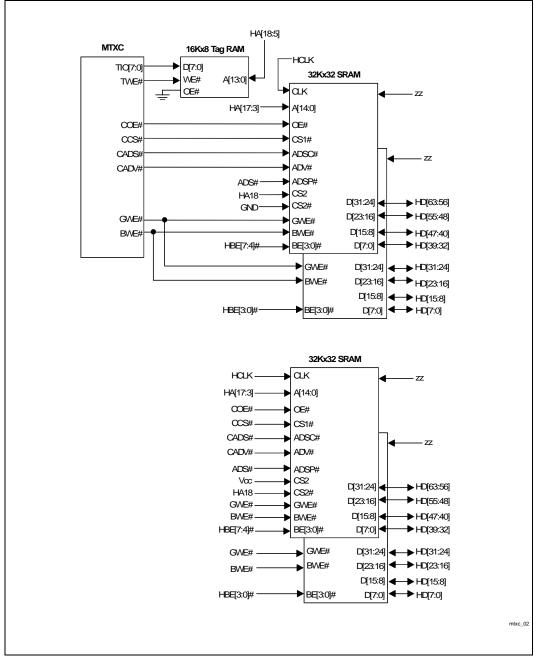

#### Second Level Cache

The second level cache is direct mapped and supports both 256-Kbyte and 512-Kbyte SRAM configuration using Pipeline Burst SRAM or DRAM Cache SRAM. The Cache performance is 3-1-1-1 for line read/write and 3-1-1-1-1-1-1 for back to back reads that are pipelined. Cacheless configuration is also supported.

#### **PCI Interface**

The PCI interface is 2.1 compliant and supports up to four PCI bus masters in addition to the PIIX4 bus master requests.

#### **Datapath and Buffers**

The MTXC contains three sets of data buffers for optimizing data flow. A five QWord deep DRAM write buffer is provided for CPU-to-DRAM writes, second level cache write backs, and PCI-to-DRAM transfers. This buffer is used to achieve 3-1-1-1 posted writes to DRAM and also provides DWord merging and burst merging for CPU-to-DRAM write cycles. In addition, an extra line of buffering is provided that is combined with the DRAM Write Buffer to supply an 18 DWord deep buffer for PCI to main memory writes. A five DWord buffer is provided for CPU-to-PCI writes to help maximize the bandwidth for graphic writes to the PCI bus. Also, five QWords of prefetch buffering has been added to the PCI-to-DRAM read path that allows up to two lines of data to be prefetched at an x-2-2-2 rate. The MTXC interfaces directly to the Host and DRAM data bus.

PRELIMINARY

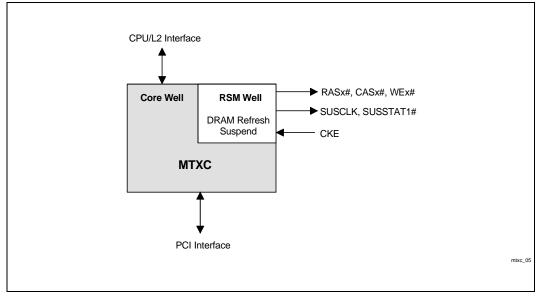

#### **Power Management Features**

The MTXC implements extensive power management features. The CLKRUN# feature enables controlling of the PCI clock (on/off). The MTXC supports POS, STR, STD, and Soft-off suspend states. SUSCLK and SUSSTAT1# signals are used for implementing Suspend Logic. The MTXC supports two SMRAM modes; Compatible SMRAM (C\_SMRAM) and Extended SMRAM (E\_SMRAM). The C\_SMRAM is the traditional SMRAM feature implemented in Intel PCIsets. The E\_SMRAM is a new feature that supports writeback cacheable SMRAM space up to 1 Mbytes. In order to minimize the idle power, the internal clock in MTXC is turned off (gated off) when there is no activity on the Host and PCI Bus.

Figure 1. MTXC System Block Diagram

PRELIMINARY

# intəl

#### 2.0. SIGNAL DESCRIPTION

This section provides a detailed description of each signal. The signals are arranged in functional groups according to their associated interface.

The "#" symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level. When "#" is not present after the signal name, the signal is asserted when at the high voltage level.

The terms assertion and negation are used exclusively. This is done to avoid confusion when working with a mixture of "active low" and "active high" signal. The term assert, or assertion indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term negate, or negation indicates that a signal is inactive.

The I/O buffer types are shown below:

| Buffer Type | Description                                                                                                |

|-------------|------------------------------------------------------------------------------------------------------------|

| I           | input only signal                                                                                          |

| 0           | totem pole output                                                                                          |

| I/O         | bi-direction, tri-state input/output pin                                                                   |

| s/t/s       | sustained tri-state                                                                                        |

| od          | open drain                                                                                                 |

| 3.3V/2.5V   | Indicates the buffer is 3.3V or 2.5V only, depending on the voltage (3.3V or 2.5V) connected to VccX pins. |

| 3.3V/5V     | Indicates that the output is 3.3V and input is 3.3V receiver with 5V tolerance.                            |

| 5V          | Indicates 3.3V receiver with 5V tolerance.                                                                 |

#### 2.1. MTXC Signals

#### 2.1.1. HOST INTERFACE

| Name     | Туре             | Description                                                                                                                                                                                                                   |

|----------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[31:3]  | I/O<br>3.3V/2.5V | Address Bus. A[31:3] connects to the address bus of the CPU. During CPU cycles A[31:3] are inputs. The MTXC drives A[31:3] during inquire cycles on behalf of PCI initiators. Bits A[31:26] act as inputs when RST# is active |

| BE[7:0]# | l<br>3.3V/2.5V   | <b>Byte Enables.</b> The CPU byte enables indicate which byte lane the current CPU cycle is accessing. All eight byte lanes must be provided to the CPU if the cycle is a cacheable read regardless of the state of BE[7:0]#. |

| ADS#     | l<br>3.3V/2.5V   | Address Status. CPU asserts ADS# in T1 of the CPU bus cycle.                                                                                                                                                                  |

| BRDY#    | O<br>3.3V/2.5V   | <b>Bus Ready.</b> The MTXC asserts BRDY# to indicate to the CPU that data is available on reads or has been received on writes.                                                                                               |

| NA#      | O<br>3.3V/2.5V   | <b>Next Address.</b> This signal is asserted by the MTXC to indicate to the Processor that it is ready to process a second cycle.                                                                                             |

| Name                 | Туре             | Description                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AHOLD                | O<br>3.3V/2.5V   | Address Hold. The MTXC asserts AHOLD when a PCI initiator is performing<br>a cycle to DRAM. AHOLD is held for the duration of the PCI burst transfer.<br>The MTXC will negate AHOLD when the completion of the PCI to DRAM read<br>or write cycles complete and during PCI peer transfers. AHOLD is kept<br>asserted while PHLDA# is asserted (i.e., duration of PIIX4 granting). |

| EADS#                | O<br>3.3V/2.5V   | <b>External Address Strobe.</b> Asserted by the MTXC to inquire the first level cache when servicing PCI master references of DRAM.                                                                                                                                                                                                                                               |

| BOFF#                | O<br>3.3V/2.5V   | <b>Back Off.</b> Asserted by the MTXC when required to terminate a CPU cycle that was in progress.                                                                                                                                                                                                                                                                                |

| HITM#                | l<br>3.3V/2.5V   | <b>Hit Modified.</b> Asserted by the CPU to indicate that the address presented with the last assertion of EADS# is modified in the first level cache and needs to be written back.                                                                                                                                                                                               |

| M/IO#, D/C#,<br>W/R# | l<br>3.3V/2.5V   | <b>Memory/IO; Data/Control; Write/Read.</b> Asserted by the CPU with ADS# to indicate the type of cycle that the system needs to perform.                                                                                                                                                                                                                                         |

| HLOCK#               | l<br>3.3V/2.5V   | <b>Host Lock.</b> All CPU cycles sampled with the assertion of HLOCK# and ADS#, until the negation of HLOCK# must be atomic, i.e. no PCI activity to DRAM is allowed.                                                                                                                                                                                                             |

| CACHE#               | l<br>3.3V/2.5V   | <b>Cache.</b> Asserted by the CPU during a read cycle to indicate the CPU will perform a burst line fill. Asserted by the CPU during a write cycle to indicate the CPU will perform a burst writeback cycle. If CACHE# is asserted to indicate cacheability, the MTXC will assert KEN# either with the first BRDY#, or with NA# if NA# is asserted before the first BRDY#.        |

| KEN#/INV             | O<br>3.3V/2.5V   | <b>Ken/Invalidate.</b> KEN#/INV functions as both the KEN# signal during CPU read cycles, and the INV signal during L1 snoop cycles. During CPU cycles, KEN#/INV is normally low. KEN#/INV is driven high during the 1st BRDY# or NA# assertion of a non-L1-cacheable CPU read cycle.                                                                                             |

|                      |                  | KEN#/INV is driven high(low) during the EADS# assertion of a PCI master DRAM write(read) snoop cycle. Note that KEN#/INV operation during snoop cycles is independent of the FLCE bit programming.                                                                                                                                                                                |

| SMIACT#              | l<br>3.3V/2.5V   | System Management Interrupt Active. This is asserted by the CPU when it is in system management mode as a result of an SMI. This signal must be sampled active with ADS# for the processor to access the SMM space of DRAM, located at A0000h, after SMM space has been loaded and locked by BIOS at system boot.                                                                 |

| HD[63:0]             | I/O<br>3.3V/2.5V | <b>Host Data.</b> These signals are connected to the CPU data bus. These signals have internal pull-down resistors.                                                                                                                                                                                                                                                               |

#### NOTES:

All of the signals in the host interface are described in the Pentium Processor data sheet. The preceding table highlights MTXC specific uses of these signals.

PRELIMINARY

#### 2.1.2. DRAM INTERFACE

| Name                                       | Туре       | Description                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAS[3:0]#<br>or<br>CS[3:0]#,               | O<br>3.3 V | Row Address Strobe—RASx# (EDO/FPM). These pins select the DRAM row.<br>Chip Select—CSx# (SDRAM). These pins activate the SDRAMs. SDRAM                                                                                                                                                                                                                                                                             |

| RAS4#/CS4#/<br>BA1,<br>RAS5#/CS5#/<br>MA13 |            | accepts any command when its CS# pin is active low.<br>Note: For 64Mbit SDRAM support, BA1/MA12 and MA13 are muxed with the<br>RAS4# and RAS5# signals, respectively. When SDRAMC[bit 1]=1, BA1 and<br>MA13 are driven out on these lines.                                                                                                                                                                         |

| CAS[7:0]# or<br>DQM[7:0]                   | O<br>3.3 V | Column Address Strobe (EDO/FPM). These pins select the DRAM column.<br>Input/Output Data Mask SDRAM). These pins act as synchronized output<br>enables during a read cycle and a byte mask during a write cycle. The read<br>cycles require Tdqz clock latency before the functions are actually performed. In<br>case of a write cycle, word mask functions are performed in the same cycle (0<br>cycle latency). |

| MA[11:0]                                   | O<br>3.3 V | <b>Memory Address (EDO/FPM/SDRAM).</b> This is the row and column address for DRAM. These buffers now include programmable size selection, as controlled by the DRAMEC[MAD] bit. For 64-Mbit SDRAM support BA1/MA12 and MA13 are muxed with the RAS4# and RAS5# signals, respectively.                                                                                                                             |

| MWEB#                                      | O<br>3.3 V | <b>Memory Write Enable (second copy) (EDO/FPM/SDRAM).</b> MWE# should be used as the write enable for the memory data bus. This signal has programmable buffer size selection.                                                                                                                                                                                                                                     |

| MWE#                                       | O<br>3.3 V | <b>Memory Write Enable (EDO/FPM/SDRAM).</b> MWE# should be used as the write enable for the memory data bus. This signal has programmable buffer size selection.                                                                                                                                                                                                                                                   |

| SRAS[A,B]#                                 | O<br>3.3 V | <b>SDRAM Row Address Strobe (SDRAM).</b> When asserted, this signal latches Row Address on the positive edge of the clock. This signal also allows Row access and precharge. Two copies are provided for loading purpose. These signals have programmable buffer size selection.                                                                                                                                   |

| SCAS[A,B]#                                 | O<br>3.3 V | <b>SDRAM Column Address Strobe (SDRAM).</b> When asserted, this signal latches Column Address on the positive edge of the clock. This signal also allows Column access. Two copies provided for loading purpose. These signals have programmable buffer size selection.                                                                                                                                            |

| CKE/MAA0                                   | O<br>3.3 V | <b>SDRAM Clock Enable (SDRAM).</b> SDRAM clock enable pin. When this signal is negated, SDRAM enters power down mode. This signal is also muxed to provide a second copy of memory address MA0 (MAA0). The MA function is selected via DRT[bit2] (offset 67h).                                                                                                                                                     |

|                                            |            | MTXC negates CKE (and CKEB) when SUSSTAT1# is asserted. Note that MTXC asserts CKE (and CKEB) for all rows (i.e., CKE and CKEB cannot be selectively asserted for certain rows and negated for other rows).                                                                                                                                                                                                        |

## Extended Temperature 82439TX (MTXC) Datasheet

| Name      | Туре           | Description                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CKEB/MAA1 | 0<br>3.3 V     | <b>SDRAM Clock Enable (SDRAM) (second copy).</b> SDRAM clock enable pin.<br>When this signal is negated, SDRAM enters into power down mode. Note that<br>this signal is not implemented in the "Suspend Well" and should not be used if<br>suspend to RAM (STR) is implemented. This signal is also muxed to provide a<br>second copy of memory address MA1 (MAA1). The MA function is selected via<br>DRT[bit2] (offset 67h). |

|           |                | MTXC negates CKE (and CKEB) when SUSSTAT1# is asserted. Note that MTXC asserts CKE (and CKEB) for all rows (i.e., CKE and CKEB cannot be selectively asserted for certain rows and negated for other rows).                                                                                                                                                                                                                    |

| MD[63:0]  | I/O<br>3.3V/5V | <b>Memory Data.</b> These signals are connected to the DRAM data bus. These signals have internal pull-down resistors                                                                                                                                                                                                                                                                                                          |

# PRELIMINARY

#### 2.1.3. SECONDARY CACHE INTERFACE

| Name              | Туре           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CADV#             | O<br>3.3V      | <b>Cache Advance.</b> Assertion causes the PBSRAM in the secondary cache to advance to the next QWord in the cache line.                                                                                                                                                                                                                                                                                                                   |

| CADS#             | O<br>3.3V      | <b>Cache Address Strobe.</b> Assertion causes the PBSRAM in the secondary cache to load the PBSRAM address register from the PBSRAM address pins.                                                                                                                                                                                                                                                                                          |

| CCS#              | O<br>3.3V      | <b>Cache Chip Select (CCS#).</b> The second level cache will power up, if necessary, and perform an access if this signal is asserted when CADS# is asserted. The second level cache will power down if this signal is negated when CADS# is asserted. When CCS# is negated the second level cache will ignore ADS#. If CCS# is asserted when ADS# is asserted, the second level cache will power up, if necessary, and perform an access. |

| COE#              | O<br>3.3V      | <b>Cache Output Enable.</b> The secondary cache data RAMs drive the CPUs data bus when COE# is asserted.                                                                                                                                                                                                                                                                                                                                   |

| GWE#              | O<br>3.3V      | <b>Global Write Enable.</b> GWE# assertion causes all the byte lanes to be written into the secondary cache data RAMs, if they are powered up.                                                                                                                                                                                                                                                                                             |

| BWE#              | O<br>3.3V      | Byte Write Enable. Asserted low with GWE#=HIGH to enable using host's BE[7:0]# to be used to control byte lanes to pipeline burst SRAM cache.                                                                                                                                                                                                                                                                                              |

| TIO[7:0]          | I/O<br>3.3V/5V | <b>Tag Address.</b> These are inputs during CPU accesses and outputs during second level cache line fills and second level cache line invalidates due to inquire cycles. These signals have internal pull-down resistors.                                                                                                                                                                                                                  |

| TWE#              | O<br>3.3V      | Tag Write Enable. When asserted, new state and tag addresses are written into the external tag.                                                                                                                                                                                                                                                                                                                                            |

| KRQAK/<br>CS4_64# | I/O<br>3.3V    | <b>KRQAK/Chip Select 4 (for 64-Mb Technology).</b> This pin is a dual-function signal. KRQAK is used in a DRAM Cache L2 implementation and is a bi-directional refresh request/acknowledge. The CS4_64# function is used to generate the fifth chip select line in a SDRAM L2 Cache implementation that supports five rows of 64-Mbit SDRAM.                                                                                               |

|                   |                | During a hard reset, this signal is sampled to determine if DRAM cache is in the system (see MTXC Strapping options). This signal has a weak internal pull-down.                                                                                                                                                                                                                                                                           |

|                   |                | If SDRAMC[bit 1]=1 and DRAM cache is not present in the system (indicated by CEC[bit 5]=0, offset 53h), the CS4_64# function is selected. If DRAM cache is in the system or SDRAMC[bit 1] (offset 54h)=0, then KRQAK is used to drive the KRQAK function.                                                                                                                                                                                  |

#### 2.1.4. PCI INTERFACE

| Name       | Туре          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD[31:0]   | I/O<br>3.3/5V | Address/Data. The standard PCI address and data lines. Address is driven with FRAME# assertion, data is driven or received in following clocks.                                                                                                                                                                                                                                                                                                                                             |

| C/BE[3:0]# | I/O<br>3.3/5V | <b>Command/Byte Enable.</b> The command is driven with FRAME# assertion, byte enables corresponding to supplied or requested data is driven on following clocks.                                                                                                                                                                                                                                                                                                                            |

| FRAME#     | I/O<br>3.3/5V | <b>Frame.</b> Assertion indicates the address phase of a PCI transfer. Negation indicates that one more data transfer is desired by the cycle initiator.                                                                                                                                                                                                                                                                                                                                    |

| DEVSEL#    | I/O<br>3.3/5V | <b>Device Select.</b> This signal is driven by the MTXC when a PCI initiator is attempting to access DRAM. DEVSEL# is asserted at medium decode time.                                                                                                                                                                                                                                                                                                                                       |

| IRDY#      | I/O<br>3.3/5V | Initiator Ready. Asserted when the initiator is ready for a data transfer.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TRDY#      | I/O<br>3.3/5V | Target Ready. Asserted when the target is ready for a data transfer.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| STOP#      | I/O<br>3.3/5V | Stop. Asserted by the target to request the master to stop the current transaction.                                                                                                                                                                                                                                                                                                                                                                                                         |

| LOCK#      | I/O<br>3.3/5V | Lock. Used to establish, maintain, and release resource locks on PCI.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| REQ[3:0]#  | l<br>3.3/5V   | PCI Request. PCI master requests for PCI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GNT[3:0]#  | O<br>3.3V     | PCI Grant. Permission is given to the master to use PCI.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PHLD#      | I<br>3.3/5V   | <b>PCI Hold.</b> This signal comes from the expansion bridge. It is the bridge request for PCI. The MTXC will drain the DRAM write buffers, drain the CPU-to-PCI posting buffers, and acquire the host bus before granting via PHLDA#.                                                                                                                                                                                                                                                      |

| PHLDA#     | 0<br>3.3V     | <b>PCI Hold Acknowledge.</b> This signal is driven by the MTXC to grant PCI to the expansion bridge. PHLDA# protocol has been modified to include support for passive release.                                                                                                                                                                                                                                                                                                              |

| PAR        | I/O<br>3.3/5V | <b>Parity.</b> A single parity bit is provided over AD[31:0] and C/BE[3:0]. This signal should be pulled high through a weak external pull-up resistor.                                                                                                                                                                                                                                                                                                                                     |

| CLKRUN#    | I/O<br>3.3/5V | <b>CLOCK RUN.</b> An open drain output and also an input. MTXC requests the central resource (PIIX4) to start, or maintain the PCI clock by the assertion of CLKRUN#. MTXC will tri-state CLKRUN# upon negation of reset (since CLK is running upon negation of reset). External pull-up is required. Note: This signal should be connected to the PIIX4 CLKRUN# pin. However, if it is left as a no connect on the MTXC, it must be pulled low through a 100 $\Omega$ (pull-down resistor. |

| RST#       | l<br>3.3/5V   | <b>Reset.</b> When asserted this signal asynchronously resets the MTXC. The PCI signals also tri-state compliant to PCI Rev 2.0 and 2.1 specifications.                                                                                                                                                                                                                                                                                                                                     |

PRELIMINARY

#### 2.1.5. TEST AND CLOCK

| Name   | Туре              | Description                                                                                                                                                                                                     |

|--------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEST#  | I<br>3.3/5V       | <b>Test In.</b> NAND tree mode is activated by driving this pin low. The test mode selected depends on the state of REQ[3:0]#. This pin should be pulled high with an external pull-up during normal operation. |

| HCLKIN | l<br>3.3/2.5<br>V | <b>Host Clock In.</b> This pin receives a buffered host clock. This clock is used by all of the MTXC logic that is in the Host clock domain.                                                                    |

| PCLKIN | l<br>3.3/5V       | <b>PCI Clock In.</b> This pin receives a buffered divide-by-2 host clock. This clock is used by all of the MTXC logic that is in the PCI clock domain.                                                          |

#### 2.1.6. POWER MANAGEMENT

| Name      | Туре      | Description                                                                                                                                                                                                                                                  |

|-----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SUSCLK    | I<br>3.3V | <b>Suspend Clock.</b> The signal is a 32 KHz input for DRAM refresh circuitry and clocking events in suspend state. The DRAM refresh during suspend and non-suspend states is performed based on this clock. This signal has an internal pull-down resistor. |

| SUSSTAT1# | I<br>3.3∨ | <b>Suspend Status.</b> SUSSTAT1# indicates MTXC's power plane status during suspend mode. SUSSTAT1#, along with SUSCLK and RST#, define the suspend protocol between MTXC and PIIX4. This signal has an internal pull-up resistor.                           |

#### 2.1.7. POWER AND GROUND PINS

| Name      | Туре               | Description                                                                                                                                                                                                                                                                                                                  |  |

|-----------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Vcc       | 3.3V               | <b>Main voltage supply.</b> These pins are the primary voltage supply for the MTXC core and I/O periphery and must be connected to 3.3V.                                                                                                                                                                                     |  |

| Vcc (CPU) | 3.3V<br>or<br>2.5V | <b>Interface Voltage Supply.</b> These pins are the primary voltage supply for the C Host periphery and must be connected to either 2.5V or 3.3V, depending on oltage level of the CPU interface. Refer to the Power sequencing requirements on for additional details.                                                      |  |

| Vcc (SUS) | 3.3V               | <b>Ispend Well Voltage Supply.</b> These pins are the primary voltage supply for the IXC suspend logic and I/O. If suspend to RAM is supported, these pins should be an isolated power plane; otherwise, they can be connected to the same 3.3V urce used for the Vcc pins.                                                  |  |

| Vcc5REF   | 3.3V<br>or 5V      | <b>Voltage Reference.</b> This pin is tied to 5V through a small external power sequencing circuit, if MTXC signals are required to be 5V Tolerant. In a non 5V tolerant system (i.e. 3.3V only system), this signal can be tied directly to Vcc. Refer to the Power sequencing requirements section for additional details. |  |

| Vss       | 0V                 | Ground. These pins are the ground for the MTXC.                                                                                                                                                                                                                                                                              |  |

### 2.2. MTXC Strapping Options

| Name          | Туре     | Description                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCS           | A[31:30] | Secondary Cache Size. Described in the Cache Control Register bits 7:6.                                                                                                                                                                                                                                                                                                                                             |

| L2RAMT        | A[29:28] | Initial L2 RAM Type. Described in the Cache Control Register bits 5:4.                                                                                                                                                                                                                                                                                                                                              |

| DRAM<br>Cache | KRQAK    | <b>DRAM Cache L2 Present Upon Reset Negation.</b> This bit is sampled to detect DRAM L2 cache. If sampled high, a DRAM Cache is present. A weak pulldown is provided internally. A DRAM cache module should implement a pull-up on this pin that overrides the weak pulldown. BIOS does not have to be aware of this, this information is used by the MTXC to maintain optimal Pburst timings.                      |

| 25VD          | A26      | <b>2.5V Voltage Detection.</b> This bit is used to determine the voltage level (3.3V or 2.5V) of the host clock connected to the host clock pin and the voltage on the $Vcc(CPU)$ pins. An external pull-down or pull-up resistor is required on this pin (pulled down for 2.5V and pulled up for 3.3V).                                                                                                            |

| HFD           | A27      | <b>Frequency Detection.</b> BIOS can use this bit to determine if the system is 60 MHz (external pull-up) or 66 MHz (no strapping is present) as described in the DRTH Register, bit 7. DRTH[bit 7] register is initialized with the inverted value of pin A27 upon reset negation. The A27 input buffer includes a weak pulldown resistor which will force DRTH[bit 7] to default to 1 if no strapping is present. |

#### 2.3. Power Planes

The MTXC has three primary internal power planes. These power planes permit parts of the MTXC to power down to conserve battery life. Table 1 shows the internal planes and their uses.

| Table 1. MTXC | Internal Power | Planes |

|---------------|----------------|--------|

|---------------|----------------|--------|

| Power<br>Plane | Description                                                                                                                                                                                                                                                                            | Signals Powered                                                                                                                                              | Vcc Pins  | GND<br>Pins |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------|

| SUSPEND        | Contains the logic needed to resume from the<br>Suspend-to-RAM state. This power supply<br>should be capable of providing a "trickle" current.<br>The input signals attached to the SUSPEND<br>power plane Do Not Support 5V Input Levels.<br>These signals must not exceed Vcc (SUS). | MWE#, MWEB#,<br>CKE, RAS[5:0]# 1,<br>CAS[7:0]#, SUSCLK,<br>SUSSTAT1#                                                                                         | Vcc (SUS) | Vss         |

| CPU            | CPU Interface signals have a separate supply so<br>that the CPU interface can be 3.3V for existing<br>CPUs and can be 2.5V on future CPUs.                                                                                                                                             | A[31:3], BE[7:0]#,<br>ADS#, BRDY#, NA#,<br>AHOLD, EADS#,<br>BOFF#, HITM#,<br>M/IO#, D/C#, W/R#,<br>HLOCK#, CACHE#,<br>KEN#/INV, SMIACT#,<br>HD[63:0], HCLKIN | Vcc (CPU) | Vss         |

| Vcc5REF        | The Vcc5REF signal provides protection for the 5V tolerant 3.3V signals.                                                                                                                                                                                                               | PCI Bus Input and<br>I/O, MD[63:0],<br>TIO[7:0], PCLKIN,<br>TEST#                                                                                            | Vcc5REF   | Vss         |

# PRELIMINARY

| Table | 1. | MTXC | Internal | Power | Planes |

|-------|----|------|----------|-------|--------|

|-------|----|------|----------|-------|--------|

| Power<br>Plane | Description                                                                                     | Signals Powered       | Vcc Pins | GND<br>Pins |

|----------------|-------------------------------------------------------------------------------------------------|-----------------------|----------|-------------|

| MAIN           | Contains all the rest of the MTXC logic. This plane is powered by the main system power supply. | All Other Signal Pins | Vcc      | Vss         |

NOTES:

KRQAK is not part of the suspend well. When this pin is used as the 5<sup>th</sup> RAS line (CS4\_64), special considerations must be taken.

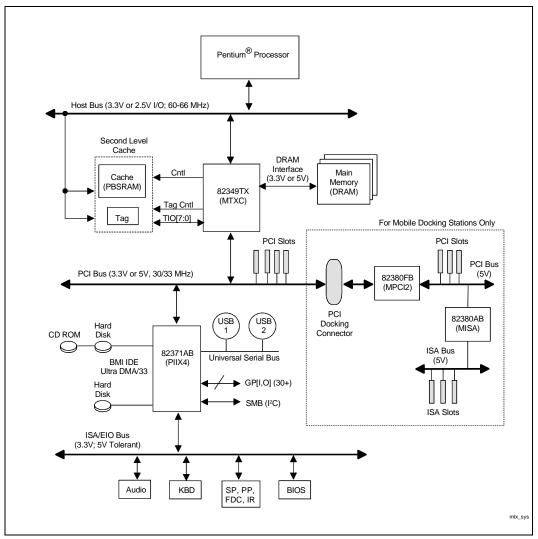

#### 2.4. Power Sequencing Requirements

The Vcc5REF signal must be tied to 5V in a system requiring 5V tolerance. In a 5V tolerant system, Vcc5REF must power up before or simultaneous to Vcc. It must power down after or simultaneous to Vcc. At any time, Vcc5REF should not be more than 0.6 volts below Vcc. In a non-5V tolerant system (3.3V only), this signal can be tied directly to Vcc. In this case, there are no sequencing requirements. Refer to Figure 2 for an example circuit schematic which may be used to ensure the proper Vcc5REF sequencing.

Figure 2. Example Vcc5REF Sequencing Circuit (FIX SYMBOL- See hardcopy)

The Vcc(CPU) power plane is tied to either 2.5 volts or 3.3 volts, depending on the voltage level of the CPU interface. In a system that ties this power plane to 2.5 volts, the Vcc(CPU) pins must power up after or simultaneous to Vcc. It must power down before or simultaneous to Vcc. At any time, Vcc should not be more than 1.2 volts below the Vcc(CPU) plane. VCC(SUS) can power up and power down independent of all other power planes.

#### 2.5. Improving Signal Integrity in Lightly Loaded Systems

To insure that DRAM interface signal integrity is maintained for lightly loaded systems, series termination and/or diodes (Gnd and Vcc diodes) are recommended on the following signals: CAS#/DQMx, MWEx, SCASx, SRASx, CKEx, and all MA lines (note: RAS4# and RAS5# are also used as MA lines, depending on the configuration, and should be terminated when used as MA lines). This will insure that the overshoot, undershoot, and most importantly, ring-back does not cause any problems.

If series termination is used, use 10 ohms. This value provides the best signal integrity and flight time results. Place as close to the driver as possible. If diodes are used, the diodes should have a forward current of at least 200ma at 1 volt. A MMBD1203 diode or equivalent meets this requirement. The diodes should be placed at the end of the trace.

Diodes improve signal integrity without increasing the flight time. A 10 ohm series resistor will increase the flight time by approximately 300ps. Both provide similar signal integrity results.

#### 2.6. Signal States During And After A Hard Reset

Table 2 shows the state of all the MTXC output and bi-directional signals when RST# is asserted. An undefined state means that the signal is driven either high or low, but not tri-stated.

| Name                     | State during<br>RST# | State After<br>RST# |

|--------------------------|----------------------|---------------------|

| A[31:3]                  | Low                  | Tri-State           |

| BRDY#                    | High                 | High                |

| NA#                      | High                 | High                |

| AHOLD                    | High                 | Low                 |

| EADS#                    | High                 | High                |

| BOFF#                    | High                 | High                |

| KEN#/INV                 | Low                  | Low                 |

| HD[63:0]                 | Tri-State            | Tri-State           |

| RAS[5:0]# or<br>CS[5:0]# | Undefined            | High                |

| CAS[7:0]# or<br>DQM[7:0] | Undefined            | Undefined           |

| MA[11:0],<br>BA1,MA13    | Undefined            | Undefined           |

| MWE#,<br>MWEB#           | High                 | High                |

| SRAS[A,B]#               | High                 | High                |

#### Table 2. Signal States During/After Reset

| Table 2. Signal States | s During/After Reset |

|------------------------|----------------------|

|------------------------|----------------------|

| ······································ |                      |                     |  |

|----------------------------------------|----------------------|---------------------|--|

| Name                                   | State during<br>RST# | State After<br>RST# |  |

| SCAS[A,B]#                             | High                 | High                |  |

| CKE,CKEB                               | Undefined            | High                |  |

| MD[63:0]                               | Tri-State            | Tri-State           |  |

| CADV#                                  | High                 | High                |  |

| CADS#                                  | High                 | High                |  |

| CCS#                                   | Low                  | Low                 |  |

| COE#                                   | High                 | High                |  |

| GWE#                                   | High                 | High                |  |

| BWE#                                   | High                 | High                |  |

| TIO[7:0]                               | Low                  | Tri-State           |  |

| TWE#                                   | Low                  | High                |  |

| KRQAK                                  | Input                | Input               |  |

| AD[31:0]                               | Low                  | Tri-State           |  |

| C/BE[3:0]#                             | Low                  | Tri-State           |  |

| FRAME#                                 | Tri-State            | Tri-State           |  |

| DEVSEL#                                | Tri-State            | Tri-State           |  |

PRELIMINARY

# intപ്പ

## Extended Temperature 82439TX (MTXC) Datasheet

#### Table 2. Signal States During/After Reset

| Name  | State during<br>RST# | State After<br>RST# |

|-------|----------------------|---------------------|

| IRDY# | Tri-State            | Tri-State           |

| TRDY# | Tri-State            | Tri-State           |

| STOP# | Tri-State            | Tri-State           |

| LOCK# | Tri-State            | Tri-State           |

#### Table 2. Signal States During/After Reset

| Name      | State during<br>RST# | State After<br>RST# |

|-----------|----------------------|---------------------|

| GNT[3:0]# | Tri-State            | High                |

| PHLDA#    | High                 | High                |

| PAR       | Low                  | Undefined           |

| CLKRUN#   | Tri-State            | Tri-State           |

#### 3.0. REGISTER DESCRIPTION

The MTXC contains two sets of software accessible registers (I/O Mapped and PCI configuration registers), accessed via the Host CPU I/O address space. The I/O mapped registers control access to PCI configuration space. Configuration registers residing in PCI configuration space used to specify PCI configuration, DRAM configuration, cache configuration, operating parameters and optional system features.

The MTXC internal registers (both I/O Mapped and PCI Configuration registers) are only accessible by the Host CPU and cannot be accessed by PCI masters. The registers can be accessed as Byte, Word (16-bit), or DWord (32-bit) quantities, with the exception of CONFADD, which can only be accessed as a DWord. All multi-byte numeric fields use "little-endian" ordering (i.e., lower addresses contain the least significant parts of the field). The following nomenclature is used for access attributes:

- **RO READ ONLY**. If a register is read only, writes to this register have no effect.

- **R/W READ/WRITE**. A register with this attribute can be read and written.

- **R/WC READ/WRITE CLEAR.** A register bit with this attribute can be read and written. However, a write of 1 clears (sets to 0) the corresponding bit and a write of 0 has no effect.

Some of the MTXC registers described in this section contain reserved bits. Software must deal correctly with fields that are reserved. On reads, software must use appropriate masks to extract the defined bits and not rely on reserved bits being any particular value. On writes, software must ensure that the values of reserved bit positions are preserved. That is, the values of reserved bit positions must first be read, merged with the new values for other bit positions and then written back.

In addition to reserved bits within a register, the MTXC contains address locations in the PCI configuration space that are marked "Reserved" (Table 3). The MTXC responds to accesses to these address locations by completing the Host cycle and returning a value of zero. The registers marked as "Undefined" will return a non-zero value and are defined as read only. Software should not write to reserved or undefined MTXC configuration locations in the device-specific region (above address 3Fh).

Upon RESET, the MTXC sets its internal configuration registers to predetermined **default** states. The default state represents the minimum functionality feature set required to successfully bring up the system. Hence, it does not represent the optimal system configuration. It is the responsibility of the system initialization software (usually BIOS) to properly determine the DRAM configurations, cache configuration, operating parameters and optional system features that are applicable, and to program the MTXC registers accordingly.

#### 3.1. I/O Mapped Registers

The MTXC contains three registers that reside in the CPU I/O address space—the Configuration Address (CONFADD) Register, the Configuration Data (CONFDATA) Register, and the PM2 Register Block. The Configuration Address Register enables/disables the configuration space and determines what portion of configuration space is visible through the Configuration Data window.

#### 3.1.1. PM2\_CNTRL—PM2 REGISTER BLOCK

| I/O Address:   | 0022h      |

|----------------|------------|

| Default Value: | 00h        |

| Access:        | Read/Write |

| Bit | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0   | Arbiter Disable (ARB_DIS). When ARB_DIS=1, the MTXC does not respond to any REQ# signals (including PHOLD#) going active until this bit is set back to 0. This bit is used to disable bus master accesses prior to placing the CPU in a stop clock state. This bit maintains cache coherency by preventing PCI masters from gaining access to the PCI bus and causing snoop cycle activity. MCTL[Bit 6] (offset 79h) must be set to 1 before this register is accessible. |

#### 3.1.2. CONFADD—CONFIGURATION ADDRESS REGISTER

| I/O Address:   | 0CF8h (Accessed as a DWord) |

|----------------|-----------------------------|

| Default Value: | 0000000h                    |

| Access:        | Read/Write                  |

CONFADD is a 32-bit register accessed only when referenced as a DWord. A Byte or Word reference will "pass through" the Configuration Address Register onto the PCI bus. The CONFADD register contains the Bus Number, Device Number, Function Number, and Register Number for which a subsequent configuration access is intended.

| Bit   | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | Configuration Enable (CONE). 1=Enable. 0=Disable.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 30:24 | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 23:16 | <b>Bus Number.</b> When the Bus Number is programmed to 00h the target of the Configuration Cycle is either the MTXC or the PCI Local Bus that is directly connected to the MTXC, depending on the Device Number field. A type 0 Configuration Cycle is generated on PCI if the Bus Number is programmed to 00h and the MTXC is not the target. If the Bus Number is non-zero a type 1 configuration cycle is generated on PCI with the Bus Number mapped to AD[23:16] during the address phase.        |

| 15:11 | <b>Device Number.</b> This field selects one agent on the PCI bus selected by the Bus Number. During a Type 1 Configuration cycle this field is mapped to AD[15:11]. During a Type 0 Configuration Cycle this field is decoded and one of AD[31:11] is driven to a 1. The MTXC is always Device Number 0.                                                                                                                                                                                               |

| 10:8  | <b>Function Number.</b> This field is mapped to AD[10:8] during PCI configuration cycles. This allows the configuration registers of a particular function in a multi-function device to be accessed. The MTXC responds to configuration cycles with a function number of 000b; all other function number values attempting access to the MTXC (Device Number=0, Bus Number=0) will generate a type 0 configuration cycle onto the PCI bus with no IDSEL asserted, which will result in a master abort. |

| 7:2   | <b>Register Number.</b> This field selects one register within a particular Bus, Device, and Function as specified by the other fields in the Configuration Address Register. This field is mapped to AD[7:2] during PCI configuration cycles.                                                                                                                                                                                                                                                          |

| 1:0   | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

#### 3.1.3. CONFDATA—CONFIGURATION DATA REGISTER

| I/O Address:   | 0CFCh      |

|----------------|------------|

| Default Value: | 0000000h   |

| Access:        | Read/Write |

CONFDATA is a 32-bit read/write window into configuration space. The portion of configuration space that is referenced by CONFDATA is determined by the contents of CONFADD.

| Bit  | Descriptions                                                                                                                                                                              |

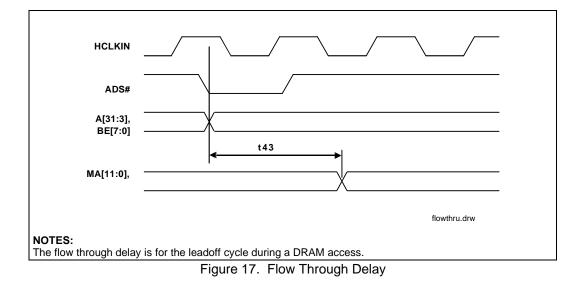

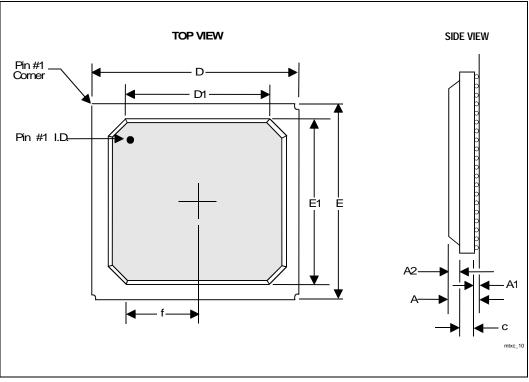

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|