## - IIIILASER XT SERIES PERSONAL COMPUTER

# **Technical Reference Manual**

For LASER Multi-I/O Card

#### TABLE OF CONTENT

#### **CHAPTER 1 INTRODUCTION**

| 1.1 | FEATURES AND AVAILA | BLE |

|-----|---------------------|-----|

|     | OPTIONS             |     |

| 1.2 | SYSTEM USAGE        |     |

#### CHAPTER 2 BOARD LAYOUT, CONNECTORS AND JUMPERS

| 2.1 | BOARD LAYOUT    |  |

|-----|-----------------|--|

| 2.2 | CONNECTORS AND  |  |

|     | JUMPERS         |  |

| 2.3 | JUMPER SETTINGS |  |

#### **CHAPTER 3 HARDWARE DESCRIPTION**

| OVERA  | LL BLOCK                                                                                                               |                                                                                                                         |

|--------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| DIAGRA | λM                                                                                                                     | 3-3                                                                                                                     |

| FLOPPY | DISK INTERFACE                                                                                                         |                                                                                                                         |

| AND TH | RANSCOPY                                                                                                               |                                                                                                                         |

| FUNCT  | ION                                                                                                                    | 3-5                                                                                                                     |

| 3.2.1  | Hardware                                                                                                               | 3-5                                                                                                                     |

| 3.2.2  | Programming                                                                                                            |                                                                                                                         |

|        | Considerations                                                                                                         | 3-8                                                                                                                     |

| 3.2.3  | Connector Pin                                                                                                          |                                                                                                                         |

|        | Assignment                                                                                                             | 3-11                                                                                                                    |

| PARALI |                                                                                                                        |                                                                                                                         |

| 3.3.1  | Hardware                                                                                                               | 3-12                                                                                                                    |

| 3.3.2  | Programming                                                                                                            |                                                                                                                         |

|        | Considerations                                                                                                         | 3-14                                                                                                                    |

| 3.3.3  | Connector Pin                                                                                                          |                                                                                                                         |

|        | Assignment                                                                                                             | 3-16                                                                                                                    |

| RS232C | SERIAL INTERFACE                                                                                                       |                                                                                                                         |

|        |                                                                                                                        | 3-17                                                                                                                    |

| 3.4.1  | Hardware                                                                                                               | 3-18                                                                                                                    |

|        | DIAGRA<br>FLOPPY<br>AND TH<br>FUNCT<br>3.2.1<br>3.2.2<br>3.2.3<br>PARALI<br>3.3.1<br>3.3.2<br>3.3.3<br>RS232C<br>PORTS | 3.2.2       Programming<br>Considerations         3.2.3       Connector Pin<br>Assignment         PARALLEL PRINTER PORT |

|     | 3.4.2  | Programming         |

|-----|--------|---------------------|

|     |        | Considerations 3-20 |

|     | 3.4.3  | Connector Pin       |

|     |        | Assignment 3-21     |

| 3.5 | GAME   | PORT 3-23           |

|     | 3.5.1  | Hardware 3-24       |

|     | 3.5.2  | Programming         |

|     |        | Considerations 3-25 |

|     | 3.5.3  | Connector Pin       |

|     |        | Assignment 3-26     |

| 3.6 | REAL-T | 'IME CLOCK 3-27     |

|     | 3.6.1  | Hardware 3-28       |

|     | 3.6.2  | Programming         |

|     |        | Considerations 3-30 |

#### CHAPTER 4 GATE ARRAY C1

| 4.1 | FUNC   | TIONAL BLOCK         |

|-----|--------|----------------------|

|     | DIAGE  | RAM 4-3              |

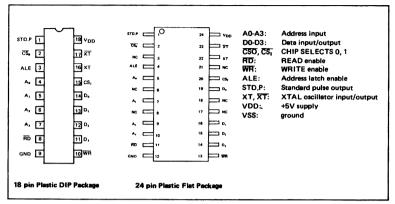

| 4.2 | PIN A  | SSIGNMENT AND        |

|     | SIGNA  | L DESCRIPTION 4-4    |

| 4.3 | ELECT  | TRICAL               |

|     | SPECII | FICATIONS 4-14       |

|     | 4.3.1  | Absolute Maximum     |

|     |        | Ratings 4-14         |

|     | 4.3.2  | Electrical           |

|     |        | Characteristics 4-14 |

| 4.4 | MECH   | IANICAL              |

|     | INFOF  | RMATION 4-15         |

#### **CHAPTER 5 TROUBLE-SHOOTING GUIDE**

| 5.1 | GENERAL FAILURE 5-3     |

|-----|-------------------------|

| 5.2 | FLOPPY DISK INTERFACE / |

|     | TRANSCOPY FAILURE 5-4   |

| 5.3 | PARALLEL PRINTER PORT   |

|     | FAILURE 5-7             |

| 5.4 | RS232C SERIAL INTERFACE |

|     | PORT FAILURE 5-8        |

| 5.5 | GAME PORT FAILURE 5-9   |

| 5.6 | REAL-TIME CLOCK         |

|     | FAILURE 5-10            |

#### APPENDIX

#### A DATA SHEETS

В

| A.1 | FDC    | Z765A           |       |

|-----|--------|-----------------|-------|

|     | (uPD)  | 765 Compatible) | A.1-1 |

| A.2 | ACE    | INS8250         | A.2-1 |

| A.3 | RTC    | MSM6242         | A.3-1 |

| A.4 | RTC    | RP5C15          | A.4-1 |

|     |        |                 |       |

| MU  | LTI-I/ | O SCHEMATICS .  | B-1   |

## **CHAPTER 1**

### **INTRODUCTION**

### 1. INTRODUCTION

The Multi-I/O Card is a multifunction enhancement product for the IBM<sup>®</sup>PC,PC/XT family or compatible computers. This card incorporates Very Large Scale Integration (VLSI) Gate Array technology to reduce PCB area, minimize power consumption and improve reliability.

#### 1.1 FEATURES AND AVAILABLE OPTIONS

The Multi-I/O Card provides standard features including:

#### . Floppy disk interface

Two double-sided, double-density floppy disk drives are supported.

. Parallel printer port

Interfaces with a Centronics type parallel printer.

RS-232C serial interface ports

Up to two RS-232C serial interface ports are provided for interfacing with modem, serial printer, remote display terminal or other serial devices.

Real - Time Clock

With the rechargeable backup battery, the real-time clock allows automatic setting up of time and date every time the computer is turned on.

. Game Port

Connects to game paddle or joystick, for interactive games and graphics software.

#### Diskette Backup (Transcopy) Function

Provides diskette duplication of copy-protected or noncopy-protected software. This function is activated via jumper setting and an optional software package. Check with your dealer for details of this software.

The Multi-I/O Card is available in different versions for various levels of system requirements. Some version comes with only one serial interface port. Sockets and connectors are provided to allow upgrading to two serial ports. Refer to the user's manual for details of upgrading to two serial ports.

Another version of this card contains no floppy disk interface. This version is applicable to PC, PC/XT or compatible main units with built-in Floppy Disk Adapter logic.

Newer version (Enhanced) of this card has on board jumpers which allows disabling of some I/O functions when there is conflict with other devices in the system.

#### 1.2 SYSTEM USAGE

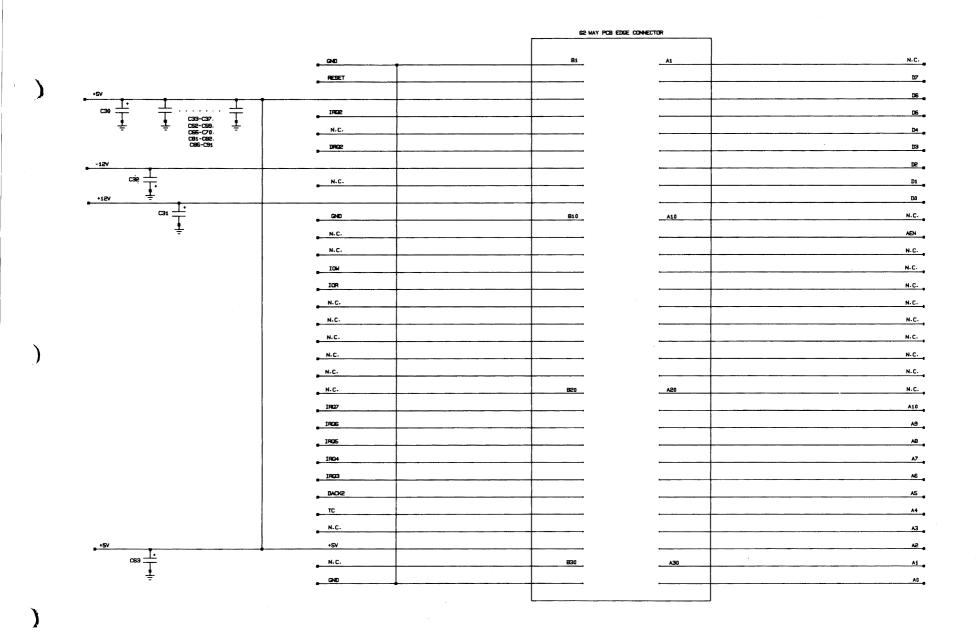

The Multi-I/O Card interfaces with a PC, PC/XT or compatible main unit via a 62 pins PCB edge connector (slot). The following I/O Channel lines are used:

| A0-A10                  | Address lines                    |

|-------------------------|----------------------------------|

| D0-D7                   | Data lines                       |

| IOR, IOW                | I/O Read and I/O Write lines     |

| AEN Address enable line |                                  |

| тс                      | Terminal count for DMA operation |

| RESET DRV System Reset line              |                                             |  |

|------------------------------------------|---------------------------------------------|--|

| DACK 2 DMA acknowledge for DMA channel 2 |                                             |  |

| DRQ 2                                    | DMA request for DMA channel 2               |  |

| IRQ2, IRQ3,<br>IRQ4, IRQ5,<br>IRQ6, IRQ7 | Interrupt request levels<br>2,3,4,5,6 and 7 |  |

| +5V, +12V,<br>-12V                       | +5V, +12V and -12V DC<br>supply voltages    |  |

| Function                        | I/O Address<br>(Hex)              | Interrupt<br>Level | DMA<br>Channel |

|---------------------------------|-----------------------------------|--------------------|----------------|

| Floppy<br>Disk Interface        | 3F2-3F5                           | 6                  | 2              |

| Parallel<br>Printer<br>Port     | 378-37A<br>or<br>3BC-3BE          | 7                  | /              |

| RS232C<br>Serial Port<br>(COM1) | 3F8-3FF                           | 4                  | /              |

| RS232C<br>Serial Port<br>(COM2) | 2F8-2FF                           | 3                  | /              |

| Game Port                       | 201                               | 1                  | /              |

| Real-Time<br>Clock              | 340-35F<br>or<br>2C0-2DF          | 2 or 5             | /              |

| Transcopy<br>Function           | 66F or<br>6EF or<br>76F or<br>7EF | /                  | 2              |

The following table summarizes the I/O Address, Interrupt Levels and DMA Channels used by each of the functions:

# CHAPTER 2 BOARD LAYOUT, CONNECTORS AND JUMPERS

# 2. BOARD LAYOUT, CONNECTORS AND JUMPERS

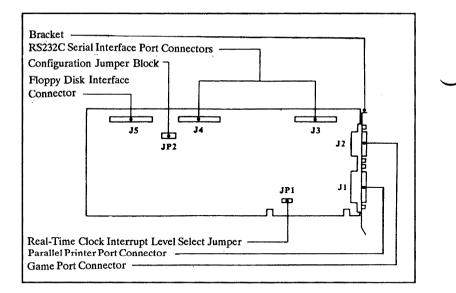

The Multi-I/O Card occupies one 62 pins PCB edge connector (slot) as a typical long card does. However, the two RS232C Serial Interface Ports uses two additional brackets on the back panel of the computer main unit. Therefore, a total of three slots will be required.

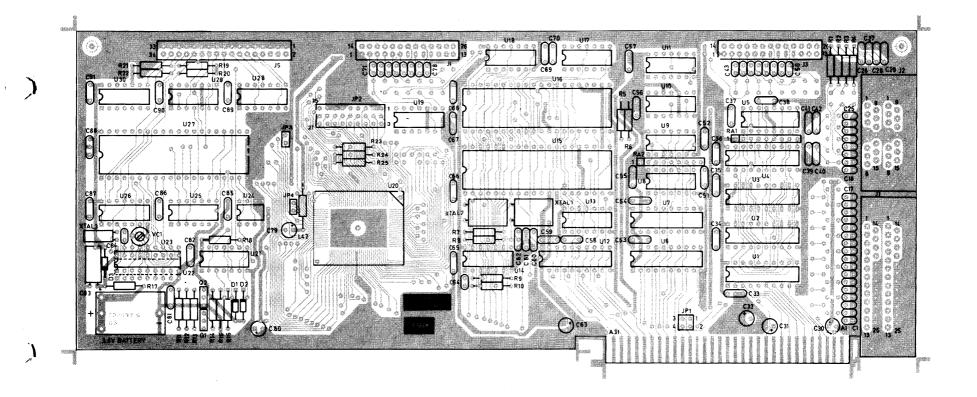

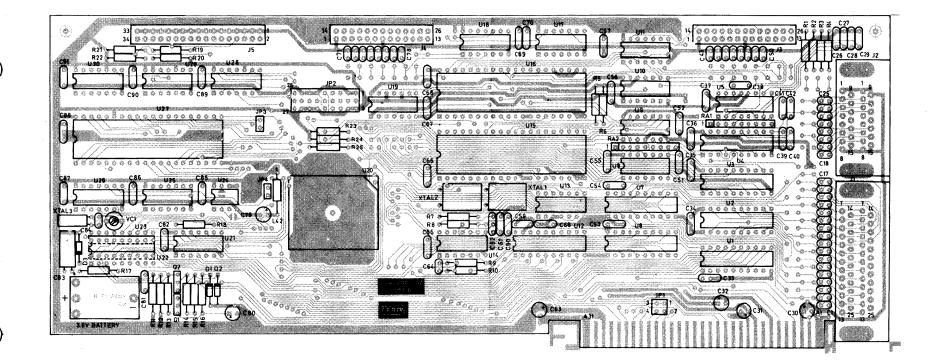

#### 2.1 BOARD LAYOUT

The following figure shows the major elements, in particular, the jumper blocks and connectors on the Multi-I/O Card.

Fig. 2.1 Multi-I/O Board Layout

#### 2.2 CONNECTORS AND JUMPERS

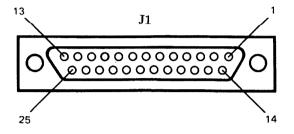

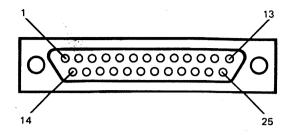

- Connector J1, a 25 pins "D" type female connector, is for connecting to a Centronics standard parallel printer.

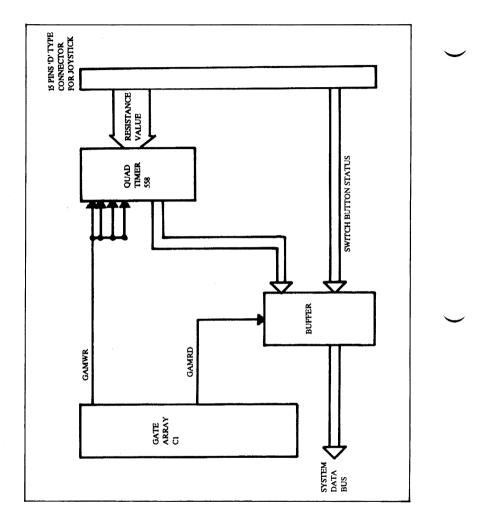

- . Connector J2, a 15 pins "D" type female connector, is for connecting to a joystick or game paddles.

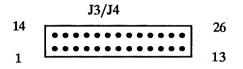

- . Connectors J3 and J4, 26 ways header wafer connectors, are connectors of the two RS232C Serial Interface Ports. J3 is for the Primary Port (COM1) and J4 is for the Secondary Port (COM2). The signals on these connectors are carried to the back of the computers via the cable(s) supplied.

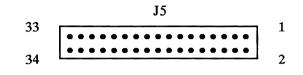

- . Connector J5, a 34 ways header wafer connector, is for connecting to floppy disk drives.

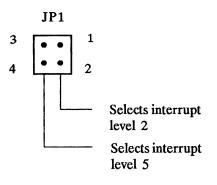

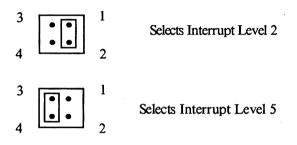

- . JP1, a 4 pins jumper block, is for selecting the two different interrupt request levels for the Real-Time Clock.

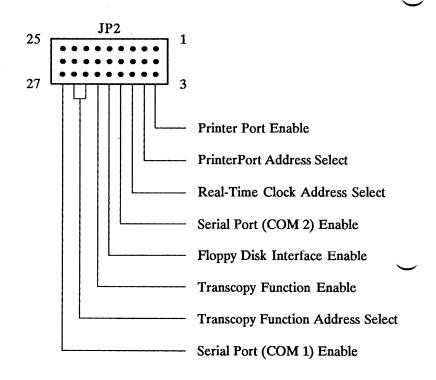

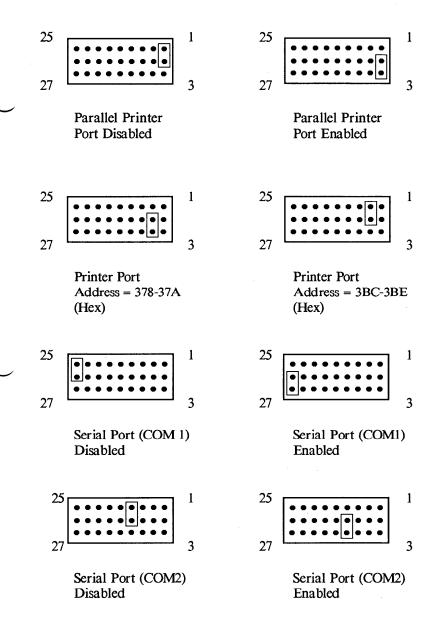

JP2, a 27 pins jumper block on newer versions of the card, is a configuration Jumper Block which allows the user to select different addresses for some of the I/O functions. Moreover, some I/O functions can be disabled in case of address conflict with other devices in the system.

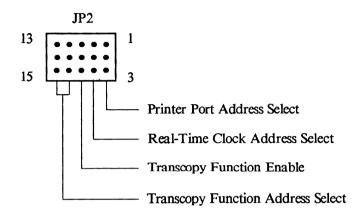

On some earlier version of the Multi-I/O Card, JP2 is a 15 pins jumper block which serves similar purpose as that on the newer version. The Floppy Disk Interface, Parallel Port, RS232C Serial Interface Ports are hardwired to be enabled.

#### 2.3 JUMPER SETTINGS

Various combinations of the jumper block and their meanings are summarized as follows. The jumpers irrelevant to the function under consideration are omitted for clarity.

#### Jumper Block JP1

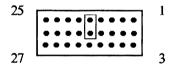

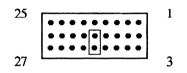

#### Jumper Block JP2 (on newer versions)

Floppy Disk Interface Disabled

Floppy Disk Interface Enabled

Select Real-Time Clock Address=340-35F (Hex)

Transcopy Function Disabled

Transcopy Function Address=7EF (Hex)

Transcopy Function Address=6EF (Hex)

Select Real-Time Clock Address=2C0-2DF (Hex)

Transcopy Function Address=76F (Hex)

Transcopy Function Address=66F (Hex)

$$\begin{array}{c} 13 \\ \bullet \bullet \bullet \bullet \bullet \\ \bullet \bullet \bullet \bullet \bullet \\ 15 \end{array}$$

Printer Port Address=378-37A (Hex)

$$\begin{array}{c|c} 13 \\ \bullet \bullet \bullet \bullet \bullet \\ 15 \end{array}$$

Select Real-Time Clock Address=340-35F (Hex)

Transcopy Function Disabled

Transcopy Function Address=7EF (Hex)

Printer Port Address=3BC-3BE (Hex)

Select Real-Time Clock Address=2C0-2DE (Hex)

Transcopy Function Enabled

Transcopy Function Address=76F (Hex)

Transcopy Function Address=6EF (Hex)

Transcopy Function Address=66F(Hex)

## **CHAPTER 3**

### HARDWARE DESCRIPTION

This chapter describes the hardware structure of the Multi-I/O Card in terms of each function available. For a detail circuit diagram, component layout and component location list, please refer to the Appendix.

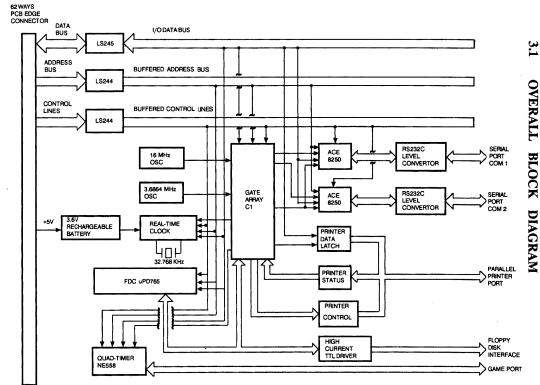

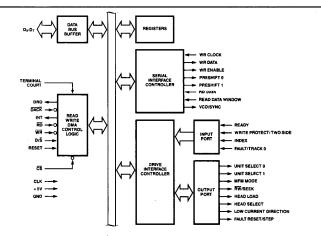

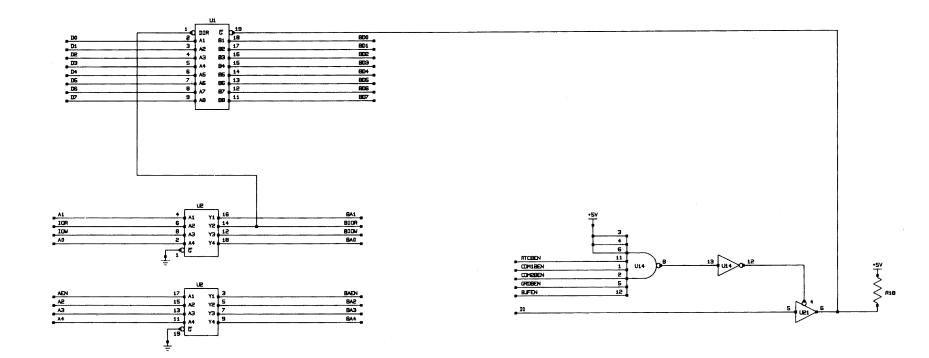

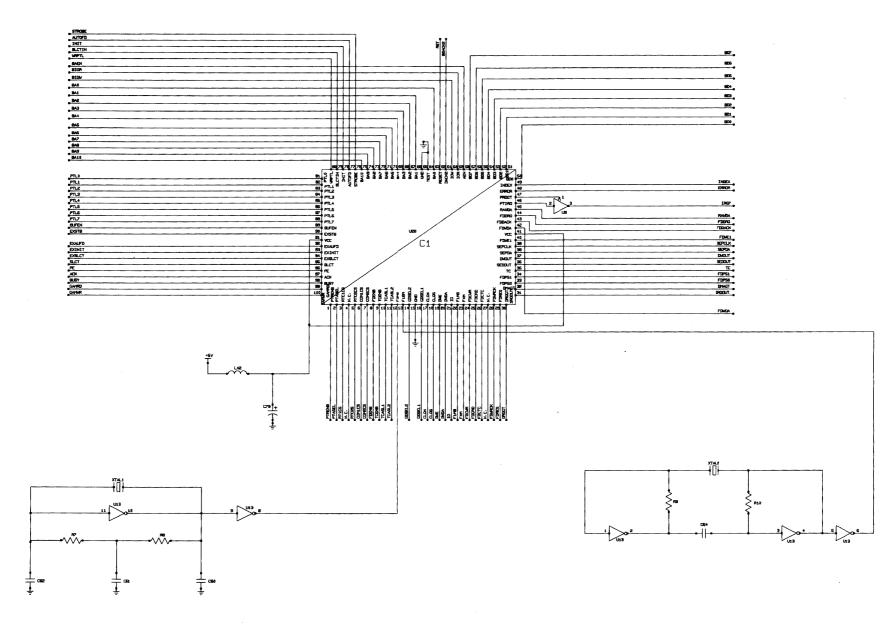

Fig. 3.1 Overall structure

ω 5 The heart of the Multi-I/O Card is a 100 pins flat package Very Large Scale Integration (VLSI) Gate Array C1 (C1 is the code name used by the manufacturer for this particular chip and it will be used throughout this document).

The Gate Array C1 incorporates the hardware logic of :

- . Floppy disk interface support logic for the external Floppy Disk Controller Chip uPD765 or compatibles.

- . One Centronics Parallel Printer Interface.

- . Address decoder and clock generator for two RS232C Serial Ports.

- . Address decoder for Joystick/Game Port.

- . Address decoder for Real-Time Clock chip.

- Logic for backup of protected floppy diskette (Transcopy Function).

Complete functions on the Multi-I/O Card are formed by addition of external LSI chips, buffers, latches, clock generators, battery and the required connectors.

Please refer to Chapter 4 for a complete specification of the Gate Array C1.

#### 3.2 FLOPPY DISK INTERFACE AND TRANSCOPY FUNCTION

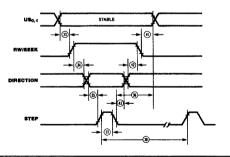

The floppy disk interface on the Multi-I/O Card is designed for double-sided, double-density, MFM-coded floppy disk drive. Up to two 5-1/4" double-sided, double-density floppy disk drives are supported. 3-1/2", 720K, double-sided disk drives with the same data rate and suitable device driver program will also work with the Multi-I/O Card.

#### 3.2.1 Hardware

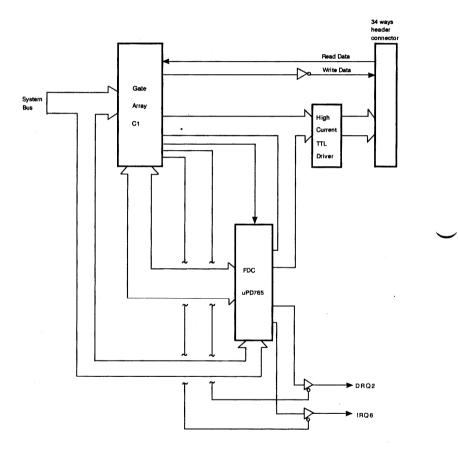

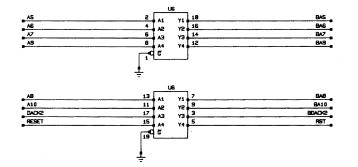

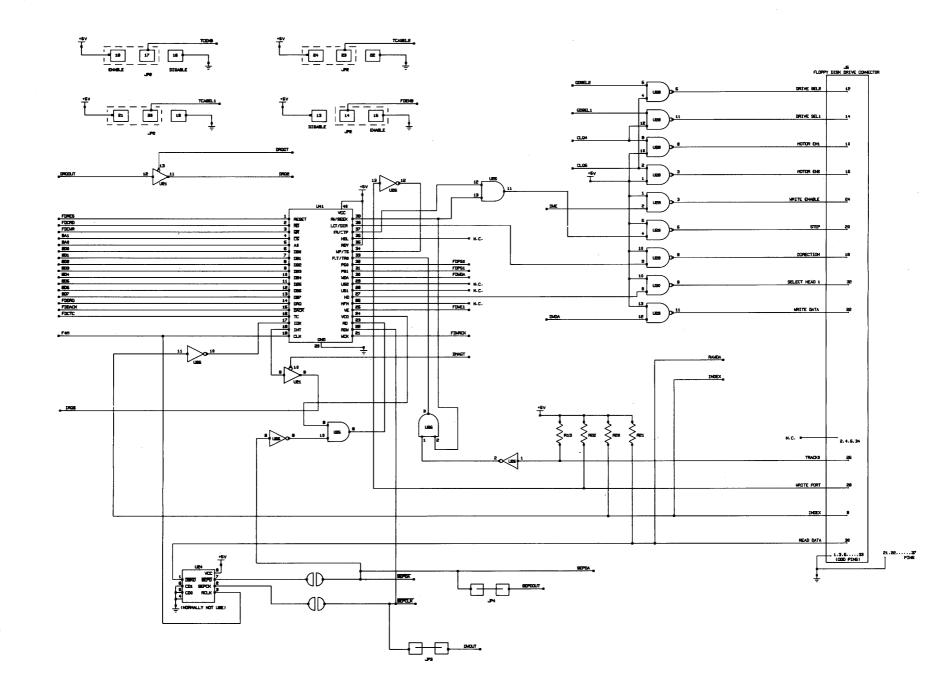

The floppy disk interface section includes a Floppy Disk Controller (FDC) chip uPD765, several high current TTL drivers and some logic circuitry inside the Gate Array C1. The following block diagram illustrates the structure.

#### Fig. 3-2 Floppy Disk Interface

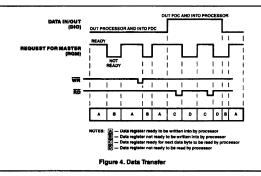

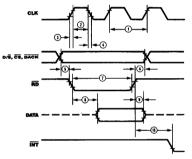

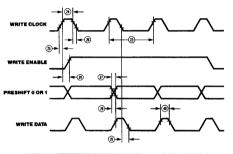

The disk drive parameters of the NEC uPD765 or compatible FDC are programmable. Transfer of data between the system memory and floppy disk controller is accomplished by Direct Memory Access (DMA) channel 2. An interrupt level 6 is also used to indicate when an operation is completed and a status condition requires processor attention.

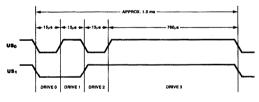

The floppy disk interface employs write precompensation for its record data to improve reliability. Write pre-compensation is controlled by the FDC (uPD765) and performed inside the Gate Array C1. Write pre-compensation constant of 250ns using a 4MHz clock is implemented.

Data recovery of the MFM raw read data from floppy disk drive is done by a digital data separator built inside the Gate Array C1. The digital data separator is a synchronous counter type employing a 16MHz reference clock for higher reliability margin in the separated data.

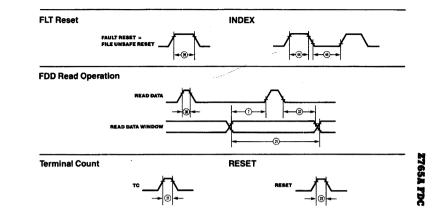

The hardware logic of Transcopy is built entirely inside the Gate Array C1. This part includes a control port, serial to parallel convertor, parallel to serial convertor, status port, data / clock pulse generator and their associated address decoder. When the Transcopy function is activated via proper software, the reading / writing of floppy disk data will go directly through the Transcopy logic and the FDC uPD765 is bypassed. This enables the Transcopy function to resolve the copy-protection schemes used by most software packages. The Transcopy logic uses DMA channel 2 for its operation.

#### 3.2.2 Programming Considerations

The floppy disk interface presents a high level command interface to software I/O drivers. From a programming point of view, the interface consist of an 8-bit digital-output register plus a uPD765 or compatible floppy disk controller. The following table shows the I/O Address used.

| <u>Register</u>                               | I/OAddressUsed (Hex) |

|-----------------------------------------------|----------------------|

|                                               | 255                  |

| FDC Data Register<br>FDC Main Status Register | 3F5<br>3F4           |

| Digital Output Register                       | 3F2                  |

The floppy disk controller (FDC) contains two registers that may be accessed by the system processor: a status register and a data register. The 8-bit main status register contains the status information of the FDC and may be accessed at any time. The 8-bit data register stores data, commands, parameters, and provides floppy drive status information.

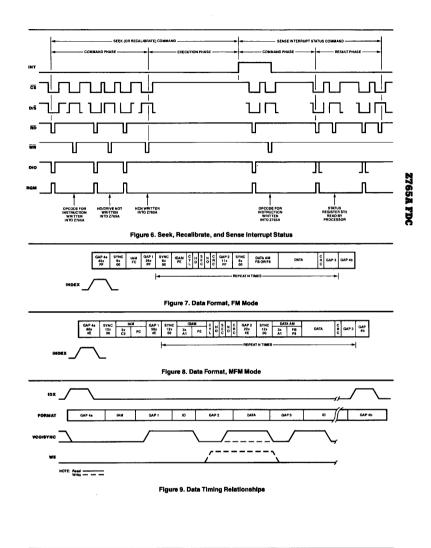

The FDC is capable of executing 15 different commands, each initiated by a multi-byte transfer from the processor. The results of command execution is also a multi-byte transfer back to the processor. Each command can be broadly divided into three phases:

- . Command Phase

- . Execution Phase

- . Result Phase

Please refer to the data sheet of FDC uPD765 in the Appendix for details of these command descriptions.

The digital output register (3F2) is an output-only register used to control drive motors, drive selection and feature enable. All bits are cleared by the I/O interface reset line. The hardware logic for this register, together with other address decoding and DMA support logic, are all built inside the Gate Array C1.

The bits in the digital output register have the following functions:

| Bits 0,1 |                                                                                                                                                                                                      | ed by hardwone drive. | vare to                                                            |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------------------------------------------------------|

|          | Bit 1                                                                                                                                                                                                | Bit 0                 | Drive<br>Selected                                                  |

|          | 0                                                                                                                                                                                                    | 0                     | 0(A)                                                               |

|          | 0                                                                                                                                                                                                    | 1                     | 1 (B)                                                              |

|          | 1                                                                                                                                                                                                    | 0                     | Not applicable                                                     |

|          | 1                                                                                                                                                                                                    | 1                     | Not applicable                                                     |

| Bit 2    |                                                                                                                                                                                                      |                       | 65) is reset when this bit is clear.<br>program to enable the FDC. |

| Bit 3    | This bit, when set, allows the FDC interrupt and<br>DMA request to be gated onto the System Bus.<br>When cleared, interrupt and DMA cannot be<br>generated.                                          |                       |                                                                    |

| Bit 4,5  | These bits controls, respectively, the spindle<br>motors of drive 0 (A) and 1 (B). If they are set while<br>the associated drive is selected, that motor will be<br>turned on. Otherwise, it is off. |                       |                                                                    |

| Bit 6, 7 | Not used.                                                                                                                                                                                            |                       |                                                                    |

The Transcopy hardware appears to the programmer as a single Read/Write I/O port. The address of this I/O port is 7EF/76F/6EF/66F depending on the current jumper block settings.

Bit definitions are as follows:

When CPU write:

| Bit 0      | Transcopy DMA (channel 2) enable. |

|------------|-----------------------------------|

| Bit 1      | Transcopy Read control.           |

| Bit 2      | Transcopy Write control.          |

| Bits 3,4,5 | Internal Counter control.         |

| Bits 6,7   | Transcopy Data Rate control.      |

When CPU read:

| Bits 0-5 | Not used (garbage).                                                |

|----------|--------------------------------------------------------------------|

| Bit 6    | Value of Bit 7 on a previous CPU write operation to this I/O port. |

| Bit 7    | Index signal from floppy disk drive.                               |

All bits are cleared by system reset.

| <u>Pin No.</u> | Function                  |

|----------------|---------------------------|

| 1-33 (odd no.) | Ground                    |

| 2,4,6,34       | Unused                    |

| 8              | Index                     |

| 10             | Motor Enable A            |

| 12             | Drive Select B            |

| 14             | Drive Select A            |

| 16             | Motor Enable B            |

| 18             | Direction (Stepper Motor) |

| 20             | Step Pulse                |

| 22             | Write Data                |

| 24             | Write Enable              |

| 26             | Track 0                   |

| 28             | Write Protect             |

| 30             | Read Data                 |

| 32             | Select Head 1             |

#### 3.3 PARALLEL PRINTER PORT

The parallel printer port on the Multi-I/O card is a Centronics type parallel port. This type of parallel port can be used as a general input / output port for any device or application that matches its signal input / output specification.

#### 3.3.1 Hardware

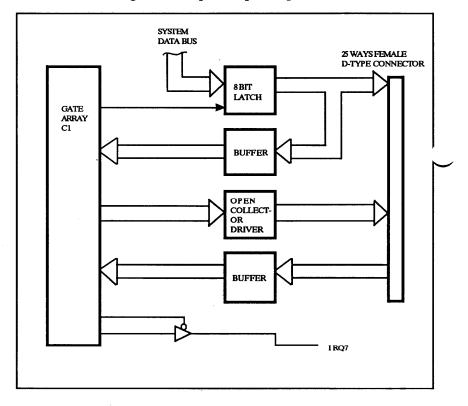

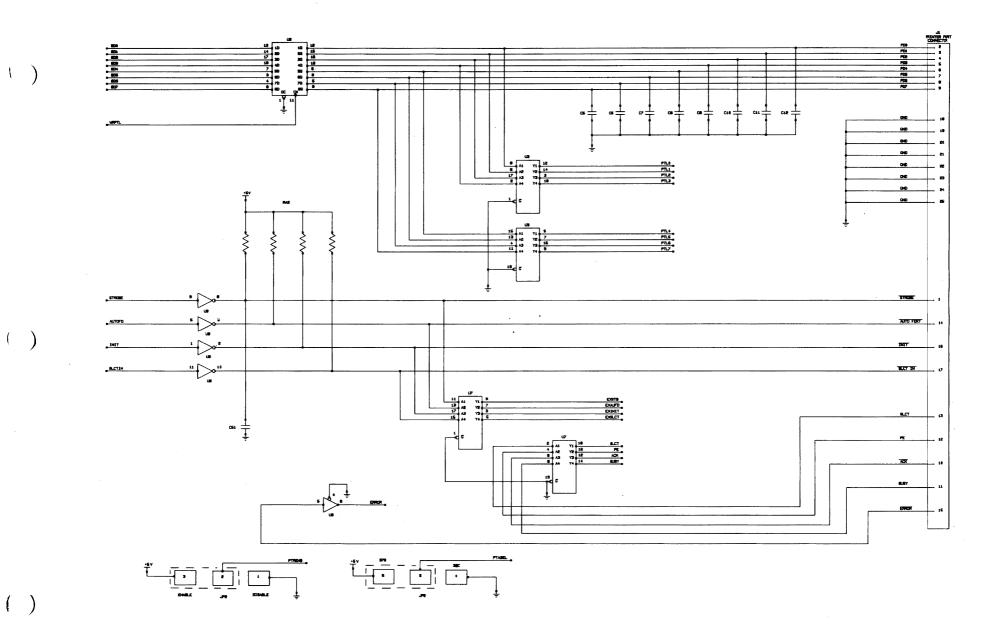

Functional block diagram of the parallel printer port is as follows:

Fig. 3.3 Parallel Printer Port

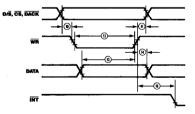

8 bit data are output to the parallel device by writing to an 8-bit register, while status signals can be read through a status register. An input line (ACK) can be used to create an interrupt to the processor when it is properly enabled.

Most of the necessary hardware logic and decoding are built inside the Gate Array C1. Externally, an 8-bit data latch, which also serves as signal driver, plus some open collector drivers and buffer, are needed.

#### 3.3.2 Programming Considerations

The parallel printer port uses I/O Address 378-37A (Hex) or 3BC-3BE (Hex), depending on the current jumper block setting. The hardware appears as registers / latches accessible by the system processor.

| I/O Address (Hex) | Function             |

|-------------------|----------------------|

| 378/3BC           | Printer Data Port    |

| 379/3BD           | Printer Status Port  |

| 37A/3BE           | Printer Control Port |

#### Parallel Data Port 378 / 3BC:

This is an 8-bit read/write parallel data port for the parallel external device. The signal is held stable by latches and can be read back any time via the same I/O Address.

#### Printer Status Port 379 / 3BD:

This is a read only status port which can be accessed by the CPU to check for status of the external parallel device.

| Bit Number | Status    |

|------------|-----------|

| 0          | Not used  |

| 1          | Not used  |

| 2          | Not used  |

| 3          | Not used  |

| 4          | SLCT      |

| 5          | <u>PE</u> |

| 6          | ACK       |

| 7          | BUSY      |

## Printer Control Port 37A / 3BE:

The Printer control port, when written to, presents the following latched control signals to the external parallel device:

| Bit Number | Control Signal |

|------------|----------------|

| 0          | STROBE         |

| 1          | AUTO FD        |

| 2          | INIT           |

| 3          | SLCTIN         |

| 4          | IRQ7 Enable    |

| 5          | Not used       |

| 6          | Not used       |

| 7          | Not used       |

The status of the control signals output being latched by a previous write command to I/O port 37A/3BE, can be read from the same address.

| Bit Number | Status of Control Signal |  |  |

|------------|--------------------------|--|--|

| 0          | STROBE                   |  |  |

| 1          | AUTOFD                   |  |  |

| 2          | INIT                     |  |  |

| 3          | SLCTIN                   |  |  |

| 4          | Not used                 |  |  |

| 5          | Not used                 |  |  |

| 6          | Not used                 |  |  |

| 7          | Not used                 |  |  |

System interrupt level 7 can be enabled by setting bit 4 in the Printer Control Port (37A / 3BE) and activating the ACK input line.

| <u>Pin No</u> | Function         |

|---------------|------------------|

| 1             | STROBE           |

| 2             | Parallel Data D0 |

| 3             | Parallel Data D1 |

| 4             | Parallel Data D2 |

| 5             | Parallel Data D3 |

| 6             | Parallel Data D4 |

| 7             | Parallel Data D5 |

| 8             | Parallel Data D6 |

| 9             | Parallel Data D7 |

| 10            | ACK              |

| 11            | BUSY             |

| 12            | PE               |

| 13            | SLCT             |

| 14            | AUTO FD          |

| 15            | ERROR            |

| 16            | INIT             |

| 17            | SLCTIN           |

| 18-25         | GROUND           |

## 3.4 RS232C SERIAL INTERFACE PORTS

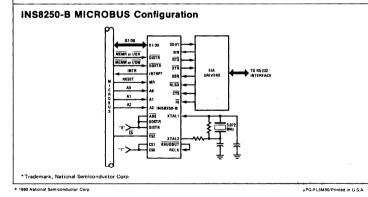

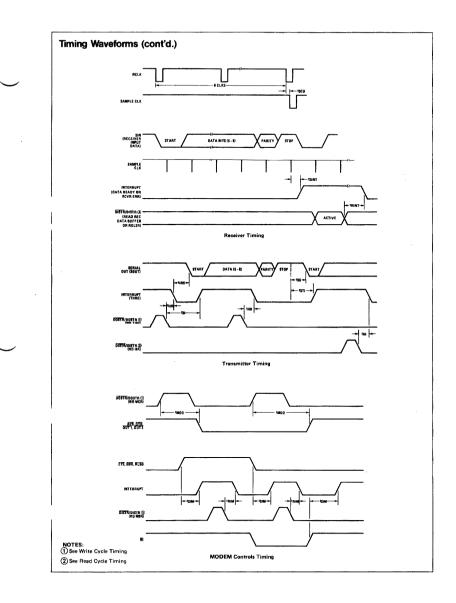

The Multi-I/O card supports up to two RS232C Serial Interface Ports. They are designated as COM1 and COM2 in accordance with their I/O Address 3F8-3FF (Hex) and 2F8-2FF (Hex) respectively. These serial ports provide interface for serial devices including modem, serial printer and terminal.

The serial communication ports are fully programmable and supports asynchronous communications only. They add and remove start bits, stop bits and parity bits. A programmable baud rate generator allows operation from 50 baud to 9600 baud. Five, six, seven or eight bit characters with 1, 1-1/2 or 2 stop bits are supported.

|--|

Each serial port has it assigned level of system interrupt. A fully prioritized interrupt system within each serial port controls transmit, receive, error, line status and data set interrupts. Diagnostic capabilities provide loopback functions of transmit / receive and input / output signals.

## 3.4.1 Hardware Description

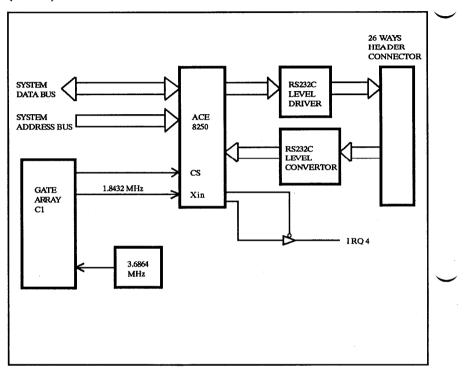

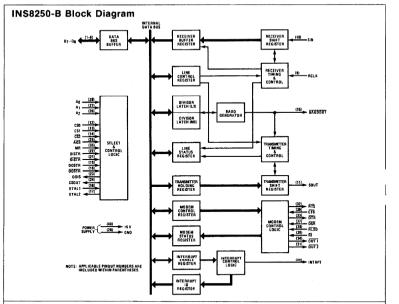

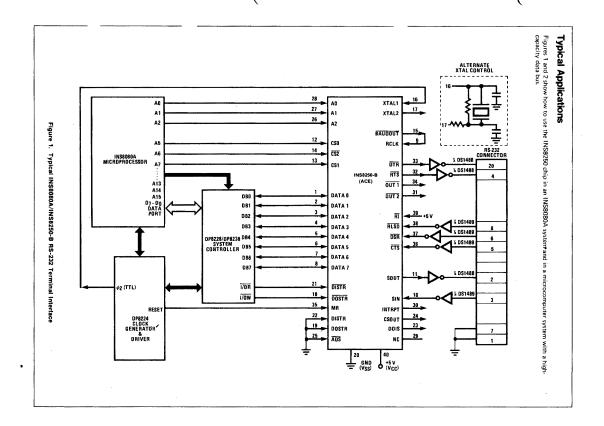

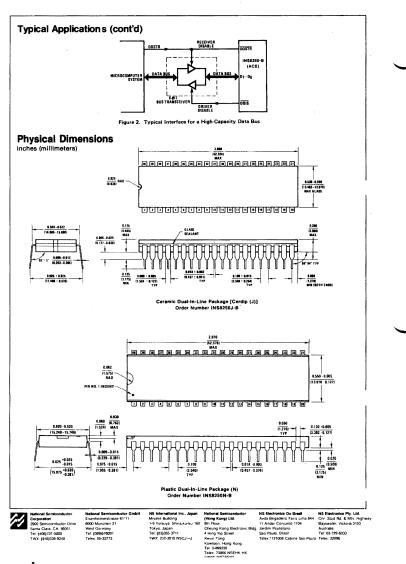

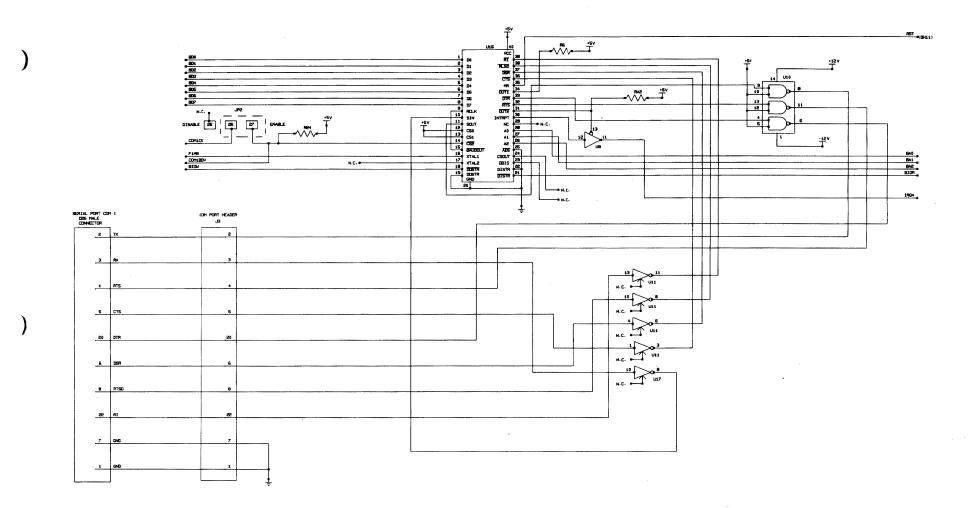

Following is a block diagram of hardware for one serial port (COM1).

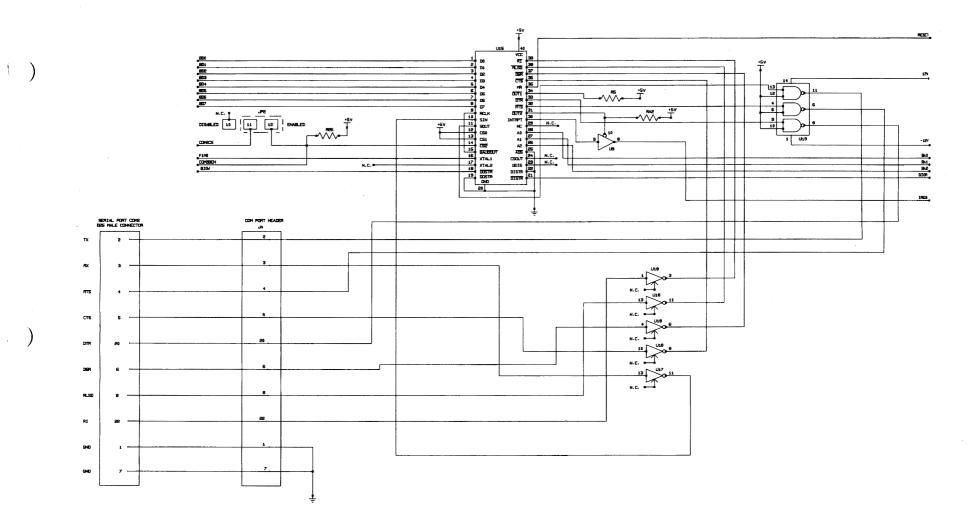

Fig. 3.4 RS232C Serial Interface Port

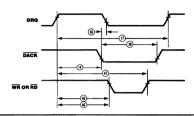

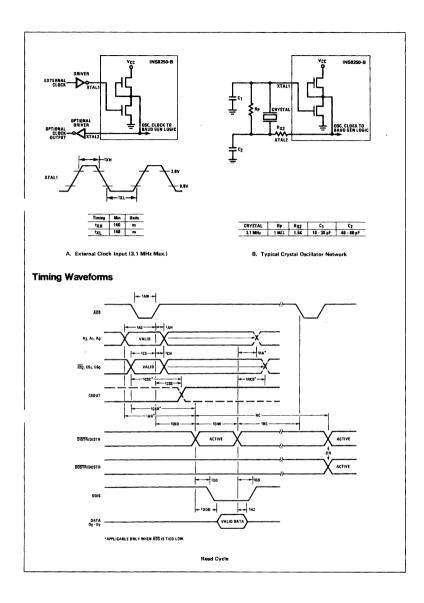

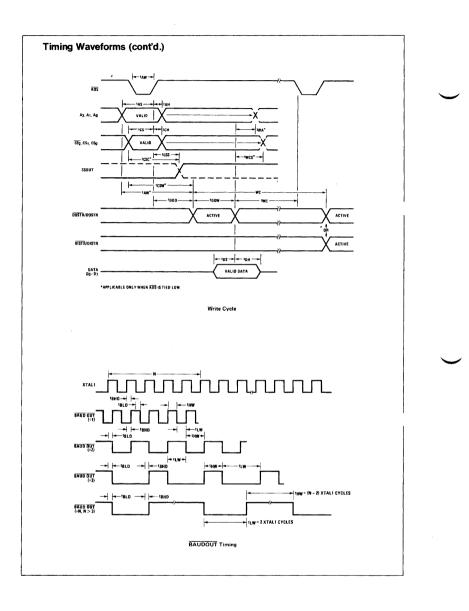

The heart of the Serial Communication Port is the INS8250 Asynchronous Communication Element (ACE), or its functional equivalent. Address decoding and clock generation is done in Gate Array C1. A 3.6864MHz signal input to Gate Array C1 is divided by two and fed to the INS8250 ACE chip as a 1.8432 MHz master clock. Baud rates of 50 to 9600 are generated from this 1.8432 MHz signal.

The serial data output, together with modem control output from the ACE, are changed from TTL voltage into RS232C voltage levels via signal drivers 1488 or equivalent. Conversely, RS232C voltage levels are converted back to TTL levels by signal converters 1489 or equivalent and fed to the ACE inputs.

### 3.4.2 Programming Considerations

Apart from the general function listed above, the ACE also features:

- Full double buffering eliminates extra hardware / software for precise synchronization.

- Modem control functions of Clear to Send (CTS), Request to Send (RTS), Data Set Ready (DSR), Data Terminal Ready (DTR), Ring Indicator (RI), and Carrier Detect.

- False start bit detection.

- Line break generation and detection.

The INS8250 ACE is fully programmable for each function and any communication protocol must be loaded before the serial port is operational. This is done by selecting the proper I/O Address for each Serial Port. The following tables summarizes the I/O Address assigned to the internal registers of INS8250 ACE in the Multi-I/O card. The divisor latch access bit DLAB (bit7) of the line control register is used to select certain register.

| I/O De<br>(in Hex)                                                 |                                                                           |                                                                                                                                                                                                                                                  |                                                   |

|--------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| COM1                                                               | COM2                                                                      | Register<br>Selected                                                                                                                                                                                                                             | DLAB State                                        |

| 3F8<br>3F8<br>3F8<br>3F9<br>3F9<br>3F4<br>3FA<br>3FC<br>3FD<br>3FE | 2F8<br>2F8<br>2F9<br>2F9<br>2F9<br>2FA<br>2FA<br>2FB<br>2FC<br>2FD<br>2FE | TX Buffer<br>RX Buffer<br>Divisor Latch LSB<br>Divisor Latch MSB<br>Interrupt Enable<br>Register<br>Interrupt Identification<br>Registers<br>Line Control Register<br>Modem Control<br>Register<br>Line Status Register<br>Modem Status Register | DLAB=0(Write)<br>DLAB=0(Read)<br>DLAB=1<br>DLAB=1 |

## I/O Decodes

| Hex | Hex Address 3F8 to 3FF and 2F8 to 2FF |   |   |   |   |   |   |   |     |          |                                                          |

|-----|---------------------------------------|---|---|---|---|---|---|---|-----|----------|----------------------------------------------------------|

| A9  | A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 DLAB    |   |   |   |   |   |   |   |     | Register |                                                          |

| 1   | 1/0                                   | 1 | 1 | 1 | 1 | 1 | X | X | x   |          |                                                          |

|     |                                       |   |   |   |   |   | 0 | 0 | 0   | 0        | Receive Buffer (read)<br>Transmit<br>Holding Reg (write) |

| 1   |                                       |   |   |   |   |   | 0 | 0 | 1   | 0        | Interrupt Enable                                         |

|     |                                       |   |   |   |   |   | 0 | 1 | 0   | x        | Interrupt Identification                                 |

|     |                                       |   |   |   |   |   | 0 | 1 | 1   | х        | Line Control                                             |

| 1   |                                       |   |   |   |   |   | 1 | 0 | 0   | x        | Modem Control                                            |

|     | 1                                     |   |   |   |   |   | 1 | 0 | 1 . | X        | Line Status                                              |

|     |                                       |   |   |   |   |   | 1 | 1 | 0   | х        | Modem Status                                             |

|     |                                       |   |   |   |   | 1 | 1 | 1 | 1   | х        | None                                                     |

|     |                                       |   | 1 |   |   | 1 | 0 | 0 | 0   | 1        | Divisor Latch (LSB)                                      |

|     |                                       |   |   |   |   |   | 0 | 0 | 1   | 1        | Divisor Latch (MSB)                                      |

## Address Bits

Note: Bit 8 will be logical 1 for the port designated as COM1 or a logical 0 for the port designated as COM2.

A2, A1 and A0 bits are used to select the different register of the communications chip.

Please refer to the data sheet of ACE INS8250 in the Appendix for details of these internal registers.

| <u>Pin No.</u> | <b>Function</b> |

|----------------|-----------------|

| 1              | Ground          |

| 2              | TX              |

| 3              | RX              |

| 4              | RTS             |

| 5              | CTS             |

| б              | DSR             |

| 7              | Ground          |

| 8              | RLSD            |

| 9-19           | Not used        |

| 20             | DTR             |

| 21             | Not used        |

| 22             | RI              |

| 23-26          | Not used        |

| <u>Pin No.</u> | Function |

|----------------|----------|

| 1              | Ground   |

| 2              | TX       |

| 3              | RX       |

| 4              | RTS      |

| 5              | CTS      |

| 6              | DSR      |

| 7              | Ground   |

| 8              | RLSD     |

| 9-19           | Not used |

| 20             | DTR      |

| 21             | Not used |

| 22             | RI       |

| 23-25          | Not used |

## 3.5 GAME PORT

The Game Port on the Multi-I/O Card allows up to four game paddles or two joysticks to be attached. In addition, inputs for four switch buttons are provided. Paddle and joystick positions are determined by the variable resistance values sensed by the Joystick/ Game Port. The real-time resistive values are converted into a relative paddle or joystick position via appropriate software.

### 3.5.1 Hardware

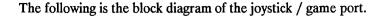

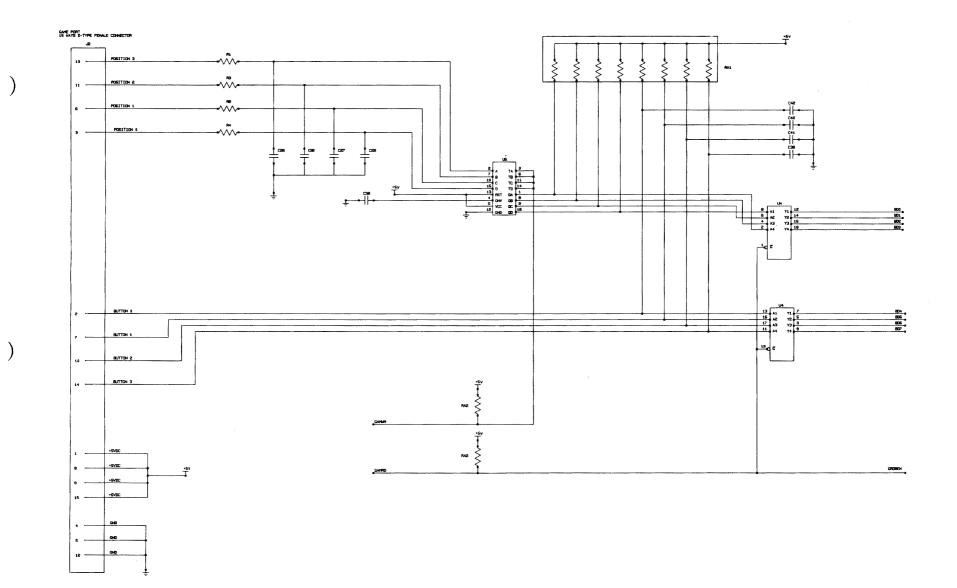

Fig. 3.5 Joystick/Game Port

The chip for conversion of resistance value into digital state is the Quad-Timer NE558 or equivalent. Address decoding for the Joystick / Game Port is provided by the Gate Array C1. I/O Address for triggering of four monostable timers as well as reading of position / button status byte is 201 Hex. The position/button status are gated via data buffer with its enable line decoded from Gate Array C1.

## 3.5.2 Programming Considerations

The Joystick / Game Port appears to the programmer as one Read/ Write Port with I/O Address 201 Hex.

When an I/O write command is issued to port address 201 Hex, irrespective of the data written, all four monostable outputs go high and will remain high for varying periods of time depending on the position each variable resistor of the joystick is set. The variable resistance on the joystick should have a range from 0 to 100K-ohms.

These four monostable timer outputs are read by an I/O read command from port address 201 Hex and are reflected on data bits 0 through 3.

Bit 4 through 7 of the I/O port reflects the real-time status of the switch buttons. These buttons default to an open state and are read as "1". When a button is pressed, it is read as "0:". Programmers should note that these buttons are not debounced by hardware.

| Bit Number | Function        |

|------------|-----------------|

| 0          | Position 0      |

| 1          | Position 1      |

| 2          | Position 2      |

| 3          | Position 3      |

| 4          | Switch Button 0 |

| 5          | Switch Button 1 |

| 6          | Switch Button 2 |

| 7          | Switch Button 3 |

| 1  | +5VDC      |

|----|------------|

| 2  | Button 0   |

| 3  | Position 0 |

| 4  | Ground     |

| 5  | Ground     |

| 6  | Position 1 |

| 7  | Button 1   |

| 8  | +5VDC      |

| 9  | +5VDC      |

| 10 | Button 2   |

| 11 | Position 2 |

| 12 | Ground     |

| 13 | Position 3 |

| 14 | Button 3   |

| 15 | +5VDC      |

|    |            |

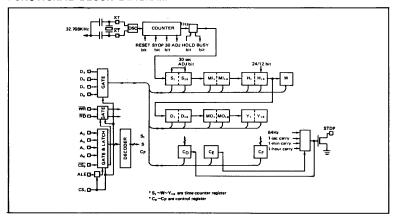

## 3.6 REAL-TIME CLOCK

The Multi-I/O Card is equipped with a Real-Time Clock and rechargeable battery backup. This function maintains the time and calendar, and, with suitable software, allows automatic setting up of time and date each time the computer is turned on.

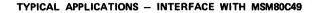

## 3.6.1 HARDWARE

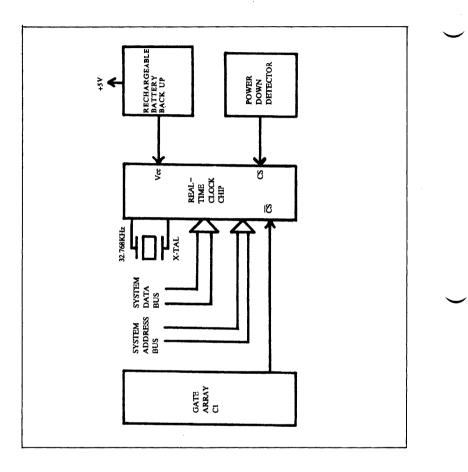

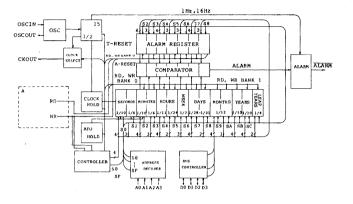

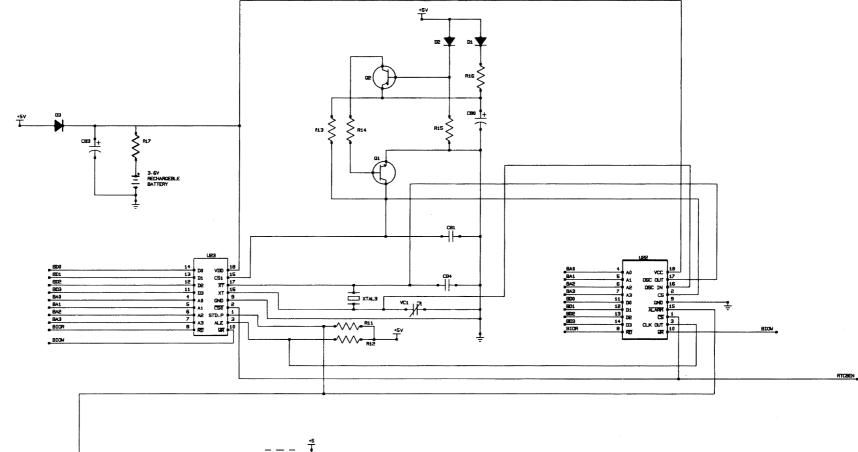

Following is a block diagram of the Real-Time Clock.

Fig. 3.6 Real-Time Clock

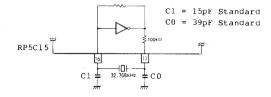

The heart of the Real-Time Clock is the real-time clock chip. The Multi-I/O Card has made provision to work with two different realtime clock chips, namely, the OKI MSM 6242 or the RICOH RP5C15. These chips are on different locations of the PCB.

The real-time clock chip runs with a clock of 32.768 KHz for its internal counting operation.

This chip normally draws power from the computer's +5V supply when the computer is turned ON. The backup battery is recharged from the +5V supply. When the power is OFF, the backup battery replaces the normal +5V to keep the chip running.

A power down detection circuitry is added to pull the CS line of the real-time clock chip to logic low as soon as the computer's +5V supply is dropping. This prevents transient garbage to be written to the chip during power down.

Address decoding for the real-time clock chip is done in Gate Array C1. The I/O Address range used is 340-35F (Hex) or 2C0 - 2DF (Hex), depending on the current jumper block setting.

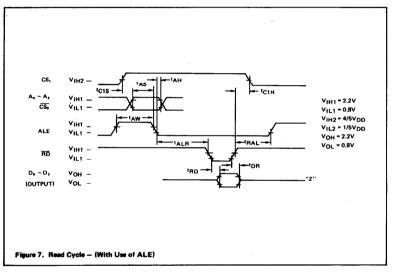

## 3.6.2 Programming Considerations

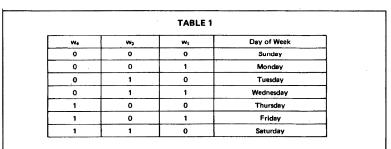

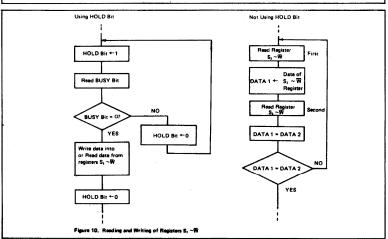

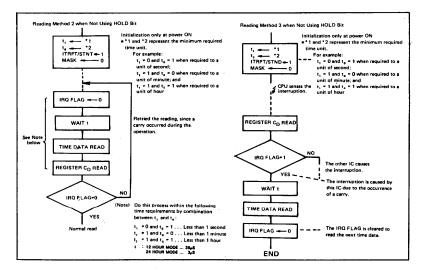

The Real-Time Clock function appears to the programmer as a number of CPU addressable registers. These registers serve functions including second, minute, hour, day, month, year and days of the week.

The real-time clock chip incorporates 16 such registers, while the Gate Array C1 decodes 32 different addresses. The upper 16 addresses map to the lower 16 addresses.

The Real-Time Clock utility programs SETCLOCK,GETCLOCK supplied with the card automatically handle the different chips used and different addresses selected.

Refer to the Appendix for detail meaning of the real-time clock chip registers.

# **CHAPTER 4**

## GATE ARRAY C1

## CHAPTER 4 GATE ARRAY C1

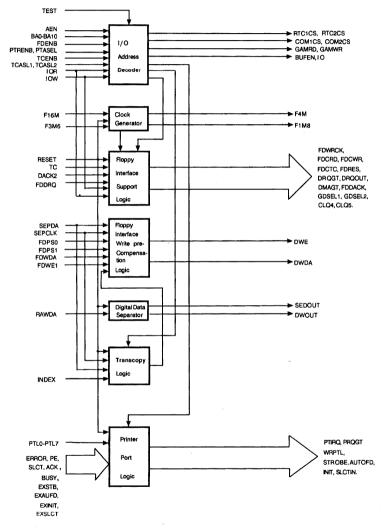

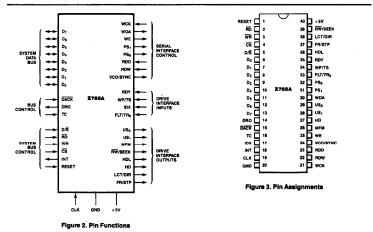

The Gate Array C1 is a 100 pins flat package VLSI Gate Array designed to implement a number of I/O functions for the IBM<sup>®</sup>PC, PC/XT and compatibles.

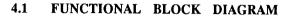

It consists of the logic circuitry for the following popular I/O features:

- Floppy disk interface support logic for the Floppy Disk Controller Chip uPD765.

- One Centronics Parallel Printer Interface.

- Address decoders for two RS232C Serial ports.

- Address decoder of a Joystick/Game Port

- Address decoder for a Real-Time Clock Chip.

- Logic circuitry for backup of copy-protected diskette (Transcopy Function).

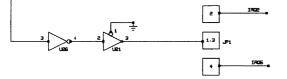

Fig 4.1 Gate Array C1 Function Diagram

## 4.2 PIN ASSIGNMENT AND SIGNAL DESCRIPTION

Abbreviation on pin type:

|            | I<br>O<br>I/O | Input<br>Output<br>Bi-directional |                                                                                                      |

|------------|---------------|-----------------------------------|------------------------------------------------------------------------------------------------------|

| Pin<br>No. | Pin<br>type   | Name                              | Description                                                                                          |

| 1          | I             | PTRENB                            | Printer Port enable line.<br>Active high input.<br>1=printer port enabled<br>0=printer port disabled |

| 2          | Ι             | PTASEL                            | Printer Port I/O address select.<br>1=378-37A (Hex)<br>0=3BC-3BF (Hex)                               |

| 3          | Ο             | RTC1CS                            | Real-Time Clock 1 address decoder.<br>Active low output.<br>Address range=340-35F (Hex)              |

| 4          | 1             | N.C.                              | No connection.                                                                                       |

| 5          | 0             | RTC2CS                            | Real-Time Clock 2 address decoder.<br>Active low output.<br>Address range = 2C0-2DF (Hex)            |

| 6          | 0             | COM1CS                            | RS232C Serial Port 1 address de-<br>coder.<br>Active low output.<br>Address range=3F8-3FF (Hex)      |

| 7          | Ο             | COM2CS                            | RS232C Serial Port 2 address de-<br>coder.<br>Active low output.<br>Address range=2F8-2FF (Hex)      |

4-4

|   | 8  | I | FDENB  | Floppy Disk Interface e<br>Active low input.<br>0=Floppy Interface ena<br>1=Floppy Interface disa                                                          |                                                                     | led                      |  |

|---|----|---|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------|--|

| _ | 9  | Ι | TCENB  | Transcopy Function ena<br>Active high input.<br>1=Transcopy Function<br>0=Transcopy Function                                                               |                                                                     | enabled                  |  |

|   | 10 | I | TCASL1 | Transcopy 1                                                                                                                                                | Function addre                                                      | ess select 1.            |  |

|   | 11 | I | TCASL2 | Transcopy Function address select 2<br>Different combinations of TCASL1,<br>TCASL2 results in one of four<br>possible addresses for Transcopy<br>Function: |                                                                     |                          |  |

|   |    |   |        | TCASL2                                                                                                                                                     | TCASL1                                                              | <u>I/O</u><br>Address    |  |

| _ |    |   |        | 0<br>0<br>1<br>1                                                                                                                                           | 0<br>1<br>0<br>1                                                    | 7EF<br>76F<br>6EF<br>66F |  |

|   | 12 | I | F3M6   | 3.6864MHz<br>The signal i<br>Array C1 to                                                                                                                   | s divided by 2<br>generate a 1<br>al for the seria                  | in Gate<br>.8432MHz      |  |

| ~ | 13 | I | F16M   | oscillator.<br>All necessar<br>Floppy Disl                                                                                                                 | from an extern<br>ry timing signa<br>(Interface are<br>(MHz signal) | ll for the               |  |

| .14 | 0 | GDSEL2 | Partially decoded Drive B select<br>signal for the Floppy Disk Interface.<br>Active high output.<br>This signal should be NAND with<br>CLQ5 to produce the valid Drive B<br>select signal. |

|-----|---|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | / | GND    | 0 V                                                                                                                                                                                        |

| 16  | 0 | GDSEL1 | Partially decoded Drive A select<br>signal for the Floppy Disk Interface.<br>Active high output.<br>This signal should be NAND with<br>CLQ4 to produce the valid Drive A<br>select signal. |

| 17  | 0 | CLQ4   | Motor enable signal for floppy disk<br>drive A.<br>Active high output.                                                                                                                     |

| 18  | 0 | CLQ5   | Motor enable signal for floppy disk<br>drive B.<br>Active high output.                                                                                                                     |

| 19  | 0 | DWE    | Floppy drive write enable signal.<br>Active high output.                                                                                                                                   |

| 20  | 0 | DWDA   | Floppy drive write data signal.<br>Active high output.                                                                                                                                     |

| 21  | 0 | Ю      | This signal is a logical AND of the<br>IOR, IOW.<br>Active low output, indicating I/O<br>Read, I/O Write is in progress.                                                                   |

| 22  | 0 | F1M8   | This signal is a 1.8432MHz square<br>wave output signal derived from the<br>3.6864MHz input signal.                                                                                        |

| )        | 23 | 0 | F4M    | This is a 4MHz square wave output<br>derived from the 16MHz input signal.<br>This signal is used as the clock input of<br>an external FDC uPD765, or as the<br>reference clock in an external data<br>separator WD9216. |

|----------|----|---|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 24 | 0 | FDCWR  | Decoded output signal to the Write<br>input of an external FDC uPD765.<br>Active low output.<br>This line is activated when the CPU<br>writes to the FDC or DMA write to the<br>FDC is in progress.                     |

|          | 25 | Ο | FDCRD  | Decoded output signal to the Read<br>input of an external FDC uPD765.<br>Active low output.<br>This line is activated when the CPU<br>reads from the FDC or DMA read<br>from the FDC is in progress.                    |

| $\smile$ | 26 | Ο | FDCTC  | Terminal count output to an external<br>FDC uPD765.<br>Active high output. This line is acti-<br>vated at the end of each DMA transfer<br>for Floppy Disk Interface.                                                    |

|          | 27 | / | N.C.   | No connection.                                                                                                                                                                                                          |

|          | 28 | 0 | FDWRCK | Write clock output to an external FDC<br>uPD765.<br>500 KHz positive going pulse signal.                                                                                                                                |

|          | 29 | Ο | FDRES  | Reset output to an external FDC<br>uPD765.<br>Active high output. This line is activate<br>when a "0" is written to the Digital<br>Output Register (Hex 03F2) of the<br>Floppy Disk Interface inside the Gate<br>Array. |

| 30 | 0 | DRQGT  | Control output for Floppy Disk Interface<br>DMA Request. Active low output.<br>This line is used for enabling an external<br>tri-state buffer (LS125) which has output<br>driving the system DMA Request channel<br>2.                              |

|----|---|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 | 0 | DRQOUT | Floppy Disk Interface DMA Request.<br>Normally tri-state with active high output.<br>This line is connected to a tri-state buffer<br>(LS125) which drives the system DMA<br>Request channel 2.                                                      |

| 32 | 0 | DMAGT  | Control output for Floppy Disk Interface<br>Interrupt Request. Active low output.<br>This line is used for enabling an external<br>tri-state buffer (LS125) which has input<br>from the uPD765 Interrupt line, and drive<br>the system IRQ level 6. |

| 33 | I | FDPS0  | Floppy Disk Interface Write Precomp 0.                                                                                                                                                                                                              |

| 34 | I | FDPS1  | Floppy Disk Interface Write Precomp 1.                                                                                                                                                                                                              |

|    |   |        | FDPS0,FDPS1 are input signals from an external FDC uPD765.<br>These two signals controls the amount of write pre- compensation to be effected on the write data to floppy disk drive. Maximum write pre-compensation is +/-250nS.                   |

| 35 | I | TC     | System Terminal Count.<br>Active high input.                                                                                                                                                                                                        |

| 36 | 0 | SEDOUT | Separated Data out.<br>Active low output from an internal digital<br>data separator inside the Gate Array. The<br>active duration of the pulse output is<br>62.5nS.                                                                                 |

| <u> </u> | 37 | 0 | DWOUT  | Data Window out.<br>This is a 250KHz rectangular wave<br>output from the internal digital data<br>separator inside the Gate Array. The<br>phase (edges) of this signal will shift<br>back and forth according to the raw<br>read data from the floppy disk drive.                                                                                                                                                                                    |

|----------|----|---|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 38 | I | SEPDA  | Separated Data input.<br>This is the separated read data for use<br>by Floppy Disk Interface and the<br>Transcopy Function. If the internal<br>digital data separator is used, this pin<br>should be connected to the SEDOUT<br>(pin 36) of the Gate Array. If an<br>external data separator is adopted, this<br>pin should be connected to the sepa-<br>rated data output from the external data<br>separator.                                      |

| <u> </u> | 39 | Ι | SEPCLK | Separated Clock input.<br>This is the separated clock, or the data<br>window used by the Floppy Disk<br>Interface and the Transcopy Function.<br>If the internal digital data separator is<br>used, this pin should be connected to<br>the DWOUT (pin 37) of the same Gate<br>Array. If an external data separator is<br>adopted, this pin should be connected<br>to the separated clock, or data window<br>output from the external data separator. |

|          | 40 | I | FDWE1  | Floppy disk drive write enable.<br>Active high input from an external<br>FDC uPD765.                                                                                                                                                                                                                                                                                                                                                                 |

|          | 41 | / | VCC    | +5V DC supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <u> </u> | 42 | Ι | FDWDA  | Floppy disk write data.<br>Active high input from an external<br>FDC uPD765. This write data is not<br>yet write pre-compensated.                                                                                                                                                                                                                                                                                                                    |

| 43 | 0   | FDDACK | Floppy Disk Interface DMA<br>Acknowledge.<br>Active high output signal to an<br>external FDC uPD765.                                                                                   |

|----|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 44 | Ι   | FDDRQ  | Floppy Disk Interface DMA<br>Request.<br>Active high input signal from an<br>external FDC uPD765.                                                                                      |

| 45 | I   | RAWDA  | Raw read data from floppy disk drive.<br>Active low input which is used by the<br>internal digital data separator.                                                                     |

| 46 | 0   | PTIRQ  | Printer Port interrupt request.<br>Tri-state normally, high when active.<br>This pin should connect to a tri-state<br>buffer (LS125) which drives the<br>system Interrupt level 7.     |

| 47 | 0   | PRQGT  | Printer Port interrupt request control.<br>Active low output.<br>This pin should be used for control-<br>ling a tri-state buffer (LS125) which<br>drives the system Interrupt level 7. |

| 48 | I   | ERROR  | Printer status signal - ERROR.                                                                                                                                                         |

| 49 | Ι   | INDEX  | Floppy disk drive Index signal.<br>Active low input.<br>This signal is used by the Transcopy<br>logic inside the Gate Array.                                                           |

| 50 | I/O | BD0    | Data line D0                                                                                                                                                                           |

| 51 | I/O | BD1    | Data line D1                                                                                                                                                                           |

| 52 | I/O | BD2    | Data line D2                                                                                                                                                                           |

| 53 | I/O | BD3    | Data line D3                                                                                                                                                                           |

| 54 | I/O | BD4   | Data line D4                                                                                         |

|----|-----|-------|------------------------------------------------------------------------------------------------------|

| 55 | I/O | BD5   | Data line D5                                                                                         |

| 56 | I/O | BD6   | Data line D6                                                                                         |

| 57 | I/O | BD7   | Data line D7                                                                                         |

| 58 | Ι   | AEN   | System Address Enable. Active low input. All CPU Read/Write takes place when AEN is active.          |

| 59 | I   | IOR   | System I/O Read.<br>Active low input.                                                                |

| 60 | Ι   | IOW   | System I/O Write.<br>Active low input.                                                               |

| 61 | Ι   | DACK2 | System DMA channel 2 Acknowl-<br>edge. Active low input.                                             |

| 62 | I   | RESET | System Reset. Active high input.                                                                     |

| 63 | I   | BA0   | Address line A0                                                                                      |

| 64 | Ι   | TEST  | Test input for factory diagnostic<br>purpose. Must be grounded (tie to 0<br>V) for normal operation. |

| 65 | /   | GND   | 0 V                                                                                                  |

| 66 | Ι   | BA1   | Address line A1                                                                                      |

| 67 | Ι   | BA2   | Address line A2                                                                                      |

| 68 | Ι   | BA3   | Address line A3                                                                                      |

| 69 | I   | BA4   | Address line A4                                                                                      |

| 70 | I   | BA5   | Address line A5                                                                                      |

| 71 | I   | BA6   | Address line A6                                                                                      |

|    |     |       |                                                                                                      |

4-11

| 72                                           | I                               | BA7                                                          | Address line A7                                                                                                                                                                                                                                                                                              |

|----------------------------------------------|---------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 73                                           | I                               | BA8                                                          | Address line A8                                                                                                                                                                                                                                                                                              |

| 74                                           | Ι                               | BA9                                                          | Address line A9                                                                                                                                                                                                                                                                                              |

| 75                                           | I                               | BA10                                                         | Address line A10                                                                                                                                                                                                                                                                                             |

| 76                                           | 0                               | STROBE                                                       | Printer control output - STROBE                                                                                                                                                                                                                                                                              |

| 77                                           | 0                               | AUTOFD                                                       | Printer control output - AUTOFD                                                                                                                                                                                                                                                                              |

| 78                                           | 0                               | INIT                                                         | Printer control output - INIT                                                                                                                                                                                                                                                                                |

| 7 <b>9</b>                                   | 0                               | SLCT IN                                                      | Printer control output - SLCT IN                                                                                                                                                                                                                                                                             |

| 80                                           | 0                               | WRPTL                                                        | Printer Port parallel data latch<br>signal.<br>Active low output.<br>Decoded address = 378/3BC (Hex)                                                                                                                                                                                                         |

| 81<br>82<br>83<br>84<br>85<br>86<br>87<br>88 | I<br>I<br>I<br>I<br>I<br>I<br>I | PTL0<br>PTL1<br>PTL2<br>PTL3<br>PTL4<br>PTL5<br>PTL6<br>PTL7 | Printer Port parallel data 0 input<br>Printer Port parallel data 1 input<br>Printer Port parallel data 2 input<br>Printer Port parallel data 3 input<br>Printer Port parallel data 4 input<br>Printer Port parallel data 5 input<br>Printer Port parallel data 6 input<br>Printer Port parallel data 7 input |

| 89                                           | 0                               | BUFEN                                                        | Enable signal for an external data<br>buffer (LS245) connected between<br>the data lines of the Gate Array and<br>the system data bus                                                                                                                                                                        |

| 90                                           | I                               | EXSTB                                                        | Printer status signal - STROBE                                                                                                                                                                                                                                                                               |

| 91                                           | /                               | VCC                                                          | +5V DC supply voltage.                                                                                                                                                                                                                                                                                       |

| 92                                           | Ι                               | EXAUFD                                                       | Printer status signal - AUTOFD                                                                                                                                                                                                                                                                               |

| 93                                           | I                               | EXINIT                                                       | Printer status signal - INIT                                                                                                                                                                                                                                                                                 |

| 94  | I | EXSLCT | Printer status signal - SLCT IN                                                   |

|-----|---|--------|-----------------------------------------------------------------------------------|

| 95  | Ι | SLCT   | Printer status signal - SLCT                                                      |

| 96  | I | PE     | Printer status signal - PE                                                        |

| 97  | Ι | ACK    | Printer status signal - ACK                                                       |

| 98  | Ι | BUSY   | Printer status signal - BUSY                                                      |

| 99  | 0 | GAMRD  | Game Port Read signal.<br>Active low output.<br>I/O address decoded = 201 (Hex)   |

| 100 | 0 | GAMWR  | Game Port Timer Trigger.<br>Active low output.<br>I/O address decoded = 201 (Hex) |

## 4.3 ELECTRICAL SPECIFICATIONS

| Parameter             | Symbol | Rating       | Unit |

|-----------------------|--------|--------------|------|

| Supply voltage        | Vcc    | -0.3~+6.7    | v    |

| Terminal voltage      | Vt     | -0.3~Vcc+0.3 | V    |

| Output Current        |        |              |      |

| - per one output      | Io     | -8~+8        | mA   |

| - total               | Iot    | -40~+40      | mA   |

| Operating Temperature | Topr   | -20~+75      | С    |

| Storage Temperature   |        |              |      |

| - with Bias           | Tbias  | -20~+85      | С    |

| - without Bias        | Tstg   | -55~+125     | С    |

## 4.3.1 Absolute Maximum Ratings

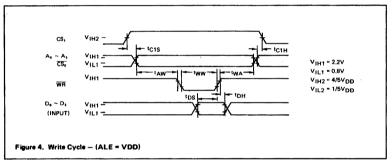

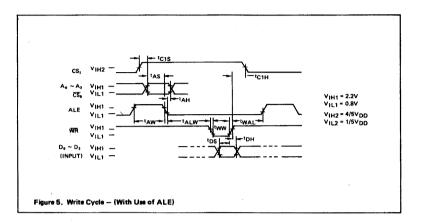

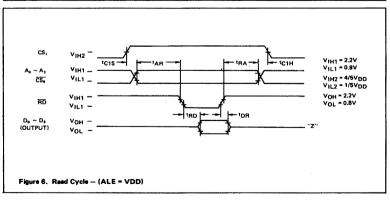

## 4.3.2 Electrical Characteristics

Vcc = 5V +/- 5%, Ta = -20° to  $75^{\circ}$ C

| Parameter              | Symbol       | min  | max     | unit |

|------------------------|--------------|------|---------|------|

| Input Voltage          | VIH          | 2.2  | Vcc+0.3 | v    |

|                        | VIL          | -0.3 | 0.8     | V    |

| Output Voltage         | VOH          | 3.5  |         | V    |

| _                      | (IOH = -2mA) |      |         |      |

|                        | VOL          |      | 0.5     | V    |

|                        | (IOL = 5mA)  |      |         |      |

| Input Leakage Current  | ILI          |      | 1       | υA   |

| Output Leakage Current | ILO          |      | 1       | uA   |

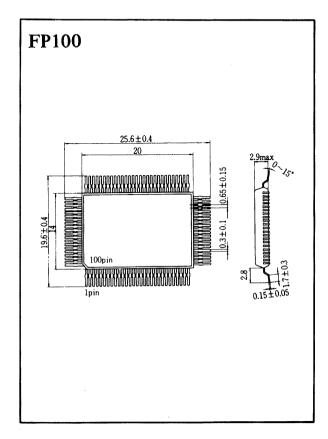

## 4.4 MECHANICAL INFORMATION

Fig 4.2 Gate Array C1

## **CHAPTER 5**

# TROUBLE - SHOOTING GUIDE

## CHAPTER 5 TROUBLE-SHOOTING GUIDE

This chapter describes the general guidelines for trouble-shooting of the Multi-I/O Card.

For more detail information on logic states please refer to the Gate Array C1 Specification in Chapter 4, data sheets of various components and the circuit schematic diagrams in the Appendix.

Technical reference manual of the host main unit will also be of help.

Refer to your DOS (Disk Operating System) User's Manual for errors associated with disk I/O.

The description contained in this chapter assumes that the problem comes from, or most likely from, the Multi-I/O Card. This can easily be verified by removing the card from the system, exchange for another I/O Card, or move the suspected Multi-I/O Card to another system and observe the result. Remember to turn power OFF before removing any card.

#### 5.1 GENERAL FAILURE

#### Symptom

Computer system no response after power up. Power indicator on main unit does not light up.

#### Possible causes

+5V failure/ short circuited on Multi-I/O Card.

#### Solution

Check for +5V DC short-circuiting on Multi-I/O Card

- Check for short-circuited decoupling capacitor.

- Check for short-circuited I.C. chips.

- Check if the card is inserted properly in the main unit slot.

#### Symptom

Main unit power indicator lights up. Computer no video, or no other response, including the power up 'beep' sound.

#### Possible causes

- Solution

- . System address bus, data bus, or control lines contamination due to Multi-I/O Card failure.

Multi-I/O Card not inserted properly.

- Check data buffer and address buffer I.C. U1,U6,U12 on Multi-I/O Card.

- Check if the card is inserted properly in the slot.

### 5.2 FLOPPY DISK INTERFACE/TRANSCOPY FAILURE

#### <u>Symptom</u>

Floppy drive not booting.

#### Possible causes

- . Floppy drive function disabled (on newer versions of this card).

- I/O Address conflict with another floppy drive adapter on the main unit.

- Data bus contamination on all I/O functions.

- Floppy drive interface logic failure.

- Floppy drive interface cable not properly connected.

#### **Solution**

- Change jumper block setting to enable this function.

- Change jumper block setting to disable this function, while use the built-in adapter on the main unit.

- Check I/O data bus buffer U1.

- Check all other LSI, I.C. connected to the I/O data bus.

- Check Gate Array C1 (U20).

- Check FDC chip uPD765 (U27), U21,U25,U26, U30,U28,U29,U14,U30, R19,R20,R21,R22,Xtal 2.

Check cables and connectors for proper connection and correct orientation. Floppy disk drive failure.

Check for proper jumper (if any) settings on floppy disk drive.

Check power (DC +5V, +12V) on floppy disk drive.

Check for proper DIP switch settings on main unit.

DIP switch on main unit set wrongly, which indicates no floppy disk drive.

## Symptom

Floppy drive boot up normal. Unable to format or write data to drive, or fail to retrieve the data written by the same computer.

Possible causes

Floppy drive failure.

- Floppy drive interface write logic failure.

- . Floppy write data Precompensation failure.

- . Floppy drive signal cable broken.

- Diskette defective or improper media quality.

<u>Solution</u>

Check floppy drive.

- Check Gate Array C1 (U28), uPD765 (U27), U29.

- Check Gate Array C1 (U28), uPD765 (U27).

- Check for proper connecting cable between card and disk drive.

- Check diskette for double-sided, doubledensity and it is not defective.

## **Symptom**

Transcopy function not working. Floppy disk function normal.

## Possible causes

- . Transcopy function not enabled.

- . Address conflict with other I/O devices on the system slot.

- Transcopy logic failure.

•

- . Check jumper block for proper setting.

- . Check for I/O devices attached to system slot. Select another I/O address for Transcopy in case of conflict.

- . Replace Gate Array C1 (U20).

## 5.3 PARALLEL PRINTER PORT FAILURE

## Symptom

Printer Port not functioning properly.

## Possible causes

- Printer cable and connectors not properly connected.

- . Printer port not enabled (on newer versions of the card)

- . Operating System is assumming another parallel port, with different address, on another peripheral card.

- Printer port logic failure.

- Printer interrupt failure.

- . Check for proper connection between the card and printer.

- . Change jumper block setting to enable function.

- . Check for another parallel port in the system. Use the other port for printer if higher priority is given to that port.

- Check Gate Array C1 (U20), U2,U8,U3,U7.

- Check printer port interrupt logic in Gate Array C1 (U20), U9.

## 5.4 RS232C SERIAL INTERFACE PORT FAILURE

## Symptom

RS232C Serial Interface Ports not functioning properly.

## Possible causes

- Serial cables and connectors not connected properly.

- Serial Ports not enabled (on newer versions of the card).

- Only one serial port is built-in on some cards.

- Improper serial cable used for serial printer (different from modem cables).

- Serial port hardware logic failure.

- Check for proper connection between card and bracket, between connectors and serial device.

- Change jumper block settings to enable the function.

- Expand to two serial ports. Refer to user's manual.

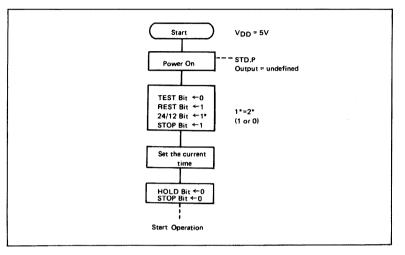

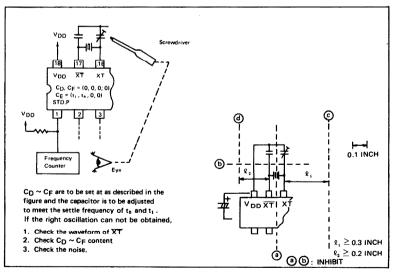

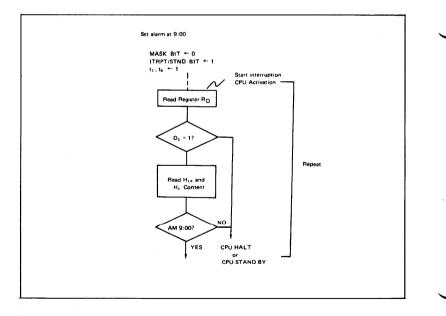

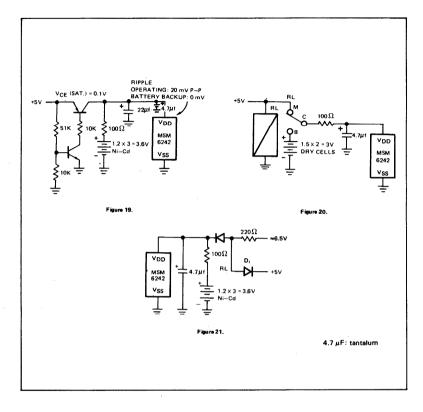

- Check if the proper serial printer cable is used.