# DISK 1<sup>TM</sup> TECHNICAL MANUAL

IEEE 696 / S-100

# ARBITRATED 24 BIT DMA FLOPPY DISK CONTROLLER

GOOBOUT COMPANY

DISK 1 TECHNICAL MANUAL Copyright ©1981 CompuPro Oakland Airport, CA 94614

First Printing: July 1981

Second Printing: January 1982

Third Printing: May 1982

Forth Printing: March 1983

Contents of this document were proofread with the aid of SpellGuard  $^{TM}$  a product from SORCIM Inc. Santa Clara, CA.

DISCLAIMER - CompuPro makes no representations or warranties with respect to the contents hereof and specifically disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, CompuPro reserves the right to revise this publication and to make any changes from time to time in the content hereof without obligation of CompuPro to notify any person of such revision or changes.

CompuPro is a registered trademark and Diskl is a trademark. Tri-State is a trademark of National Semiconductor Corp.

"SINGLE/DOUBLE DENSITY FLOPPY DISK CONTROLLER" January 1980, pages 1-16, Copyright 1980, Intel Corporation. Reprinted by permission of Intel Corporation.

All rights reserved. No part of this publication may be reproducted or transmitted in any form, or by any means, without the written permission of CompuPro.

Printed and assembled in the United States of America.

# TABLE OF CONTENTS

| WARNING 1                                            | 4<br>4<br>5<br>5               |

|------------------------------------------------------|--------------------------------|

| WITHOUT READING THE MANUAL                           | 5<br>6<br>11<br>12<br>12<br>13 |

| HARDWARE SECTION  Disk interface port map            | 15<br>15<br>16<br>16           |

| Port addressing                                      | 16<br>17<br>17<br>17           |

| Boot routine short description                       | 18<br>18<br>18<br>19           |

| Motor control enable                                 | 19<br>19<br>20<br>21           |

| Bus interface & boot circuitry                       | 21<br>22<br>22<br>23           |

| INIEL - Single/double density lioppy disk conditions | 24<br>25<br>5-30<br>1-46       |

| Parts list                                           | 7-51<br>52<br>53               |

| SOFTWARE SECTION Introduction                        | 55<br>55<br>56<br>68<br>62     |

| Software internal design                             | 65<br>69<br>72<br>74           |

| SOURCE LISTINGS Cbios                                | 77<br>120<br>126               |

| CUSTOMER SERVICE INFORMATION/LIMITED WARRANTY        | 132                            |

# >>>> WARNING <-

Not all floppy disk controllers generate true IBM compatible 3740 and SYSTEM 34 formats. Therefore, we strongly recommend that you do not use the DISK 1 to copy data onto a diskette that has been formatted by another controller! The proper procedure is to format new diskettes using the DISK 1, and copy the contents of other diskettes onto the newly formatted diskettes. (SOFTWARE SECTION; Software User's Guide)

The technical reason for this problem arises from the fact that almost all versions of the 1791 type floppy controller insert a byte of 00s immediately following the header CRC bytes. This byte of 00s is not specified in either IBM standard, and may confuse the 8272/765 controller on the DISK 1.

If your controller generates a true IBM type format, or you are using diskettes formatted by IBM, you will not experience this problem.

#### ATTENTION PURCHASERS OF CP/M-80

If purchasing CP/M-80 with your DISK 1 controller, you will receive a diskette that contains your serialized version of CP/M-80 (for a 32K system) along with several support utilities and special BIOS files. This diskette should be used to create a working copy only, and not altered in any way. The following procedure should be strictly followed.

- (1) Read the Software User's Guide in the SOFTWARE SECTION.

- (2) Boot your system using the provided diskette.

- (3) Run the FORMAT program and create a scratch diskette with a format identical to the format of your master diskette. (Your master will indicate its format on the label, i.e., 2D-256 = 256 byte format, 2D-1024 = 1024 byte format, etc.

- (4) Run the COPY program and create a duplicate of your entire (system and data tracks) master diskette. (see NOTE (2) below)

- (5) Remove your master diskette and store it in a safe place. Do not use this diskette again unless you damage your working copies. There will be a \$35 charge for recreating your master diskette if you damage or alter it.

- (6) Use your new working copy for all alterations that are made to your system.

NOTE (1): On your copy of CP/M you will receive two versions of the CompuPro BIOS. One version may be altered and reassembled using the CP/M supplied assembler (ASM), and another version must be reassembled and linked under the ACT assembler from SORCIM. The hex code from these files is identical, however, ASM will not assemble the files written for ACT.

NOTE (2): If you wish to change the density of your working disk or go from single sided to double sided, you must use SYSGEN to create the system, and PIP to transfer the data files. The COPY utility will only copy diskettes of identical formats.

#### **ABOUT DISK 1**

Congratulations on your decision to purchase the DISK I floppy disk controller. DISK I has been designed to be the highest performance floppy disk interface available that fully complies with with the IEEE 696/S-100 bus standard. Due to its provision for ready expansion and modification as the state of the computing art improves, the S-100 bus is the professional level choice for commercial, industrial, and scientific applications. We believe that this board, along with the rest of the S-100 portion of the CompuPro family, is one of the best boards available for that bus.

Features such as fully arbitrated DMA data transfer with 24 bits of addressing, 3rd generation LSI floppy disk controller, on-board phantom BOOT EPROM, I/O mapping for uninterrupted memory space, and a startup serial port make the DISK 1 another proud member of the CompuPro family.

#### TECHNICAL OVERVIEW

The DISK 1 was specifically designed to give the user one of the most powerful floppy disk interfaces available for the S-100 bus. Designed for full electrical and mechanical compatibility with the IEEE 696/S-100 bus standard, this board boasts several innovative features not found on currently available disk controllers. These features include 24 bit DMA data transfers with the ability to cross 64K boundaries, an advanced, 3rd generation floppy disk controller made by NEC or INTEL (765A or 8272), priority arbitration for the onboard DMA circuitry that will allow up to 16 temporary bus masters without conflict, an on-board BOOT EPROM with the capability of supporting eight different processors or BOOT routines, and a start-up serial port for ease of system initialization.

Other features standard to all CompuPro boards include thorough bypassing of all supply lines to suppress transients, on-board regulators, and low power Schottky TTL and MOS technology integrated circuits for reliable, cool operation. All this and sockets for all IC's go onto a double sided, solder masked printed circuit board with a complete component legend.

# HOW TO GET YOUR DISK 1 UP AND RUNNING WITHOUT READING THE MANUAL

This section is for the user who is so anxious to see the DISK I running that he doesn't want to read the manual. This section will tell you how to set up the DISK I board as well as many other CompuPro boards so that it can run CP/M-80 or CP/M-86 in your system with either the on-board serial channel or any other supported serial channel.

We strongly recommend that you relax and read the manual. If, after reading and following the directions in this section, your system does not work, don't panic! Read the manual!

#### SYSTEM CONFIGURATIONS USING COMPUPRO HARDWARE

The following guide will help the user to configure CompuPro hardware for operation with CP/M type operating systems. This list covers boards in production at the date of printing, and if your particular CompuPro board is not listed, consult the individual manual. For the configuration of CompuPro hardware for the OASIS operating systems, refer to the configuration guide supplied by Phase One.

The following list will describe the proper switch settings and jumper options required by each CompuPro board when run with the DISK 1 controller.

**DISK**  $\underline{1}$  - The standard switch settings for running CP/M are as follows:

| "OFF" | S1 | "ON" | "OFF" | S 2 | "ON" |

|-------|----|------|-------|-----|------|

|       | 1  | >    | *     | 1   | *    |

| <     | 2  |      | *     | 2   | *    |

| <     | 3  |      | <     | 3   |      |

| <     | 4  |      | <     | 4   |      |

| <     | 5  |      |       | 5   | >    |

| <     | 6  |      |       | 6   | >    |

| <     | 7  |      |       | 7   | >    |

| <     | 8  |      |       | 8   | >    |

J16 = Short B-C

S2 POSITION

J17 = Short A-C for CPU-Z or CPU 8085/88

J17 = Short B-C for CPU 8086/87

| 1     | 2             |                                                                                                                     |

|-------|---------------|---------------------------------------------------------------------------------------------------------------------|

| 011   | "ON"<br>"OFF" | INTERFACER 1 or 2; Console at OOH, LPT List at O2H DISK 1 serial port as Console - CP/M-80 ONLY!!!                  |

| "OFF" | 011           | SYSTEM SUPPORT 1 at 50H; Console 9600 baud, List as above INTERFACER 3 or 4; 9600 baud, Console user 7, List user 6 |

I/O BOARD SUPPORTED UNDER CP/M-80 AND CP/M-86

These settings select DMA arbiter priority 15, port COH-C3H, wait states enabled, and the BOOT routine as selected.

CPU-Z - The standard switch settings for running the CPU-Z with DISK 1 are:

| "OFF" | Sl | "ON" | "OFF" | <b>S</b> 2 | "ON" | "OFF" | <b>S</b> 3 | "ON" |

|-------|----|------|-------|------------|------|-------|------------|------|

| <     | 1  |      | <     | 1          |      | <     | 1          |      |

| <     | 2  |      | <     | 2          |      | <     | 2          |      |

| <     | 3  |      | <     | 3          |      | <     | 3          |      |

| <     | 4  |      | <     | 4          |      | <     | 4          |      |

| <     | 5  |      | <     | 5          |      |       | 5          | >    |

| <     | 6  |      | <     | 6          |      | <     | 6          |      |

| <     | 7  |      | <     | 7          |      | <     | 7          |      |

| <     | 8  |      | <     | 8          |      | <     | 8          |      |

This assumes that you are not planning to run at the slow CPU-Z speed and that you do not require wait states generated on the CPU.

CPU 8085/88 - The standard switch settings for running the CPU 8085/88 with DISK 1 are:

| "OFF" | Sl | "ON" | "OFF" | S2 | "ON" | "OFF" | s3 | "ON" |

|-------|----|------|-------|----|------|-------|----|------|

|       | 1  | >    | <     | 1  |      | <     | 1  |      |

|       | 2  | >    | <     | 2  |      |       | 2  | >    |

|       | 3  | >    | <     | 3  |      | <     | 3  |      |

| <     | 4  |      | <     | 4  |      | <     | 4  |      |

| <     | 5  |      | <     | 5  |      | <     | 5  |      |

| <     | 6  |      | <     | 6  |      | <     | 6  |      |

| *     | 7  | *    | <     | 7  |      | <     | 7  |      |

| <     | 8  |      | <     | 8  |      | <     | 8  |      |

Switch S4 should be set to the desired speed. Switch S1-7 should be "OFF" in systems having a front panel and "ON" in systems without a front panel. A wait state is inserted in all I/O cycles.

CPU 86/87 - The standard switch settings for running the CPU 86/87 with DISK 1 are:

| "OFF" | Sl | "ON" | "OFF" | S 2 | "ON" | "OFF" | <b>S</b> 3 | "ON" | "OFF" | S4 | "ON" | "OFF" | S5 ' | "ON" |

|-------|----|------|-------|-----|------|-------|------------|------|-------|----|------|-------|------|------|

| <     | 1  |      | <     | 1   |      | <     | 1          |      | <     | 1  |      | <     | 1    |      |

| <     | 2  |      | <     | 2   |      | <     | 2          |      | <     | 2  |      | <     | 2    |      |

| <     | 3  |      | <     | 3   |      |       | 3          | >    |       | 3  | >    | <     | 3    |      |

| <     | 4  |      | <     | 4   |      |       | 4          | >    |       | 4  | >    | <     | 4    |      |

| <     | 5  |      | <     | 5   |      | <     | 5          |      |       | 5  | >    | <     | 5    |      |

| <     | 6  |      | <     | 6   |      | <     | 6          |      |       | 6  | >    | <     | 6    |      |

| <     | 7  |      | <     | 7   |      |       | 7          | >    |       | 7  | >    | <     | 7    |      |

| <     | 8  |      | <     | 8   |      | <     | 8          |      |       | 8  | >    | <     | 8    |      |

| <     | 9  |      | <     | 9   |      |       |            |      |       | 9  | >    | <     | 9    |      |

| < '   | 10 |      | <     | 10  |      |       |            |      |       | 10 | >    | <     | 10   |      |

JUMPERS: Make sure there is a shorting plug installed at jumper location J8. J8 is located near the top left-hand corner of the board. There should be no shorting plugs installed at jumper locations J0 thru J7, which are located near the bottom left-hand corner of the board.

INTERFACER  $\frac{1}{1}$  - The standard switch settings for running the INTERFACER 1 as the console and  $\frac{1}{1}$  ist device I/O board with DISK 1 are:

| "OFF" | S1 | "ON" | "OFF" | S2 | "ON" | "OFF" | s3 | "ON" |

|-------|----|------|-------|----|------|-------|----|------|

|       | 1  | >    |       | 1  | >    | <     | 1  |      |

| <     | 2  |      |       | 2  | >    |       | 2  | >    |

| <     | 3  |      |       | 3  | >    |       | 3  | >    |

| <     | 4  |      |       | 4  | >    |       | 4  | >    |

|       | 5  | >    |       | 5  | >    |       | 5  | >    |

| <     | 6  |      |       | 6  | >    |       | 6  | >    |

| <     | 7  |      |       | 7  | >    |       | 7  | >    |

| <     | 8  |      | (     | 8  |      | (     | 8  |      |

This configuration provides the Console device on channel "A" (ports 00H and 01H) at 9600 baud and the List device on channel "B" (ports 02H and 03H) at 9600 baud.

- 1. Jumpers J3 through J6 should be set in Slave mode.

- 2. We recommend that Jumpers J7 and J8 be set to match your terminal

and printer specifications and that Jumpers J9 and J10 have traces 2-15, 4-13, 6-11, and 8-9 cut.

3. Baud rates may be altered if desired by resetting Sl.

INTERFACER 2 - The standard switch settings for running the serial section of the INTERFACER 2 as the console device I/O board with DISK 1 are as follows. The list device is assumed to be another INTERFACER 1/2 serial port at locations 02H and 03H.

| "OFF" | S2 | "ON" | "OFF" | $s_3$ | "ON" | "OFF" | S4 | "ON" |

|-------|----|------|-------|-------|------|-------|----|------|

|       | 1  | >    |       | 1     | >    |       | 1  | >    |

| <     | 2  |      |       | 2     | >    |       | 2  | >    |

| <     | 3  |      |       | 3     | >    | <     | 3  |      |

| ζ.    | 4  |      |       | 4     | >    |       | 4  | >    |

| <     | 5  |      |       | 5     | >    |       | 5  | >    |

| ż     | 6  |      |       | 6     | >    |       | 6  | >    |

| <     | 7  |      |       | 7     | >    |       | 7  | >    |

| · 〈   | 8  |      | <     | 8     |      | <     | 8  |      |

This configuration provides the Console device on the serial channel (ports 00H and 01H) at 9600 baud and the List device on another INTERFACER I or 2 channel.

- 1. Jumpers J5 and J6 should be set in Slave mode.

- 2. We recommend that you set J9 to match your terminal specifications and that Jumper J10 have traces 2-15, 4-13, 6-11, and 8-9 cut.

- 3. Baud rate may be altered if desired by resetting S2.

- 4. The setting of S1 is dependent on your parallel requirements and does not affect the setting of the serial channel.

- 5. The address chosen for the parallel ports is the CompuPro standard of 08H through 0BH so that it does not overlap the serial port.

INTERFACER 3 - The standard switch settings for running the INTERFACER 3 as the console and list device I/O board with DISK 1 are:

| OFF" | S1 | "ON" |

|------|----|------|

| <    | 1  |      |

|      | 2  | >    |

|      | 3  | >    |

|      | 4  | >    |

| <    | 5  |      |

|      | 6  | >    |

|      | 7  | >    |

|      | 8  | >    |

|      |    |      |

This configuration provides the Console device on User 7 (left most) at 9600 baud and the List device on User 6 (2nd from left) at 9600 baud.

- 1. Jumpers Jl and J2 should be set in Slave mode.

- 2. We recommend that Jumpers J3 through J14 be removed.

- 3. Jumpers J15 and J16 may remain unwired.

- 4. Jumper J17 should be set for an appropriate number of wait states for your system speed.

- 5. USART assumes 8 data bits, 2 stop bits, no parity, asynch operation, RTS and DTR output in "spacing" (+12V) condition.

6. USART requires that CTS and DSR\* be "spacing" (+12V). \*(DSR is used to determine if printer is ready on User 6 only)

INTERFACER  $\frac{4}{1}$  - The standard switch settings for running the INTERFACER 4 as the console and  $\frac{1}{1}$  ist device I/O board with DISK 1 are:

| "OFF" | Sl | "ON" | "OFF" | <b>S2</b> | "ON" | "OFF" | <b>S</b> 3 | "ON" |

|-------|----|------|-------|-----------|------|-------|------------|------|

| <     | 1  |      |       | 1         | >    |       | 1          | >    |

| <     | 2  |      |       | 2         | >    |       | 2          | >    |

| <     | 3  |      | <     | 3         |      |       | 3          | >    |

| <     | 4  |      | <     | 4         |      |       | 4          | >    |

| <     | 5  |      |       | 5         | >    | <     | 5          |      |

| <     | 6  |      |       | 6         | >    | <     | 6          |      |

| <     | 7  |      |       | 7         | >    | <     | 7          |      |

| <     | 8  |      | <     | 8         |      | <     | 8          |      |

| <     | 9  |      |       | 9         | >    |       |            |      |

| <     | 10 |      | <     | 10        |      |       |            |      |

This configuration provides the Console device on User 7 (left most serial port-CONN3-A) at 9600 baud, the List device on User 6 (middle serial port-CONN3-B at 9600 baud or the CENTRONICS PARALLEL Channel-CONN 2 / SEE ITEM #3 BELOW), and the ULl device on User 5 (right most serial channel).

- Jumper Sockets JS1-JS3 should contain 8 position DIP SHUNTS (Slave mode for terminals or printers).

- 2. Jumper J6, J7, or J8 should be installed for 1, 2, or 3 wait states.

- For a serial list device, use CONN3-B with jumper J26 having "A" shorted to "B", and "C" shorted to "D".

For a parallel list device using the CENTRONICS PARALLEL Channel, use CONN2 with jumper J26 having "A" shorted to "C", and "B" shorted to "D"

For an EPSON type printer, install J2-bottom, J3-top, and J4-bottom.

- 4. All other Jumpers may be removed.

- 5. USART assumes 8 data bits, 2 stop bits, no parity, asynch operation, RTS and DTR output in "spacing" (+12V) condition.

- 6. USART requires that CTS and DSR\* be "spacing" (+12V). \*(DSR is used to determine if printer is ready on User 6 only)

SYSTEM SUPPORT 1 - The standard switch settings for running the SYSTEM SUPPORT 1 as the console device I/O board with DISK 1 are:

| "OFF" | S1 | "ON" | "OFF" | <b>S2</b> | "ON" | "OFF" | S3 | "ON" |

|-------|----|------|-------|-----------|------|-------|----|------|

| <     | 1  |      |       | 1         | >    | <     | 1  | 011  |

| <     | 2  |      |       | 2         | >    | <     | 2  |      |

| <     | 3  |      |       | 3         | >    | <     | 3  |      |

|       | 4  | >    |       | 4         | >    | <     | 4  |      |

| <     | 5  |      | <     | 5         |      |       | 5  | >    |

| <     | 6  |      | <     | 6         |      | <     | 6  |      |

|       | 7  | >    | <     | 7         |      |       | 7  | >    |

| <     | 8  |      | <     | 8         |      | <     | 8  |      |

This configuration provides the Console device on the SYSTEM SUPPORT 1 serial channel at 9600 baud and the List device as an INTERFACER 1/2 serial channel at ports 02H and 03H.

- USART assumes 8 data bits, 2 stop bits, no parity, RTS and DTR output in "spacing" (+12V) condition. USART requires that CTS be "spacing" (+12V).

- 2. J2 and J8 should be bussed straight across with a shunt.

- For CP/M-86, either a 6116 RAM chip or a GO86 JUMP EPROM should be installed in Ul6. The above settings place it at OFF000H for the 8086/88.

RAM 16 - The standard switch settings for operating a RAM 16 as the first 64K of system memory with the DISK 1, this setting places 64K in extended page 0 (base page), are:

| "OFF" | Sl | "ON" |

|-------|----|------|

|       | 1  | >    |

|       | 2  | >    |

|       | 3  | >    |

|       | 4  | >    |

|       | 5  | >    |

|       | 6  | >    |

|       | 7  | >    |

|       | 8  | >    |

RAM 17 - The standard switch settings for operating a RAM 17 as the first 64K of system memory with the DISK 1 are:

| "OFF" | s1 | "ON" | "OFF" | S2 | "ON" |

|-------|----|------|-------|----|------|

| *     | 1  | *    | <     | 1  |      |

|       | 2  | >    |       | 2  | >    |

|       | 3  | >    |       | 3  | >    |

|       | 4  | >    |       | 4  | >    |

|       | 5  | >    |       | 5  | >    |

|       | 6  | >    |       | 6  | >    |

|       | 7  | >    |       | 7  | >    |

|       | 8  | >    |       | 8  | >    |

|       | 9  | >    |       | 9  | >    |

| *     | 10 | *    |       | 10 | >    |

In systems with front panels, S1-1 should be "ON" and S1-10 should be "OFF". In systems without front panels, S1-1 should be "OFF" and S1-10 should be "ON". This setting places all 64K active and resident in extended page 0 (base page).

**RAM 20** - The standard switch settings for operating two RAM 20 boards as the first 64K of system memory with the DISK 1 are:

| "OFF" | s1 | "ON" | "OFF" | S2 | "ON" | "OFF" | $s_3$ | "ON" | "OFF" | 84 | "ON" |

|-------|----|------|-------|----|------|-------|-------|------|-------|----|------|

|       | 1  | >    | <     | 1  |      |       | 1     | >    | <     | 1  |      |

|       | 2  | >    | <     | 2  |      |       | 2     | >    | <     | 2  |      |

|       | 3  | >    | <     | 3  |      |       | 3     | >    | <     | 3  |      |

|       | 4  | >    | *     | 4  | *    |       | 4     | >    | <     | 4  |      |

|       | 5  | >    | <     | 5  |      |       | 5     | >    | <     | 5  |      |

|       | 6  | >    |       | 6  | >    |       | 6     | >    | <     | 6  |      |

|       | 7  | >    | <     | 7  |      |       | 7     | >    | <     | 7  |      |

|       | 8  | >    | <     | 8  |      |       | 8     | >    | <     | 8  |      |

To set the first RAM 20 (0-32K) should have S2-4 in the "OFF" position and the second RAM 20 should have S2-4 in the "ON" position. The two boards will form 64K (all active and resident) in extended page 0 (base page).

#### RAM 21

The standard switch settings for operating a RAM 21 as the first 128K of system memory with the DISK 1, this setting places 64K in extended page 0 (base page), and 64K in extended page 1, are as follows:

| "OFF" | S1 | "ON" |

|-------|----|------|

|       | 1  | >    |

|       | 2  | >    |

|       | 3  | >    |

|       | 4  | >    |

|       | 5  | >    |

|       | 6  | >    |

|       | 7  | >    |

|       | 8  | >    |

#### DRIVE INTERFACE - 8 INCH DRIVES

The interface to soft media 8" drives is standard except that the stepper motors must be enabled at all times (not tied to drive select or head load). This causes the steppers to be powered at all times (they will get warm), and allows stepping without the lamp on the front of the drive being "ON" (so be careful). In addition, the head load signal should not be tied to drive select since the 765A/8272 is always scanning the drives (this would result in a buzz). Standard 50 pin ribbon cable should be used to connect the drives to the controller, and the last drive in the line should be terminated as specified in the drive manual.

NOTE: Due to the steppers being enabled at all times, your disk power supply must be able to handle full load on the +24V line all the time and your drive box must have adequate cooling.

SHUGART 800/801: On a Shugart 800/801 drive, the shorting plugs should be installed and removed on all drives as shown on the following example:

```

INSTALLED ( T2, A, B, C, Z, 800 )

REMOVED ( D, DC, X, Y, HL, DS )

```

Drive select (DSx) should be installed appropriately and the terminators Tl, and T3-T6 should be installed on the last drive of the cable.

SHUGART 850/851: On a Shugart 850/851 drive, the shorting plugs should be installed and removed as shown below, and the DIP shunt should be altered as required. NOTE: SHUGART changes the drive P.C. board on the 850/851 regularly, so this information is for the MLC 12 series and may be dated.

```

INSTALLED (C,2S,S2,IW,RS,DL,IT,AF,M,850)

REMOVED (FS,TS,Y,DS,HLL,HI,D,DC,NF)

```

SHUNT: CUT HL AND X, ALL OTHERS INTACT. TERMINATOR RESISTORS SHOULD BE INSTALLED ON THE LAST DRIVE OF THE CABLE.

QUME DATA TRACK 8: On Qume Data Track 8 drives, the shorting plugs should be installed and removed as shown below, and the DIP shunt should be altered as required.

INSTALLED (C,2S,DL,DSx)

REMOVED (T40,GND,DS,D,DC,Y,HA)

SHUNT: CUT HL AND X, ALL OTHERS INTACT. TERMINATOR RESISTORS SHOULD BE INSTALLED ON THE LAST DRIVE OF THE CABLE.

SIEMENS MODEL FDD 100-8: On Siemens Model D drives, the shorting plugs should be installed and removed as shown below.

INSTALLED (SS,SE,E,D,RR,0,2,F,RI,L,U,H)

REMOVED (HS,8,16,32,1,TE,A,V,B,J,K,M,G)

PC BOARD MODIFICATION FOR RUNNING TWO OR MORE DRIVES: This modification involves the raw read data on pin 46 and the step inhibit signal on IC 6C (7438).

- 1. Remove the P.C. board and cut the trace leading to IC 6C pin 9.

- 2. Connect IC 6C pin 9 to IC 6C pin 12 and re-install the P.C. board.

TANDON MODEL 848 On a TANDON 848 drive, the drive will run as shipped except for the alteration of the shunt and the installation of the drive select plug. The following connections should be observed.

INSTALLED (DC,2S,S2,C,RR,RI,WP)

REMOVED (Y,DS,DL,HLL,D,NP,RM,S1)

SHUNT: CUT HL AND X (5 AND 2 OF U3), ALL OTHERS INTACT. TERMINATOR RESISTORS SHOULD BE INSTALLED ON THE LAST DRIVE OF THE CABLE.

MITSUBISHI MODEL M2894-63 On a MITSUBISHI M2894 drive, the shorting plugs should be installed and removed as shown below, and the DIP shunt (PJ1-8) should be altered as required.

INSTALLED (E,Z,2S,I,R,S2,IW,C,WP)

REMOVED (A,F,Y,DC,IT,S3)

SHUNT: OPEN PJ4 AND PJ5, ALL OTHERS CLOSED. TERMINATOR RESISTORS SHOULD BE INSTALLED ON THE LAST DRIVE OF THE CABLE.

#### 5.25 INCH DRIVES

Connection to 5.25" minifloppies requires that the DISK 1 board be modified as per the instructions entitled "MODIFICATIONS FOR MINIFLOPPIES" prior to the

following drive connections. Standard 34 pin ribbon cable should be used. However, the female transition connector must be offset to the extreme right when seated in connector J10. The serial port may be used as the motor "ON-OFF" control bit if switch S1-3 is placed in the "ON" position.

No modifications need to be made to minifloppy drives except to select the proper drive select line on the programming shunt and leave it intact. If your minifloppy drive does not drive the READY\* line, a jumper must be installed between "C" and "B" of J15. If it does drive the ready line, a jumper must be installed between "C" and "A" of J15. Jumpers J11-J13 should be set for 5.25" operation and J14 should be installed.

#### TRYING TO BOOT THE CONTROLLER

Before inserting your diskette, you should see the following things:

- (1) Your drive activity light should be glowing very dimly to indicate that the floppy controller is scanning the drives.

- (2) If the controller is trying to boot, you will see the activity light of drive #1 flashing on and off approximately once a second (dependent on the CPU speed).

If both of these are present, insert your write protected diskette and listen. If using an I/O port other than the on-board serial port, you should hear several (approx. four) clicking sounds from the drive and see the sign-on message. If using the on-board serial port you should hear one click, and after striking the "U" on the terminal, you should hear the four clicks and see the sign-on message.

#### TROUBLESHOOTING

If you are having problems getting your DISK 1 up and running and you have read the previous sections of this manual completely, read on. The following section may help you solve your problem.

PROBLEM: ONE OR MORE OF YOUR DRIVE ACTIVITY LIGHTS STAYS "ON" BRIGHT ALL THE TIME.

Solution: This almost always indicates that the drive cable is backwards at either the drive box connector or at the drive. This may be verified by removing the 50 pin cable from either the board or the box. If the lamp goes off, the cable is reversed. NOTE: When using our controller with drives from Morrow Designs, the cable must be reversed due to their non-standard connector pinouts.

#### PROBLEM: ACTIVITY LAMPS DO NOT GLOW DIMLY OR FLASH BRIGHT

Solution: This generally indicates that the drive is jumpered wrong or there is a controller fault. Make sure that the drives are jumpered correctly and that the activity lamp is activated by drive select and not head load. Make sure that the drive has all of the different DC voltages that it requires. If the

lamp still does not light, there could be a problem in either the controller or an open in the 50 pin drive cable.

#### PROBLEM: ACTIVITY LAMP GLOWS DIMLY BUT DOES NOT FLASH

Solution: This typically indicates either that the CPU is not executing the code in the BOOT EPROM due to the memory not being phantomed OFF, or that the host CPU does not have its jump-on-reset circuit turned off. The lamp will flash even if there is nothing in the system but the CPU and the DISK l board (no RAM!). Try removing everything but the CPU and the DISK l and verifying that the lamp flashes. If it does not, either of these boards could be at fault. Review your switch settings.

#### PROBLEM: DRIVE LOADS HEAD THEN UNLOADS AND REPEATS

Solution: If the board clicks and then pauses, and then repeats itself, this is typically an indication that the controller is unable to read the data from the drive. This could be from the data on the diskette being bad, the phase lock loop being out of adjustment, the DMA cycle being inhibited by the CPU, or a hardware problem on either the drive, the cable, or the DISK 1 board. Try to isolate the problem by substitution if possible, otherwise check switch settings and drive hardware for proper configuration. CAUTION: Controller calibration should only be performed by an authorized dealer, OEM or the factory.

#### PROBLEM: DRIVE LOADS HEAD ONCE THEN STOPS

Solution: A single loading of the head and then nothing generally indicates that the controller is reading the first several sectors OK but either the data is transferred into memory improperly or the system memory is either bad or misaddressed. Improper transfer into memory generally occurs only with dynamic RAM boards that reley on specific CPU timing. If you have dynamic memory, make sure that is can handle DMA and that it generates its own refresh timing. Otherwise make sure that the RAM is addressed properly and in the proper extended page (page 0). Remember that for CP/M-80 you only need 32K and for CP/M-86 you need 64K. If you can run a RAM test, verify that that your memory is OK.

# PROBLEM: IMSAI FRONT PANEL "LOCKS UP" WHEN DISK 1 IS INSTALLED

Solution: The new IEEE 696/S-100 bus standard calls for lines 20 and 70 to be grounded on the bus. When the IMSAI front panel was designed, many memory boards had the capability to be "protected" from accidental writes to the board. To accommodate these boards, the IMSAI front panel grounded line 70 but pulled up line 20 with a resistor that also enabled all the front panel functions. When DISK 1 is inserted, line 20 is grounded and the front panel is disabled. The solution is to cut line 20 on the front panel since this line is now defined as ground. ADDITIONAL NOTE: To access system RAM from the front panel after reset or power-up without running the DISK 1, the BOOT INHIBIT switch (S1-4) must be set "ON" to disable the BOOT EPROM.

# HARDWARE SECTION

#### DISK INTERFACE PORT MAP

The DISK 1 interface uses a block of four port addresses for communication between it and the host processor. DISK 1 occupies no memory space of the host processor and performs all data transfers via DMA. The address of the first port is switch settable to any address which is a multiple of four. The ports will be referred to as relative ports 0-3.

RELATIVE

FUNCTION

0 . . . FDC main status register ( read only )

1 . . . FDC data register

2 . . . STATUS register ( when read )

D7 indicates FDC INT output is asserted. No other bits are significant.

DMA address register ( when written )

The DMA address register is actually a push- down stack of three one byte registers. A three byte, twenty-four bit DMA address should be loaded most significant byte first.

#### 3 . . . SERIAL PORT

When read, bit D7 will contain the current status of the serial input line.

When written, bit D7 should contain the new state for the serial output line. The state will be latched until changed.

When written with a "0" in bit DO, the BOOT EPROM will be disabled. A system reset is required to re-enable the BOOT EPROM.

- (1) Bit D7 = 1 indicates a SPACING condition or binary O. (A start bit is a space)

- (2) Bit D7 = 0 indicates a MARKING condition or a binary 1.

- (3) On RESET, the output will be cleared to the MARKING state.

If the SERIAL port is not required for RS232 communications, a switch will allow the output data latch to serve as MOTOR-ON for the 5.25 inch floppy disks.

## COMPUPRO 8 INCH DRIVE INTERFACE ADDRESS

The current implementation of all software packages written for the DISK 1 controller and 8 inch drives including the CompuPro BIOS for CP/M-80 and CP/M-86, as well as single and multi-user OASIS, requires that the base port address be set to COH.

# ACTUAL PORT FUNCTION

```

CO . . . . . FDC main status register ( read only )

Cl . . . . . FDC data register

C2 . . . . STATUS register ( when read )

DMA address register ( when written )

C3 . . . . SERIAL PORT

```

# COMPUPRO 5.25 INCH DRIVE INTERFACE ADDRESS

SWITCH POSITION

The recommended base port address for the DISK 1 controller and 5.25 inch drives is CCH.

| ACTUAL PORT | FUNCTION                                                                |

|-------------|-------------------------------------------------------------------------|

| cc          | <br>FDC main status register ( read only )                              |

| CD          | <br>FDC data register                                                   |

| CE          | <br>STATUS register ( when read ) DMA address register ( when written ) |

| CF          | <br>SERIAL PORT                                                         |

#### PORT ADDRESSING

DIP switch S2, positions 3 thru 8 are used to select the base address of the four port block in a binary fashion as shown below:

ADDRESS BIT

|  | 3 |  |  |  |  |  |  |  |  |  | A7  |                              |

|--|---|--|--|--|--|--|--|--|--|--|-----|------------------------------|

|  | 4 |  |  |  |  |  |  |  |  |  | A6  |                              |

|  | 5 |  |  |  |  |  |  |  |  |  | A5  | $^{11}ON_{11} = ^{11}O_{11}$ |

|  | 6 |  |  |  |  |  |  |  |  |  | A4  | "OFF" = "1"                  |

|  | 7 |  |  |  |  |  |  |  |  |  | A3  |                              |

|  | 8 |  |  |  |  |  |  |  |  |  | 4.2 |                              |

**EXAMPLE:** To address this board at addresses COH thru C3H for the CompuPro CP/M BIOS, positions 3 and 4 would be "OFF" and positions 5 thru 8 would be "ON". **EXAMPLE:** To address this board at addresses CCH thru CFH, positions 3, 4, 7 and 8 would be "OFF" and positions 5 and 6 would be "ON".

#### SERIAL PORT

The serial port on the DISK I was designed for initial system startup only and should not be used as the console device for longer than required to patch the BIOS. Since this port is controlled entirely by software, its baud rate limitations are dependent on the host processor's clock rate. With the current implementation of the BIOS, the speed of the terminal is calculated when an upper case "U" is struck on the keyboard, and the sign-on message is then displayed. The terminal may be set to any baud rate, but the following maximum baud rates should be observed for best reliability:

| CPU CLOCK SPEED | MAX. BAUD RATE |

|-----------------|----------------|

| 2MHz            | 600 baud       |

| 4MHz            | 1200 baud      |

| 6MHz            | 2400 baud      |

If your processor does not run at any of the above speeds, don't worry-these are only suggested maximum rates. Connector J9 accepts a standard INTER-FACER cable with ground on pin 7, transmit data on pin 3, and receive data on pin 2. No RS-232 handshaking lines are provided.

#### INTERRUPTS

The DISK 1 is capable of running in either a polled mode or an interrupt driven mode that is particularly suited for multi-user environments. The STATUS port (relative port 2) allows the user to run in the polled mode by sampling the interrupt output of the floppy disk controller on data bit 7. To run in an interrupt driven mode, the interrupt output of the floppy disk controller is driven onto one of the vectored interrupt lines (VIO\* thru VI7\*) or the INT\* line of the S-100 bus. This is accomplished by installing a shorting plug or a #30 wrap wire across the posts at jumper locations JO thru J7 or J8. Jumpers J0 thru J7 correspond directly to VIO\* thru VI7\*, and J8 is for INT\*. It is recommended that the highest priority vectored interrupt be used to insure that it is not accidentally masked off.

#### BOOT EPROM

The BOOT EPROM contains the software routines required to load the initial sectors of the disk operating system into memory for system startup. The exact contents of this routine is covered in the SOURCE LISTINGS section under ROM Boot.

Upon power-up, the BOOT EPROM will appear as 256 bytes of memory at the host CPU's reset address. If the CPU does not reset to a location on a 256 byte boundary, the BOOT EPROM will align itself on the nearest 256 byte page. For example, an 8085 or a Z-80 will reset to 0000H, which is on a 256 byte boundary. Therefore, in this case the BOOT EPROM will appear from 0000H to 00FFH. An 8088 or an 8086 resets to 0FFFFOH, which is not page aligned, therefore, the BOOT EPROM will appear from 0FFFOOH to 0FFFFFH.

The DISK 1 requires that a minimum of 256 bytes of system RAM at the same location as the BOOT EPROM be capable of responding to PHANTOM\* by disabling itself. This RAM may be of any amount greater than 256 bytes since the BOOT routine requires no memory for proper operation.

#### BOOT EPROM ROUTINE ADDRESSING

The BOOT EPROM is capable of holding two sets of four switch selectable BOOT routines of up to 256 bytes each. Positions 1 and 2 of switch S2 select one of the four routines in a binary fashion and jumper J17 selects either the low or high half of the EPROM as shown below:

| J17 POSITION | SWITCH S2 | POSITION 2 | EPROM STARTING<br>ADDRESS | BOOT<br>ROUTINE # |

|--------------|-----------|------------|---------------------------|-------------------|

| В            | ON        | ON         | 000н                      | 0                 |

| В            | ON        | OFF        | 100н                      | 1                 |

| В            | OFF       | ON         | 200н                      | 2                 |

| В            | OFF       | OFF        | 300Н                      | 3                 |

| Α            | ON        | ON         | 400Н                      | 4                 |

| A            | ON        | OFF        | 500н                      | 5                 |

| Α            | OFF       | ON         | 600Н                      | 6                 |

| A            | OFF       | OFF        | 700Н                      | 7                 |

NOTE: In some cases, the DISK 1 may be shipped set for routines 4-7 rather than 0-3. In these cases, please leave J17 as shipped and treat the routines as 0-3 only.

#### BOOT ROUTINE SHORT DESCRIPTION

As shipped, the BOOT EPROM contains routines for loading several sectors of track 0 into memory and passing on the value associated with the particular BOOT routine. The value passed on allows the proper console I/O routine to be selected as described in a following section. The specific details for passing this value is contained in the description of the CP/M-80 BIOS. The BIOS for CP/M-80 and CP/M-86 (for running under CPU 8085/88) as implemented interprets this value as shown below. Software designed CPU 68K will contain information describing which routine to use.

- #4 This BOOT routine specifies a standard INTERFACER 1 or 2 serial port at locations 00H and 01H for the console device and the LPT list device at locations 02H and 03H. (For CP/M-80 and CP/M-86)

- #5 This BOOT routine specifies the DISK 1 on-board serial port as the console device and the list device the same as routine #1. (For CP/M-80 only! CP/M-86 does not support the on-board serial port.)

- #6 This BOOT routine specifies the serial channel on the SYSTEM SUPPORT 1 board addressed at 50H and for 9600 baud as the console device and the list device the same as in routine #1. (For CP/M-80 and CP/M-86)

- #7 This BOOT routine specifies two serial channels on an INTERFACER 3 or 4 addressed at 10H and set for 9600 baud, with user 7 as the console and 6 as the list device. (For CP/M~80 and CP/M-86)

- #0 This routine is identical to #4 but for CPU 8086/87 only.

- #1 This routine is not used by CPU 8086/87.

- #2 This routine is identical to #6 but for CPU 8086/87 only.

- #3 This routine is identical to #7 but for CPU 8086/87 only.

#### WAIT STATE ENABLE

The DISK 1 is capable of inserting wait states into the BOOT EPROM read as well as the I/O and DMA read or write cycles when fast processors are being used. The wait states become necessary when the access time of the BOOT EPROM and the floppy disk controller are longer than the fetch time of the host processor. The wait states are enabled by placing position 1 of switch S1 in the "ON" position. When enabled, the EPROM will have 5 wait states inserted, and the I/O and DMA cycles can have either 2, 3 or 4 wait states. With J16 in position "A", 2 wait states will be inserted, with J16 in position "B", 3 wait states will be inserted, and with J16 removed, 4 wait states will be inserted.

#### BOOT ENABLE/INHIBIT

The BOOT EPROM may be disabled by putting position 4 of Sl in the "ON" position, and enabled by placing it in the "OFF" position. A possible reason for disabling the BOOT routine would be if two or more DISK l controllers were

placed in the system at one time or the DISK 2 hard disk controller was the BOOTING device. In this case, more than one controller trying to boot would cause a system conflict.

Remember, the BOOT hardware on the DISK 1 board requires that a 256 byte page of memory respond to PHANTOM\* at the host processor's reset address. If the memory residing at this address does not respond to PHANTOM\*, a bus drive conflict will occur and possible damage could result.

#### ARBITER AND PRIORITY SELECTION

The DISK 1 controller allows multiple DMA devices to be active on the S-100 bus at one time. As long as a DMA board (temporary bus master) conforms to the IEEE 696 specifications concerning DMA arbitration and prioritization, up to 16 different bus masters may gain use of the bus in order of their assigned priority. Remember, there should never be more than one temporary bus master at the same priority level.

The priority of the DISK 1 board is selected in a binary fashion on positions 4 thru 8 on DIP switch S1 as shown below:

| SWITCH POSITION (S1) | PRIORITY<br>LEVEL | VALUE |                 |

|----------------------|-------------------|-------|-----------------|

| 5                    | PRIORITY 3        | 8     |                 |

| 6                    | PRIORITY 2        | 4     | "ON" = NO VALUE |

| 7                    | PRIORITY 1        | 2     | "OFF" = VALUE   |

| 8                    | PRIORITY O        | 1     |                 |

#### EXAMPLE:

- 1. For the highest priority (15), positions 5 thru 8 would be "OFF" (8+4+2+1=15).

- 2. For priority 9, positions 5 and 8 would be "OFF" and positions 6 and 7 would be "ON" (8+1=9).

- For the lowest priority (0), positions 5 thru 8 should be "ON".

#### MOTOR CONTROL ENABLE

A switch has been provided to allow the output bit of the software serial startup port to act as a "MOTOR-ON" bit for minifloppies. If switch S1 position 3 is "OFF", the serial port may be used, and the minifloppy motors will be on at all times. If position 3 is "ON", the "MOTOR ON" line is active and the motors may be turned "ON" by outputting a "O" to the control bit. The motors may be turned "OFF" by outputting a "1" to the control bit.

#### MODIFICATIONS FOR MINIFLOPPY DRIVES

If you have purchased a DISK 1 controller for 8 inch drives and wish to convert it to 5.25 inch operation, this modification can be performed at the factory for a nominal charge. Otherwise, the following section may serve as a guide for technically competent users to alter this board.

Several modifications need to be made to the DISK 1 board configured as an 8 inch controller prior using it with minifloppy drives. These changes will be outlined below:

- (1) The components indicated in the parts list under ALTERNATE PARTS LIST FOR MINIFLOPPY DRIVES must be substituted for the parts that are currently on the board unless they have been substituted at the factory.

- (2) The three traces on the solder side of the board pointed to by the three arrows (behind Jll, Jl2, and Jl3) must be cut with a sharp knife. Three jumpers must then be installed to connect the pads labeled "5" and "C". In addition install Jl4.

- (3) If your minifloppy does not drive the READY\* line, install a jumper on J15 between "A" and "B". If your minifloppy does drive the READY\* line, install a jumper between "A" and "C".

At this point, you should be ready to connect your minifloppy drive to the controller and verify its operation. Some alteration of the setting of R35 may be necessary for reliable double density operation. Remember that your 34 pin cable should be offset to the extreme right in connector J10 for proper operation.

DISK 1 CONNECTOR PINOUT WITH 8 AND 5.25 INCH DRIVES

|    | 8 INCH DRIVE<br>SIGNAL |    | 5 INCH DRIVE<br>CABLE PIN |                  |

|----|------------------------|----|---------------------------|------------------|

| 2  | LOW CURRENT            | 2  | NC                        |                  |

| 4  | FAULT RESET            |    | NC<br>NC                  |                  |

| 6  | FAULT                  | 6  | NC<br>NC                  |                  |

| 8  | NC                     | 8  | NC<br>NC                  |                  |

| 10 |                        | 10 | NC                        |                  |

| 12 | NC                     | 12 | NC                        |                  |

| 14 | SIDE SELECT            | 14 | NC                        |                  |

| 16 | NC                     | 16 | NC                        |                  |

| 18 | HEAD LOAD              | 18 | 2                         | NC               |

| 20 | INDEX (8")             | 20 | 4                         | NC               |

| 22 | READY                  | 22 | 6                         | DRIVE SELECT 4   |

| 24 | INDEX (5")             | 24 | 8                         | INDEX            |

| 26 | DRIVE SELECT 1         | 26 | 10                        | DRIVE SELECT 1   |

| 28 | DRIVE SELECT 2         | 28 | 12                        | DRIVE SELECT 2   |

| 30 | DRIVE SELECT 3         | 30 | 14                        | DRIVE SELECT 3   |

| 32 | DS4/MOTOR ON           | 32 | 16                        | MOTOR ON         |

| 34 | DIRECTION SELECT       | 34 | 18                        | DIRECTION SELECT |

| 36 | STEP                   | 36 | 20                        | STEP             |

| 38 | WRITE DATA             | 38 | 22                        | WRITE DATA       |

| 40 | WRITE GATE             | 40 | 24                        | WRITE GATE       |

| 42 | TRACK 00               | 42 | 26                        | TRACK 00         |

| 44 | WRITE PROTECT          | 44 | 28                        | WRITE PROTECT    |

| 46 | READ DATA              | 46 | 30                        | READ DATA        |

| 48 | NC                     | 48 | 32                        | SIDE SELECT      |

| 50 | NC                     | 50 | 34                        | READY            |

|    |                        |    |                           |                  |

PINS 1-49 ODD ARE ALL GROUND RETURNS.

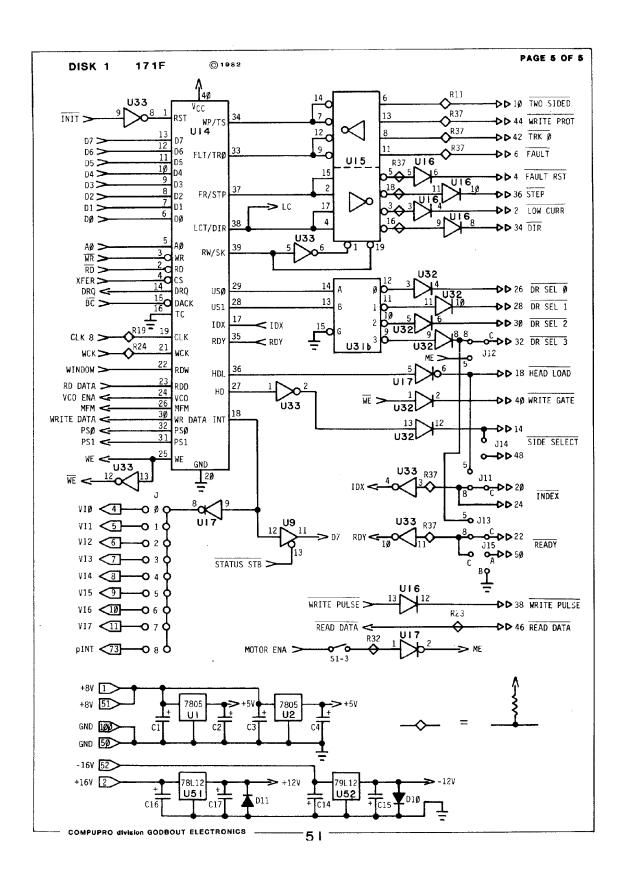

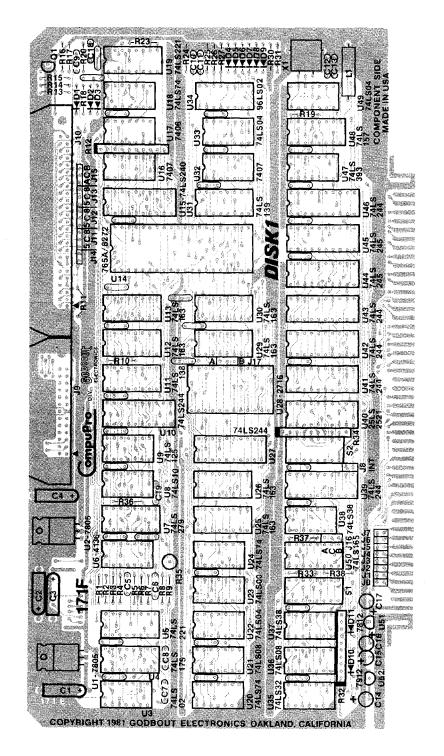

#### THEORY OF OPERATION

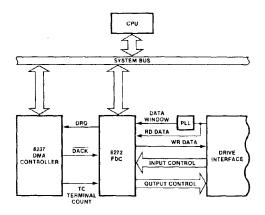

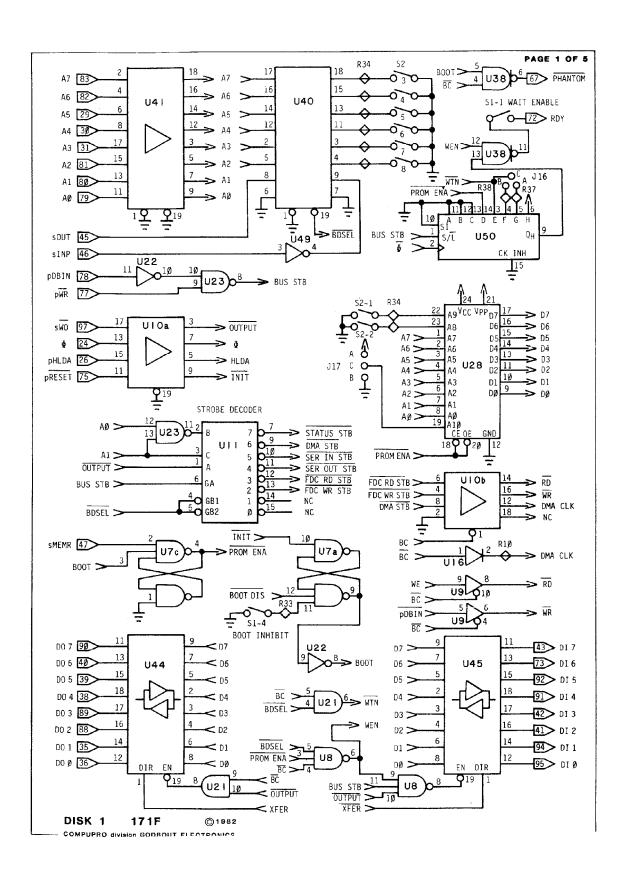

The DISK 1 board can be broken down into five subsections that will be discussed in detail in the following pages. These five subsections correspond to the five pages of the schematic, and include: (1) The Bus Interface and Boot Circuitry, (2) The DMA Counters and Address Drivers with the Serial Port, (3) The DMA Sequencing Logic and Priority Arbiter, (4) The Disk Read/Write Circuitry and Data Separator, (5) and The Floppy Disk Controller and Interface Circuitry. While reading this section it is suggested that the reader refer to the schematic and the data sheet on the controller chip.

# SECTION (1): THE BUS INTERFACE AND BOOT CIRCUITRY

This section includes the logic for the S-100 bus interface to the floppy controller, the boot circuitry, the strobe generators, the wait state circuitry and the the data bus interface. Octal bus driver U41 buffers the address lines A0 thru A7 for on-board use by the strobe decoder (U11), the boot EPROM (U28), and the address decoder (U40). Octal comparator U40 uses DIP switch S2, address lines A2 thru A7, and sOUT and sINP\* to decode a valid four port board select signal BDSEL\*. BDSEL\*, A0 and A1, OUTPUT\* (which is sWO\* buffered by U10A), and BUS STB (generated from pDBIN and pWR\* by U23), are decoded by the 3-8 line decoder U11 to generate the strobes for the floppy disk controller, the DMA registers, and the serial port. Three of these strobes are multiplexed by U10B,U9 and U16 with BC\*, WE, and pDBIN to generate the strobes for the floppy disk controller (RD\* and WR\*) and the DMA clock (DMA CLK) depending on whether a DMA bus cycle (BC) is occurring or not. During a DMA cycle, WE and pDBIN generate the control strobes for the controller chip, and BC\* clocks the DMA counters. During non-DMA cycles, U11 generates these strobes.

The boot circuitry consisting of two SR latches (U7A,C) and U24a, is initialized by INIT\* (buffered pRESET\* from U10A). When U7A is enabled by switch S1-4, INIT\* generates BOOT, which together with sMEMR generates PROM ENA\* to enable the boot EPROM whenever a memory read occurs. The boot software is contained in EPROM U28. One of eight routines within the EPROM is selected by positions 1 and 2 of switch S2 and J17. The data from the EPROM enters the internal data bus (D0-D7) and is buffered onto the S-100 bus by U45. Since PHANTOM\* is generated by U38 whenever BOOT is asserted and a DMA bus cycle (BC\*) is not occurring, and since system memory boards should be set to become disabled when PHANTOM\* is asserted, the host CPU will read the BOOT EPROM during a boot sequence. When the boot is through, U7A is reset by Q of U24a with D0=0 and SER OUT STB\* and BOOT is released.

Octal bi-directional bus drivers U44 and U45 buffer data to and from the controller board with steering from U8 and U21. When either a DMA bus cycle (BC\*) or an OUTPUT\* (command write to the FDC) occurs, U44 is enabled, and the DMA transfer line (XFER) determines the direction of the data. When XFER is high, data is transferred out of the board and onto the DO lines. When XFER is low, data is transferred from the DO bus onto the board (command write). When either a BDSEL\*, PROM ENA\* or a BC\* occurs, the WEN line is asserted, and if BUS STB and OUTPUT\* are also asserted, U45 is enabled. When XFER\* is high, the internal data is output onto the DI lines (PROM read, FDC read, or DMA write). When XFER\* is low, the data goes from the DI lines to the FDC for a disk write operation.

A wait state is left pending in shift register U50 at all times, however it is gated onto the bus only when S1-1 is closed and WEN is high. After BUS STB is asserted, U50 is allowed to shift its data once on each rising edge of \$\psi\$ during a bus strobe (BUS STB\*- pDBIN or pWR\*). The first low to inputs d-h of U50 will terminate the wait state after it has been shifted to Qh. Five cycles are required to terminate an EPROM wait state and 2, 3 or 4 cycles to terminate either an I/O or DMA wait state. The wait states are enabled only when switch S1-1 is closed (ON), and WEN is asserted (EPROM read, I/O operation, or DMA cycle).

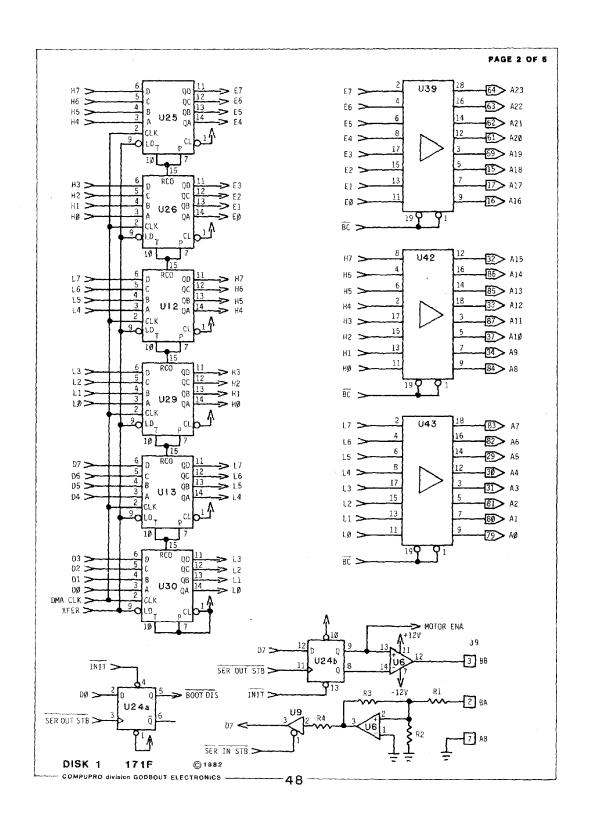

## SECTION (2) DMA COUNTERS AND ADDRESS DRIVERS

The six DMA counters (U12,13,25,26,29, and 30) form a parallel loading 24 bit counter for address generation during the DMA transfer cycle. When XFER is not asserted (low), and DMA CLK rises (from DMA STB\*, non-DMA cycle), the counters are loaded from the internal data bus (U13, U30) or from the previous stage of counter (U12, U29 or U25, U26). When XFER is asserted (a DMA cycle), DMA CLK is generated by BC\*, and the counters are incremented for the next byte transferred.

The address buffers (U39, 42, and 43) drive the 24 bits of information from the DMA counters out onto the bus whenever BC\* is asserted (during a DMA transfer). Since a full 24 bits of counter are present in this circuit, DMA transfers become independent of the 64K boundaries normally present in 8 bit processors. This allows 16 bit processors with up to 24 bits of direct addressing to be fully supported.

The software controlled serial channel is supported through two sections of op-amp U6, "D" type latch U24B, and one section of Tri-state driver U9. Data bit 7 is latched by U24B on the rising edge of SER OUT STB\*, and the Q and Q\* outputs drive U6 to convert the levels to the +12V for RS-232 operation. The Q output also drives the MOTOR ENA line for motor control of minifloppy drives, and INIT\* clears the latch on power-up. The RS-232 input levels are shifted to a TTL compatible level with the other section of U6 and this TTL level is gated onto the data bus by buffer U9 whenever a SER IN STB\* occurs.

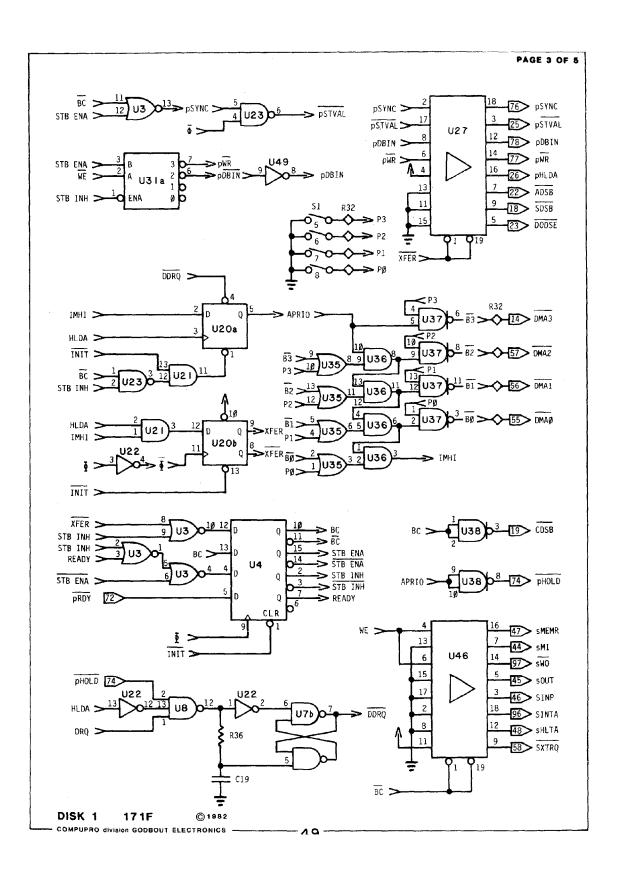

# SECTION (3) THE DMA ARBITER AND SEQUENCER LOGIC

A DMA cycle is initiated when the floppy disk controller asserts the data request (DRQ) line, the pHOLD\* line is not asserted, and the hold acknowledge line (HLDA) is not asserted. After a delay of up to 1.6 uSEC through U22, U7B, R36 and C19, U20A is preset and causes the assert priority line (APRIO) to be asserted along with the pHOLD\* line. The priority is asserted onto the DMAO\* -DMA3\* lines as generated and checked by the logic of U35, 36, 37, and switch S1 positions 5 thru 8. The highest priority line DMA3\* is asserted first depending on the switch setting, and if the DMA3\* line agrees with the asserted priority (no one with higher priority is asserting the line), then the next lowest priority line (DMA2\*) is asserted and checked as in the first case. This process repeats until either a priority mismatch occurs and the sequence is held or the IMHI line is asserted indicating that this board is the highest priority. U20A and the APRIO sequence is held while the processor acknowledges the hold by asserting HLDA line and the DMA cycle occurs. The sequence is terminated at the end of the DMA cycle with BC\* and STB INH (U23) or when a reset occurs (INIT\* -

U21). As soon as HLDA and IMHI are asserted (U21), the transfer state is entered (XFER or XFER\*) in U20B on the next rising edge of  $\Phi$ \*. This state causes the S-100 control strobes to be driven onto the bus in an IDLE state condition with all addresses, status, DO buffers, and control strobes disabled by buffer U27 and U38.

The transfer state is controlled by the sequencing logic of quad "D" latch U4, NOR gates of U3, and U21. Each new state is initiated on the meeting of several conditions and the rising edge of . When XFER\* is asserted, and STB INH is not, the bus cycle (BC, BC\*) is initiated, the S-100 status lines (U46) and the DMA address lines (U39, 42, and 43) are driven onto the bus. In addition, BC\* is fed back to the FDC as an acknowledge signal (DACK), allowing the FDC to enter the data transfer mode. In the next state after BC is asserted, the STB ENA and STB ENA\* lines are asserted. This causes the strobes to be switched from the IDLE state to either a read or write state depending on the WE\* signal from the FDC. The strobes pDBIN\* and pWR\* are generated by U31A, pSYNC is generated from BC\* and STB INH in U3, and pSTVAL\* is generated from pSYNC and \* in U23. The READY state is constantly being generated by pRDY\* and is updated every cycle of  $\Phi$ . When either READY is asserted or STB INH is asserted (U3), and STB ENA\* is asserted, the strobe inhibit state (STB INH or STB INH\*) is entered. This causes the strobes to be returned to the IDLE state as long as a wait state is not requested. If a wait state has been requested, the strobes will not be changed until the READY state occurs. STB INH also causes the APRIO line to be reset, and on the next rising edge of  $\phi$ , the bus cycle (BC) will be terminated causing the status and address lines to be removed from the bus. As soon as pHOLD\* is released and HLDA stops being asserted, the next edge of \* will cause the termination of the transfer state (XFER) and the removal of the S-100 strobes and the IDLE state on the bus.

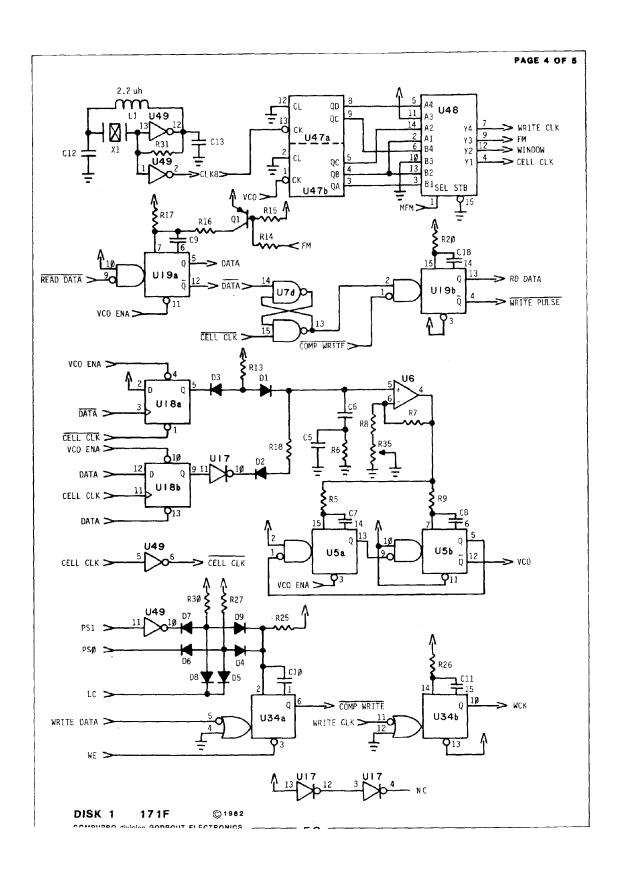

#### SECTION (4) DISK READ/WRITE CIRCUITRY AND DATA SEPARATOR

The master clock for the FDC is generated by a crystal oscillator consisting of X1, L1, and U49. This clock is fed to the FDC and is divided by U47A to yield the WRITE CLK through U48 at the proper frequency determined by the signal MFM from the FDC. WRITE CLK is converted to a 250 nSEC. pulse by U34B and is fed to the FDC. The two write precompensation signals PSO and PS1 and the low current signal LC alter the value of the timing resistor of U34A by diode current gating, and allow a varying delay in the disk write data. WRITE DATA from the FDC is fed to U34A, and when enabled by WE and time varied by the precompensation logic, and variable length COMP WRITE\* signal is generated. This pulse will have typical output length of 1.1, 1.3, and 1.5 uSEC. for an alteration from NORMAL, (200 nSEC), EARLY, and LATE precompensation. The COMP WRITE\* signal is fed to U19B for conversion to a 250 nSEC. pulse signal (WRITE PULSE\*) for feeding to the disk.

A phase lock loop is formed by a charge pump consisting of U18, U17, diodes D1-3, and resistors R13 and R18, an error amplifier and integrator consisting U6, C5-6, and R6-8 and R35, and a voltage controlled oscillator (VCO) consisting of U5, R5, R9, and C7-8. The VCO is adjusted by R35 to oscillate at approximately 2.0 MHz when enabled by the signal VCO ENA from the FDC. The output VCO is divided by U47B, and the divided outputs are selected by multiplexor U48 for the proper frequency depending on the current mode (MFM) to generate the signals WINDOW and CELL CLK. Read data (READ DATA\*) from the disk is fed to U19A for conversion to a 500 nSEC. or 1000 nSEC. pulse depending on

the state of the FM line (500 nSEC. in MFM, 1000 nSEC. in FM). DATA and DATA\* along with CELL CLK and CELL CLK\* are fed to the charge pump which determines the relative position of the CELL CLOCK with respect to the DATA and generates a voltage at pin 5. This voltage represents the error in the positioning of the DATA signal with respect to the edge of CELL CLK. This error voltage is integrated and fed to the error amplifier which adjusts the frequency of the voltage controlled oscillator to bring the DATA pulse back in line with the CELL CLK and correspondingly adjust the WINDOW signal (which defines the data cell for the FDC). The DATA\* and CELL CLK\* signals set and clear U7D, and generate a constant 250 nSEC. read pulse for the FDC (RD DATA).

## SECTION (5) THE FLOPPY DISK CONTROLLER AND INTERFACE CIRCUITRY

The floppy disk controller chip (U14) provides for the bridging of the previous four sections to the disk interface circuitry and the disk drives. The FDC is reset by INIT\* inverted by U33, and is connected to the internal data bus through DO-D7. The FDC interface to the internal bus is controlled by AO, WR\*, RD\*, and XFER, which leave the FDC enabled at all times except during a transfer state, and steer the data with WR\*, and RD\*. DRQ initiates the DMA cycle, and BC\* initiates the FDC data transfer. CLK and WCK are pulled up by R19 and R24 to achieve a greater voltage swing for the internal clocking logic of the FDC. WINDOW describes the data cell time of the RD DATA pulse from the data separator, and VCO ENA enables the voltage controlled oscillator and MFM describes whether the FDC is expecting single or double density data. WRITE DATA feeds the write precompensation circuitry with PSO and PS1 describing the amount of precomp needed for the particular data pattern. The WE and WE\* (inverted by U33) lines control the enabling of the write circuitry and are used to determine the direction of the data transfers to and from the FDC. The INT output from the FDC is the general interrupt signal that is fed to buffer Ul7 for driving the vectored interrupt lines (VIO-VI7) and pINT if jumpered. INT is also buffered by Tri-state buffer U9, which gates the interrupt status onto D7 when a STATUS STB\* occurs.

The Drive interface signals are decoded and buffered as described below. The HD line is inverted by U33 and buffered by U32 to drive the SIDE SELECT\* line to determine which head of a double sided drive to use. HDL is inverted and used to drive the HEAD LOAD\* line of the drive. The RDY signal is controlled by the inverted (U33) READY\* line and the IDX signal is controlled by the inverted (U33) INDEX\* line from the drive. The unit select lines USO and USI are fed to decoder U31B to decode the one of four drives possible with this controller, and these four signals are buffered by four sections of U32 to drive the DR SELO\* through DR SEL3\* lines of the drives. The four signals WP/TS, FLT/TRO, FR/STP, and LCT/DIR each have two functions which are determined by the RW/SK line (read-write/seek). During a read or write operation, the drive signals WRITE PROT\*, and FAULT\* are inverted and fed to the FDC lines WP/ and FLT/ and the FDC lines FR/ and LCT/ are inverted (Ul5) and buffered (Ul6) to drive the FAULT RESET\* and LOW CURRENT\* drive lines. During a seek operation, the drive signals TWO SIDED\*, and TRACK O\* are inverted and fed to the FDC lines /TS and /TRO and the FDC lines /STP and /DIR are inverted (Ul5) and buffered (Ul6) to drive the STEP\* and DIRECTION\* drive lines. These changes are controlled by the RW/SK line which determines which half of UI5 will be enabled. The WRITE PULSE\* line is buffered (U16) to drive the WRITE DATA\* line and the READ DATA\* line is terminated and fed directly to U19A. The MOTOR ENA signal is run through disable switch S1-3 and inverted to feed the ME line which becomes

MOTOR ON\* on the minifloppy drives. All lines coming from the floppy drives are terminated by 150 ohm resistors, and jumpers J11-15 are used to select either 5.25" or 8" drives.

Regulators U1 and U2 provide the regulated +5 volts for the board, and U51 and U50 provide the regulated  $\pm 12$  volts for the op-amp. Diodes D10 and D11 insure that U50 and U51 do not shut each other down on power-up due to the op-amp not being ground referenced.

# TEST ROUTINES FOR THE DISK 1 CONTROLLER

The following program contains primitive routines for (1) Loading the DMA address counters, (2) Specifying the drive characteristics to the controller, (3) Recalibrating the drive (seeking track 00), (4) Seeking a particular track on the drive, (5) Reading sectors from the drive in either single density or 1024 byte double density, and (6) Writing sectors to the drive in either single density or 1024 byte double density. The user should be familiar with the data sheet for the floppy disk controller since these routines are designed to give the user a greater understanding of the operation of the 8272/765A. These routines are by no means the basis for a disk operating system, and are designed for experimentation only.

This program should be treated as several callable subroutines using the jump table at the beginning for reference.

NOTE: This program was written to assemble under an ACT assembler and may require slight modification to assemble under CP/M-80 ASM.

# TITLE 'TEST ROUTINES FOR COMPUPRO DISK CONTROLLER.'

;DTEST - Test Routines for CompuPro Disk Controller.

#### DISK TEST

COMPUPRO

Oakland Airport

Oakland, California 94611

Copyright 1981, CompuPro Corporation.

This product is a program product of CompuPro and is supplied for use with the CompuPro IEEE 696 Floppy Disk Controller.

Version number: 1.1B Version date: April 13, 1981

BEGIN EQU 0100h

Assembly Constants FDPORT EQU OCOH

FDCS EQU FDPORT FDCD EQU FDPORT+1 ;Base port address for Controller

;Status register ;Data register

```

FDMA

EQU

FDPORT+2

;Dma address (when write)

EQU

INTS

FDPORT+2

;Status Register (when read)

SER

EQU

FDPORT+3

;Serial port

Controller function definitions

Specify (00) command

F.RTK

02

;Read track

F. SPEC

=

03

;Specify

F.DSTS

04

;Drive status

F.RDAT

06

;Read sector FM

F.DRDT

46H

;Read sector MFM

F.WRAT

05

;Write sector FM

F. WRDT

45H

;Write sector MFM

; recalibrate

F. RECA

07

F.RSTS

08

;Read status

F. SEEK

0Fh

;Seek

SRT

16-8

;= Shugart 800s (8 ms)

16-3

;= Shugart 850s (3 ms)

;

16-3

;= Remex (3 ms)

HUT:

240/16

;Head unload = 240 ms

HLT:

(35+1)/2

; Head load = 35 ms

ND:

;Set DMA mode

JUMP TABLE FOR ROUTINES

These routines are callable subroutines

;

Some require parameters passed in the "A" and "C" registers

ORG

BEGIN

START:

JMP

DDMA

;load DMA address

JMP

DSPEC

;specify drive stat

JMP

RCAL

;recalibrate (track 00)

JMP

DSEEK

;seek a track

JMP

READS

;read sector (FM)

JMP

DREADS

;read sector (MFM)

.TMP

WRS

;write sector (FM)

JMP

DWRS

;write sector (MFM)

DMA address load routine using 16 bit value in

HL register for the 24 bit DMA value

DDMA:

MVI

A,0

;extended address

OUT

FDMA

;output

MOV

A,H

;high byte

OUT

FDMA

;output

MOV

A,L

;low byte

OUT

FDMA

;output

RET

Drive Specify Command

DSPEC:

MVI

B, LSPEC

;3 byte command

LXI

D, SPEC

;point to command bytes

SPEC1:

IN

FDCS

;get status

ANI

ОСОН

CPI

80н

JNZ

SPEC1

; if no master ready bit

```

```

:load command byte

LDAX

OUT

FDCD

;to controller

;next byte

INX

D

;dec. counter

DCR

В

JNZ

SPEC1

; if more bytes

RET

Recalibrate drive (seek track 0)

B, LRECAL

RCAL:

;2 byte command

MVI

LXI

D, RECAL

;point to command bytes

RCAL1:

IN

FDCS

;get status

ANI

0C0H

CPI

80H

JNZ

RCAL1

; if no master ready bit

;load command byte

LDAX

D

OUT

FDCD

;to controller

INX

D

DCR

В

; if more bytes

JNZ

RCAL1

RET

Seek a Track with cylinder number in "A"

DSEEK:

B, LSEEK

;3 byte command

;point to command bytes

LXI

D, SEEK

STA

CYLD

;store cylinder #

SEEK1:

IN

FDCS

;check status

ANI

OCOH

CPI

80H

;if not ready

JNZ

SEEK1

LDAX

D

;load command byte

;to controller

OUT

FDCD

INX

D

DCR

В

JNZ

SEEK 1

; if more bytes

RET

FM Sector read command with sector in "A"

and cylinder in "C"

READS:

B, LREAD

;9 byte command

MVI

LXI

D, READ

;point to command bytes

STA

;store sector number

RSEC

MOV

A,C

RSCYL

STA

;store cylinder number

READ1:

IN

FDCS

;check status

OR

A

; if no master ready bit

JP

READ1

LDAX

;load command byte

D

OUT

FDCD

;to controller

INX

D

DCR

READ1

JNZ

; if more bytes

READ2:

IN

INTS

; check interrupt status

ORA

; for read complete

JP

READ2

; If not complete

```

```

READ3:

FDCS

IN

;in status

ORA

A

JP

READ3

; if not ready

IN

FDCD

;read result byte STO

SUI

40h

;strip

MOV

L,A

;save

READ4:

IN

FDCS

;in status

ORA

A

; if not ready

JP

READ4

IN

FDCD

;read result byte ST1

SUI

80h

;strip

MOV

H,A

;save

MVI

B,7-2

;5 more bytes

READ5:

IN

FDCS

; in status

OR

JР

READ5

; if not ready

IN

FDCD

;read result byte

DEC

JNZ

READ5

;wait until all done

MOV

;check results

A,L

ORA

H

RZ

;return no error

STC

;set carry

RET

;return from error

MFM Sector read command with sector in "A"

and cylinder in "C"

DREADS:

B, DLREAD

IVM

;9 byte command

D, DREAD

LXI

;point to command bytes

DRSEC

STA

;store sector number

MOV

A,C

STA

DCYL

;store cylinder number

DREAD1:

IN

FDCS

;check status

OR

JP

DREAD1

; if no master ready bit

LDAX

D

;load command byte

OUT

FDCD

;to controller

INX

D

DCR

В

JNZ

DREAD1

; if more bytes

JMP

READ2

FM Sector write command with sector in "A"

;

cylinder number in "C"

WRS:

IVM

B,LWR

;9 byte command

LXI

D,WR

;point to command bytes

STA

WSEC

;store sector number

MOV

A,C

STA

WSCYL

;store cylinder number

WR1:

IN

FDCS

; check status

OR

A

JΡ

WR1

; if no master ready bit

LDAX

D

; load command byte

```

```

FDCD

;to controller

OUT

INX

D

DCR

В

JNZ

WRl

; if more bytes

READ1

JMP

MFM Sector write command with sector in "A"

and cylinder in "C"

DWRS:

B, DLWR

;9 byte command

MVI

D, DWR

;point to command bytes

LXI

DWSEC

STA

;store sector number

MOV

A,C

STA

DWRCYL

;store cylinder number

DWR1:

IN

FDCS

;check status

OR

Α

JΡ

DWR1

; if no master ready bit

;load command byte

LDAX

OUT

;to controller

FDCD

INX

D

DCR

В

JNZ

DWR 1

;if more bytes

READ2

JMP

Function data for controller

;specify command

SPEC

DB

F.SPEC

4®SRT,4®HUT

VFD

VFD

7®HLT, 1®ND

LSPEC

*-SPEC

RECAL

DB

F.RECA, 0

;recalibrate command

*-RECAL

LRECAL

SEEK

DB

F.SEEK

;seek command

0

DB

CYLD

DB

0

LSEEK

*-SEEK

;read command (FM)

READ:

DB

F.RDAT

;hds,dsl,ds0

DB

0

;C = cylinder info

RSCYL

DB

0

DB

0

;Head

RSEC:

DB

;Record (first sector)

1

DΒ

0

;N 128 BYTE SECTOR

;EOT (last sectors)

DB

25

;GPL

DB

7

DB

128

;DTL

LREAD

*-READ

DREAD:

DB

F.DRDT

;read command (MFM)

DB

0

;hds,ds1,ds0

DCYL

DB

2

;C = cylinder info

DB

0

;Head

DRSEC:

;Record (first sector)

DB

1

DB

3

;N 1024 BYTE SECTOR

;EOT (last sectors)

DB

7

```

```

;GPL

35H

DB

DB

0

;DTL

DLREAD

*-DREAD

;write command (FM)

WR:

DB

F.WRAT

;hds,ds1,ds0

0

DB

WSCYL

0

;C = cylinder info

DB

;Head

DB

;Record (first sector)

WSEC:

DB

;N 128 BYTE SECTOR

DB

0

;EOT (last sectors)

DB

25

DB

7

;GPL

128

;DTL

DB

LWR

*-WR

DWR

DB

F.WRDT

;write command (MFM)

;hds,ds1,ds0

DB

;C = cylinder info

DWRCYL

2

DB

;Head

DB

0

;Record (first sector)

;N 1024 BYTE SECTOR

DWSEC:

DΒ

1

3

DB

7

;EOT (last sectors)

DB

;GPL

DB

35H

DB

0

;DTL

DLWR

=

*-DWR

END

```

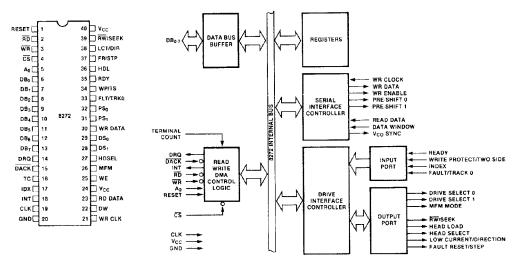

# 8272 SINGLE/DOUBLE DENSITY FLOPPY DISK CONTROLLER

- IBM Compatible in Both Single and Double Density Recording Formats

- Programmable Data Record Lengths: 128, 256, 512, or 1024 Bytes/Sector

- Multi-Sector and Multi-Track Transfer Capability

- Drive Up to 4 Floppy Disks

- Data Scan Capability Will Scan a Single Sector or an Entire Cylinder's Worth of Data Fields, Comparing on a Byte by Byte Basis, Data in the Processor's Memory with Data Read from the Diskette

- Data Transfers in DMA or Non-DMA Mode

- Parallel Seek Operations on Up to Four Drives

- Compatible with Most Microprocessors Including 8080A, 8085A, 8086 and 8088

- Single-Phase 8 MHz Clock

- Single +5 Volt Power Supply

- Available in 40-Pin Plastic Dual-in-Line Package

The 8272 is an LSI Floppy Disk Controller (FDC) Chip, which contains the circuitry and control functions for interfacing a processor to 4 Floppy Disk Drives. It is capable of supporting either IBM 3740 single density format (FM), or IBM System 34 Double Density format (MFM) including double sided recording. The 8272 provides control signals which simplify the design of an external phase locked loop, and write precompensation circuitry. The FDC simplifies and handles most of the burdens associated with implementing a Floppy Disk Drive Interface.

# PIN CONFIGURATION

#### 8272 INTERNAL BLOCK DIAGRAM

#### 8272 SYSTEM BLOCK DIAGRAM

#### **DESCRIPTION**

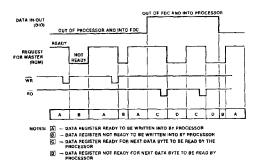

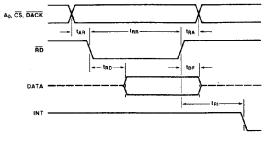

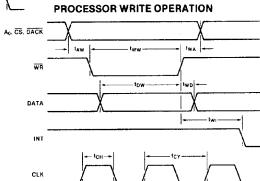

Hand-shaking signals are provided in the 8272 which make DMA operation easy to incorporate with the aid of an external DMA Controller chip, such as the 8237. The FDC will operate in either DMA or Non-DMA mode. In the Non-DMA mode, the FDC generates interrupts to the processor for every transfer of a data byte between the CPU and the 8272. In the DMA mode, the processor need only load a command into the FDC and all data transfers occur under control of the 8272 and DMA controller.

There are 15 separate commands which the 8272 will execute. Each of these commands require multiple 8-bit bytes to fully specify the operation which the processor wishes the FDC to perform. The following commands are available.

Sense Drive Status

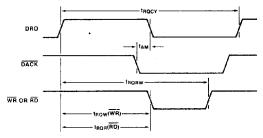

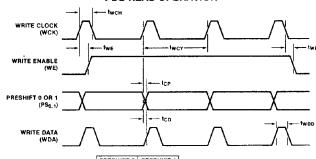

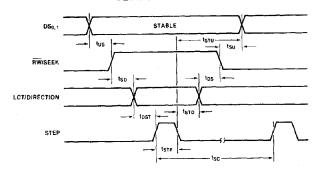

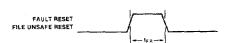

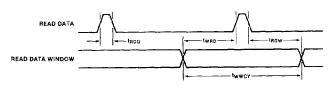

| Read Data          | Write Data              |