TTY

# -SERIAL I/O BOARD

# **DOCUMENTATION**

# **CONTENTS**:

THEORY OF OPERATION

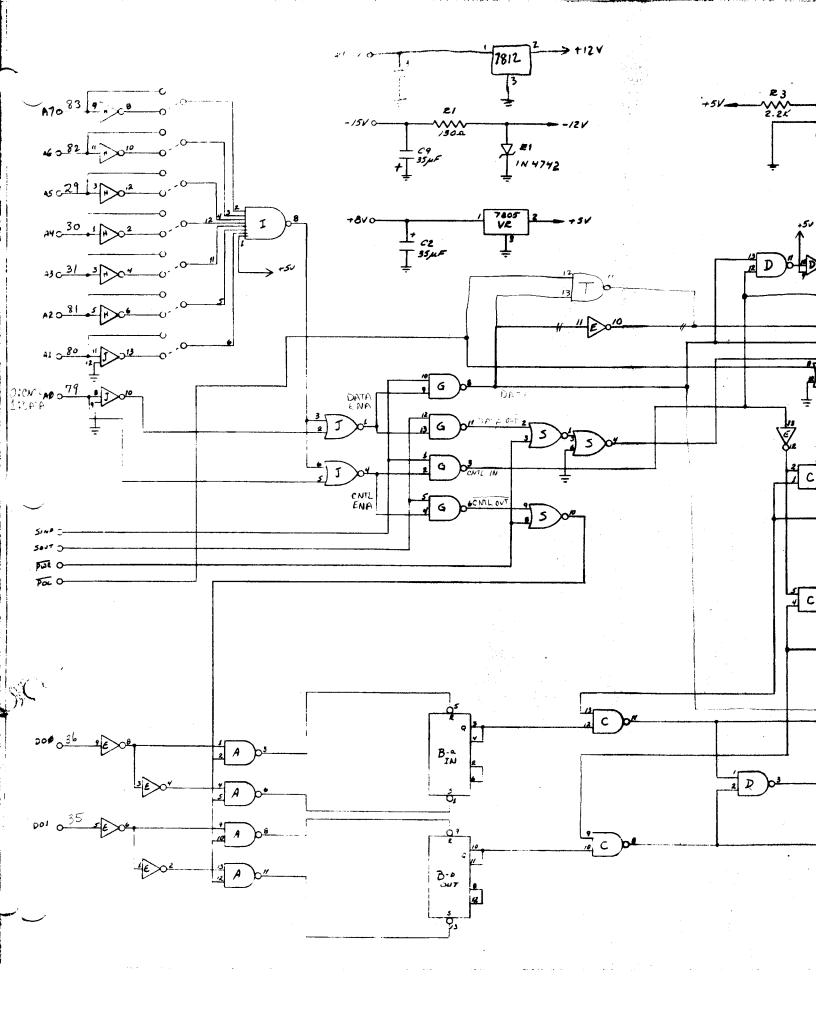

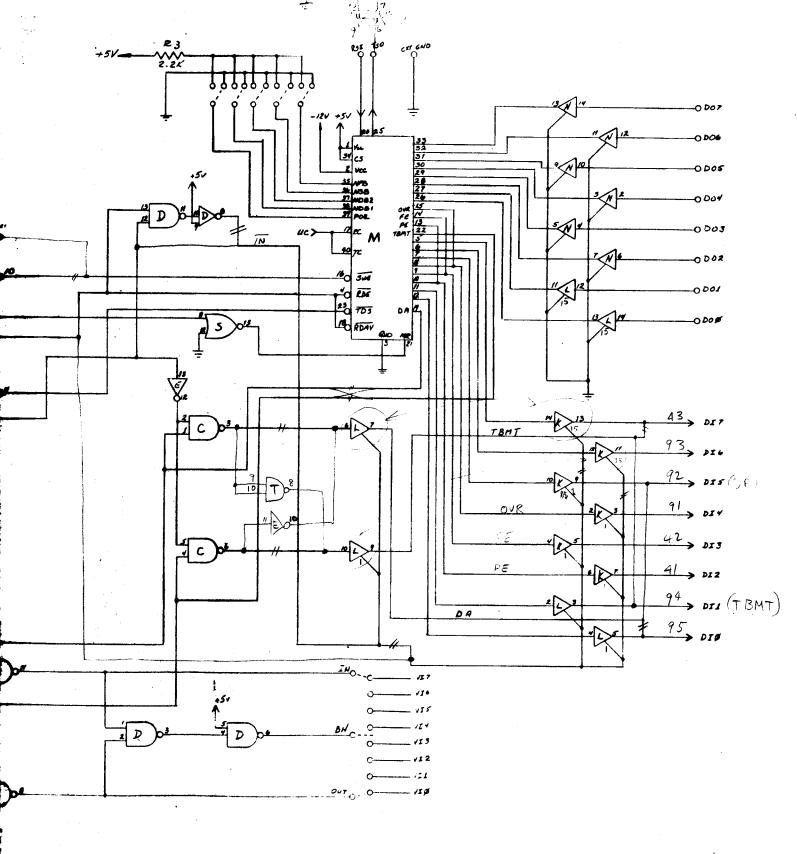

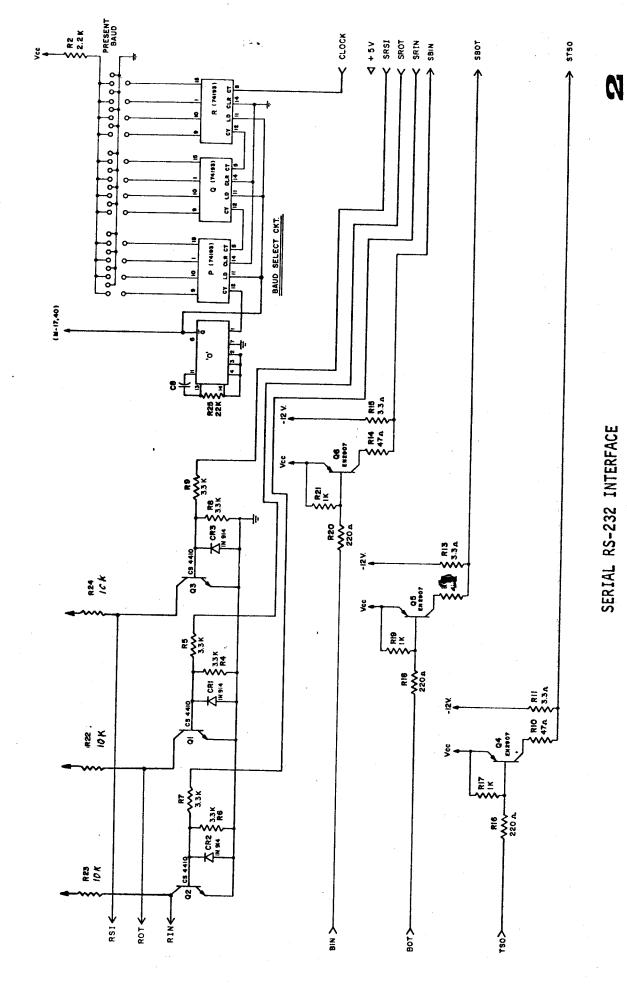

SCHEMATICS

ASSEMBLY PROCEDURE (ommitted on assembled units)

ADDRESS SELECTION CHART

BAUD RATE SELECTION CHART

© MITS, Inc., 1975

PRINTED IN U.S.A.

# THEORY of OPERATION

#### 88-SIO SERIAL INTERFACE BOARD OPERATION

The serial interface board provides communication between the ALTAIR and any serial Input/Output devices. The board has two device code addresses which are hardware selectable by jumpers for any even numbered address from 0 to 376 (octal). The BAUD rate is also selectable, via jumpers, from 0 through 25,000 BAUD. This board also provides both hardware and software interrupt capability.

#### Device Select Logic

When the CPU executes an "OUT" or an "IN" instruction, it places the device address (provided with the instruction) on both the 8 lower order address bus lines and the 8 higher order address bus lines.

The 8 lower order address bus lines are fed to the select logic on the board, IC's H & J. If the address on the bus is equal to the address selected on the board, IC I pin 8 will go low, thus enabling IC J pins 3 & 6.

Depending on the state of AO (the least significant address bit), either the control channel or the data channel will be enabled. If AO is at a logic low level, IC J pin 4 will go high, thus enabling the control channel. If AO is at a logic high level, IC J pin 1 will go high, thus enabling the data channel. Of the two device addresses on the board, the control channel is always an even number and the data channel is always an odd number.

### Control Channel

The control channel has two purposes: it is used to enable/disable the hardware interrupt capability for the Input or Output device, and to test the status of the Input/Output device.

After an "IN" instruction is executed with the control channel address, "SINP" goes high and IC J pin 4 is high thus causing IC G pin 3 to go low. This enables  $\overline{\text{SW}}_{-}^{\text{SW}}$  (Status Word Enable) at IC M pin 16 and causes IC E pin 12 and IC D pin 8 to go low, thus enabling the Data In lines. (Note that IC D pin 12 is always high except during the initial power on clear,  $\overline{\text{POC}}$ .) This inputs the data to the Data In lines and into the CPU accumulator.

The eight data bits are defined in the chart on the following page.

#### Bit Definition

| DATA BIT | LOGIC LOW LEVEL                                                                                                                   | LOGIC HIGH LEVEL                                                                                               |

|----------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 7        | Output device Ready (a ready pulse has been sent from the device) Also causes a hardware interrupt to occur if interrupt enabled. | Not Ready                                                                                                      |

| 6        | NOT USED                                                                                                                          | NOT USED                                                                                                       |

| 5        |                                                                                                                                   | Data Available (a word of data is in the buffer on the I/O board)                                              |

| 4        |                                                                                                                                   | Data Overflow (a new word of data has been recieved before the previous word was inputed to the accumulator)   |

| 3        |                                                                                                                                   | Framming Error (data word<br>has no valid stop bit)                                                            |

| 2        |                                                                                                                                   | Parity Error (recieved<br>parity does not aggree<br>with selected parity)                                      |

| ן        |                                                                                                                                   | X-mitter Buffer Empty (the<br>previous data word has been<br>X-mitted and a new data<br>word may be outputted) |

| 0        | Input device Ready (a<br>ready pulse has been<br>sent from the device)                                                            |                                                                                                                |

When an "OUT" instruction is executed with the control channel address, data bits 0 & 1 are gated through IC's E & A to the Input/Output interrupt flip-flops, IC B.

The chart below describes the result of setting these two bits.

| _D0  | <u>D1</u> | OUTPUT INTERRUPT | INPUT INTERRUPT |

|------|-----------|------------------|-----------------|

| low  | low       | disabled         | disabled        |

| low  | high      | enabled          | disabled        |

| high | low       | disabled         | enabled         |

| high | high      | enabled          | enabled         |

As an example: to enable the input device and disable the output device interrupts, load the accumulator with the following:

$$(X = don't care)$$

$\frac{D7}{X} \frac{D6}{X} \frac{D5}{X} \frac{D4}{X} \frac{D3}{X} \frac{D2}{X} \frac{D1}{X} \frac{D0}{1}$

then execute an "OUT" instruction with the control channel address.

#### Data Channel

The data channel transfers the 8 bit data words between the device and the CPU.

An "OUT" instruction, accompanied by the data channel address (odd numbered address), will pull "SOUT" and IC J pin 1 high, causing IC G pin 11 to go low. As soon as the CPU has put the data from the accumulator onto the data out bus, PWR goes low pulling IC S pin 4 low to strobe TDS (Transmit Data Strobe) at pin 23 of IC M. This causes the parallel data on the bus to be loaded and then transmitted serialy. Pin 4 of IC S also resets the output ready flip-flop (IC F-b) to clear the busy signal to the device.

An "IN" instruction with the data channel address will pull "SINP" and pin l of IC J high causing pin 8 of IC G to go low, thus enabling RDE (Recieved Data Enable) at pin 4 of IC M and the Data In lines (IC D pin 8). This puts the recieved data on the bus and the CPU strobes it into the accumulator during DBIN (Data Bus In). Pin 8 of IC G also resets the input ready flip-flop (IC F-a) and the UART Data Available flip-flop, RDAV at pin 18 of IC M.

#### <u>UART</u>

The Universal Asynchronous Reciever-Transmitter (UART) provides the paralled to serial and serial to parallel data conversion necessary to interface a serial device with the parallel ALTAIR. It also has a status word for "handshake" and error checking.

Both the Reciever and the Transmitter require a clock input frequency that is 16 times the BAUD rate. This is accomplished with a 12 bit presetable counter (IC's P, Q & R) and a single shot (IC O). If the frequency required is not found in the "BAUD RATE SELECTION CHART" included in this manual, use the formula below:

Preset Count Frequency =

$$\frac{400}{400}$$

-  $\frac{Period of Output Frequency (us)}{.5us}$

The maximum frequency is 400KHz. The maximum BAUD rate is (400K/16) 25,000 BAUD.

The UART (IC M) has several programable functions as described below.

| UART PIN #  | <u>name</u>  | FUNCTION                                                                                 |

|-------------|--------------|------------------------------------------------------------------------------------------|

| <b>35</b> . | NPB          | Eliminates parity bit from being transmitted when tied high (see pin 39, POE)            |

| 36          | NSB          | When tied low, one stop bit is transmitted When tied high, two stop bits are transmitted |

| 37<br>38    | NDB2<br>NDB1 | Defines the number of data bits per character as shown below:  NDB2 NDB1 # of Bits       |

|             |              | low low 5                                                                                |

|             |              | low high 6                                                                               |

|             |              | high low 7                                                                               |

|             |              | high high 8                                                                              |

| 39          | POE          | If NPB is tied low, POE defines whether parity will be odd or even as shown below:       |

|             |              |                                                                                          |

| POE  | <u>NPB</u> | PARITY |                  |

|------|------------|--------|------------------|

| low  | low        | odd    |                  |

| high | low        | even   |                  |

| X    | high       | none   | (X = don't care) |

4

#### <u>Interrupt</u>

The serial board is provided with hardware interrupt capability. The pads on the board labeled "OUT", "IN" & "BH" are provided for interrupt control. These three pads represent the <u>Output</u> device, the <u>Input</u> device or <u>BotH</u> devices and are jumpered to one or more of the pads labeled "VI" and numbered O through 7 at the bottom of the board.

"VI" represents "Vectored Interrupt" and the numbered pads, 0 through 7, are the 8 interrupt lines which connect into the Vectored Interrupt Board (88-VI). The numbers 0 through 7 correspond to the 8 priority levels, with 0 being the lowest and 7 the highest priority.

You can assign the input device and the output device each a different priority, or you can assign both devices a single priority. If you do not have the 88-VI board, you can jumper one of the three pads ("OUT", "IN" & "BH") on one of your I/O boards to the processor input interrupt line.

The processor input interrupt line has a pad (unlabeled) to the right of the VI pads on the board (see assembly manual). This will allow one level of interrupt to the processor. When the interrupt occurs, the processor will immediately jump to the location 70 (octal) and begin execution. Place your interrupt service routine in locations 70 through 77 (octal).

$$\phi.70 = H.38$$

$\phi.77 = H.3F$

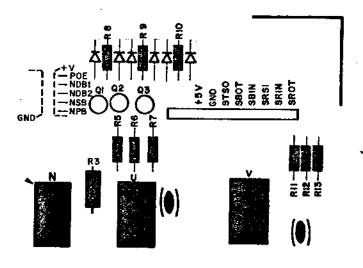

# SERIAL I/O INTERFACE OPERATION

The 88-SIO A Board is a standard RS-232 level interface board.

The output signals "BIN", "BOT" and "TSO" are standard TTL levels (0v = 1ow, +2v = high). Using the "BIN" signal as an example, these three signals are changed to RS-232 levels (+3v = high, -12v = 1ow) as follows:

When "BIN" goes to its high active state, the base of Q6 becomes positive and turns off. The output signal, "SBIN", is then pulled to -12v through resistor R15.

When "BIN" returns to its normal low state, Q6 turns on, pulling the "SBIN" signal to approximately +3 volts through resistor R14.

The input signals "SRSI", "SROT" and "SRIN" are shifted from the RS-232 levels to TTL levels as follows, using "SRSI" as an example:

When "SRSI" goes high (+3v or greater), Q3 turns on, pulling "RSI" close to ground. When "SRSI" goes negative, Q3 turns off and is protected from a larger negative voltage than -1v by CR3. With Q3 off, "RSI" is pulled to +5v through resistor R24.

The 88-SIO B Board is a standard ITL level interface board.

The three input signals "SRSI", "SRIN" and "SROT" and the three output signals "BIN", "BOT" and "TSO" are fed through non-inverting buffers (IC U).

The input requires .5ma worst case, and the output will drive a maximum of 20 normal TTL loads (48 milliamps).

The 88-SIO C Board is a standard TTY level interface board.

The output signal "BIN" (TTL level) is inverted through IC U pins 1 & 2, and fed to the base of Q1. Q1's emitter is pulled to approximately 1.6 volts through CR4 & CR5, which causes Q1 to conduct when IC U pin 2 is low. This allows current flow through R8 and Q1 and to the device. When IC U pin 2 is high, Q1 turns off presenting a high impedance to the device. The signals "BOT" & "TSO" function in the same manner.

The input signal "SRSI" (TTL level) is buffered and inverted through IC V pins 13 & 12, and re-inverted through IC V pins 11 & 10. Thus "SRSI" & "RSI" are both low or both high. The signals "SRIN" and "SROT" function in the same manner.

# 1/0 ADDRESS SELECTION CHART

| ADDRESS     | 11 ET 4    | 17            |                | CONNECT         |                | **             | ••         |               |

|-------------|------------|---------------|----------------|-----------------|----------------|----------------|------------|---------------|

| OCTAL       | HEX        |               | 16             | I5              | 14             | <u> 13</u>     | 12         |               |

| 000         | 00         | <b>A</b> 7    | <del>A6</del>  | Ā5 <sup>-</sup> | <del>A4</del>  | <del>A3</del>  | Ā2         | ΑT            |

| 002         | 02         | Ā7            | A6             | Ā5              | <b>A4</b>      | <del>A3</del>  | A2         | A]            |

| 004         | 04         | A7            | <del>A6</del>  | Ā5              | <del>A</del> 4 | <u>A3</u>      | A2         | ĀΤ            |

| 006         | 06         | <b>A7</b>     | Ā6             | <b>A5</b>       | <del>A</del> 4 | A3             | A2         | Αl            |

| 010         | 08         | Ā7            | Ā6             | <del>A5</del>   | <del>A4</del>  | А3             | A2         | ĀΤ            |

| 012         | OA         | <del>A7</del> | <del>Ā6</del>  | <b>A5</b>       | <del>A4</del>  | А3             | <u>A2</u>  | <b>A</b> 1    |

| 014         | CC         | <b>A7</b>     | <del>A6</del>  | <del>A5</del>   | <b>A4</b>      | А3             | A2         | <del>A3</del> |

| 016         | OE         | <b>A7</b>     | <del>A6</del>  | <b>A5</b>       | <b>A</b> 4     | АЗ             | A2         | A1            |

| 020         | 10         | <b>A</b> 7    | <del>A6</del>  | Ā5              | A4             | <del>A3</del>  | ĀZ         | A?            |

| 022         | 12         | · <b>Ā</b> 7  | Ā6             | Ā5              | A4             | Ā3             | Ā2         | Al            |

| 024         | 14         | <b>A7</b>     | <del>Ā</del> 6 | Ā5              | A4             | Ā3             | <b>A</b> 2 | AT            |

| 026         | 16         | <b>A7</b>     | <b>A6</b>      | Ā5              | A4             | <b>A3</b>      | A2         | A1            |

| 030         | 18         | Ā7            | Ã <del>o</del> | Ā5              | A4             | А3             | Ā2         | A1            |

| 032         | IA         | <b>A7</b>     | <b>Ā</b> 6     | Ā5              | <b>A</b> 4     | А3             | <u>A2</u>  | A1            |

| 034         | 1C         | <del>A7</del> | <del>Ā6</del>  | Ā5              | <b>A</b> 4     | АЗ             | A2         | ĀĪ            |

| 036         | E          | <b>A</b> 7    | Ã6             | <del>A5</del>   | A4             | А3             | A2         | A1            |

| <b>0</b> 40 | 20         | <b>A7</b>     | <del>A6</del>  | <b>A</b> 5 .    | <b>A</b> 4     | A3             | Ã2         | ĀT            |

| 042         | <b>2</b> 2 | Ā7            | Ā6             | <b>A</b> 5      | <del>A4</del>  | <del>Ã</del> 3 | AZ         | A1            |

| 044         | 24         | <del>A7</del> | Ā6             | <b>A</b> 5      | <del>A4</del>  | Ā3             | <b>A</b> 2 | A1            |

| 046         | 26         | <b>A7</b>     | <del>Ā6</del>  | A5              | <del>A</del> 4 | A3             | A2         | A1            |

| <b>0</b> 50 | 28         | <del>Ā7</del> | Ā6             | A5              | <del>A4</del>  | АЗ             | A2         | <del>A1</del> |

| 052         | 2A         | <b>A</b> 7    | <del>A6</del>  | A5              |                | АЗ             | A2         | A1            |

| 054         | 20         | <b>A7</b>     | `A6            | <b>A</b> 5      | <del>A4</del>  | <b>A</b> 3     | A2         | TA            |

| 056         | 2 E        | <b>A7</b>     | <del>Ā6</del>  | <b>A</b> 5      | Ā4             | А3             | A2         | A1            |

| 060         | 3 <i>0</i> | A7            | <b>A6</b>      | A5              | A4             | <b>A3</b>      | <u>A2</u>  | ĀT            |

|                  | •      |                |               |                |                |                       |                 |               |

|------------------|--------|----------------|---------------|----------------|----------------|-----------------------|-----------------|---------------|

| ADDRESS<br>OCTAL |        | I7             | 16            | CONNECT        | TIONS<br>14    | 13                    | 12              | 11            |

| 062              |        | Ā7             | Ā6            | <b>A</b> 5     | A4             | <del>73</del>         | A2              | A1            |

| 064              |        | <b>A7</b>      | <b>A6</b>     | A5             | A4             | <b>Ā</b> 3            | A2              | ĀT            |

| 066              |        | Ā <del>7</del> | Ā6            | A5             | <b>A</b> 4     | <del>A3</del>         | A2.             | Al            |

| 070              |        | <b>A7</b>      | <del>Ā6</del> | A5             | A4             | А3                    | AZ              | ĀT            |

| 072              |        | <b>A7</b>      | <del>Ā6</del> | A5             | A4             | А3                    | Ā2              | A1            |

| 074              |        | <b>A7</b>      | <del>Ā6</del> | <b>A</b> 5     | A4             | Аз                    | A2              | Āī            |

| 076              |        | <b>A7</b>      | <del>A6</del> | <b>A</b> 5     | A4             | А3                    | A2              | A1            |

| 100              |        | A7             | <b>A</b> 6    | Ā5             | Ā <del>4</del> | A3                    | Ā2              | <del>A1</del> |

| 102              |        | <b>A</b> 7     | <b>A</b> 6    | <del>A5</del>  | <del>A4</del>  | A3                    | A2              | A1            |

| 104              |        | <b>A</b> 7     | <b>A6</b>     | Ā5             | Ā4             | A3                    | <b>A</b> 2      | ĀŢ            |

| 106              | •<br>: | <b>A7</b>      | <b>A</b> 6    | Ā5             | <b>A</b> 4     | <del>A3</del>         | A2              | Αĭ            |

| 110              |        | <b>A7</b>      | <b>A</b> 6    | Ā5             | <del>4</del> 4 | A3                    | <b>A</b> 2      | ĀĪ            |

| 112              |        | <b>A7</b>      | A6            | Ā <del>5</del> | <del>A4</del>  | А3                    | <del>A2</del>   | FA.           |

| 114              |        | Ā7             | A6            | <b>A</b> 5     | <del>Ā4</del>  | <b>A</b> 3            | A2              | ĀT            |

| 116              |        | <b>A</b> 7     | A6            | Ā5             | <b>A</b> 4     | А3                    | A2              | ſΑ            |

| 120              |        | <b>A7</b>      | A6            | A5             | A4             | <del>A3</del>         | A2              | AT            |

| 122              |        | <b>A</b> 7     | A6            | A5             | A4             | <b>A</b> 3            | ĀZ              | Al            |

| 124              |        | A7             | A6            | A5             | <b>A4</b>      | Ā3                    | A2              | <del>A1</del> |

| 126              |        | <b>A7</b>      | A6            | Ā5             | A4             | <del>A3</del> .       | <b>A</b> 2      | A1            |

| 130              |        | <b>A7</b>      | <b>A</b> 6    | Ā5             | A4             | А3                    | A2              | ĀĪ            |

| 132              |        | Ā7             | A6            | Ā5             | <b>A</b> 4     | АЗ                    | $\overline{A2}$ | Α1            |

| 134              |        | A7             | <b>A6</b>     | <del>A5</del>  | <b>A</b> 4     | А3                    | A2              | ĀĪ            |

| 136              |        | Ā7             | <b>A</b> 6    | Ā <del>5</del> | A4             | АЗ                    | A2              | Αl            |

| 140              |        | A7             | <b>A</b> 6    | A5             | <del>A4</del>  | <del>A3</del>         | <del>A2</del>   | ĀĪ            |

| 142              |        | <b>A7</b>      | A6            | A5             | <b>A</b> 4     | <u> <del>A</del>3</u> | <del>A2</del>   | Al            |

| `     | ADDRESS |     | CONNECTIONS   |                |                |                |               |               |               |  |  |  |  |

|-------|---------|-----|---------------|----------------|----------------|----------------|---------------|---------------|---------------|--|--|--|--|

|       | OCTAL   |     |               | 16_            | 15             | 14             | 13            | 12            |               |  |  |  |  |

|       | 144     |     | A7            | A6             | <b>A</b> 5     | Ā4             | <del>A3</del> | A2            | A1            |  |  |  |  |

|       | 146     |     | A7            | <b>A</b> 6     | <b>A</b> 5     | <del>A4</del>  | A3            | A2            | <b>A</b> 1    |  |  |  |  |

|       | 150     |     | A7            | A6             | <b>A</b> 5     | <b>A</b> 4     | АЗ            | A2            | <del>A1</del> |  |  |  |  |

|       | 152     |     | Ā7            | <b>A</b> 6     | A5             | <b>A4</b>      | А3            | <b>A</b> 2    | <b>A</b> 1    |  |  |  |  |

|       | 154     |     | <b>A7</b>     | A6             | A5             | <del>A4</del>  | А3            | <b>A</b> 2    | A1            |  |  |  |  |

|       | 156     |     | A7            | A6             | <b>A</b> 5     | <del>A4</del>  | А3            | A2            | <b>A</b> 1    |  |  |  |  |

|       | 160     |     | <b>A7</b>     | <b>A6</b>      | <b>A5</b>      | A4             | <del>A3</del> | <u>A2</u>     | Al            |  |  |  |  |

|       | 162     |     | <b>A7</b>     | A6             | <b>A</b> 5     | A4             | <del>A3</del> | <del>A2</del> | A1            |  |  |  |  |

|       | 164     |     | <b>A7</b>     | <b>A</b> 6     | A5             | A4             | <del>A3</del> | A2            | ĀĪ            |  |  |  |  |

|       | 166     | . • | <b>A7</b>     | <b>A</b> 6     | A5             | A4             | <b>A3</b>     | A2            | Αī            |  |  |  |  |

| (     | 170     |     | <b>A7</b>     | A6             | A5             | A4             | А3            | <del>A2</del> | <u> </u>      |  |  |  |  |

|       | 172     |     | <b>A7</b>     | <b>A</b> 6     | <b>A</b> 5     | A4             | А3            | <del>A2</del> | Αì            |  |  |  |  |

|       | 174     |     | <del>A7</del> | <b>A</b> 6     | <b>A</b> 5     | A4             | АЗ            | <b>A</b> 2    | ĀĪ            |  |  |  |  |

|       | 176     |     | A7            | A6             | A5             | A4             | АЗ            | <b>A</b> 2    | A1            |  |  |  |  |

|       | 200     |     | <b>A</b> 7    | <del>Ā6</del>  | Ā5             | <del>A4</del>  | <del>A3</del> | <del>Ā2</del> | <del>A1</del> |  |  |  |  |

|       | 202     |     | A7            | <del>A6</del>  | <del>A5</del>  | <del>A4</del>  | <del>A3</del> | A2            | Al            |  |  |  |  |

|       | 204     |     | A7            | <b>A6</b>      | Ā5             | <b>A</b> 4     | Ā3            | A2            | ĀΤ            |  |  |  |  |

|       | 206     |     | A7            | Ā <del>6</del> | <del>Ā</del> 5 | <del>A</del> 4 | <del>A3</del> | A2            | <b>A</b> 1    |  |  |  |  |

|       | 210     |     | A7            | Ā6             | A <del>5</del> | <del>4</del> 4 | А3            | ĀŽ            | ĀT            |  |  |  |  |

|       | 212     |     | <b>A</b> 7    | <del>Ā6</del>  | Ā5             | <b>A4</b>      | А3            | A2            | <b>A</b> 1    |  |  |  |  |

|       | 214     |     | A7            | <del>Ā6</del>  | <del>A5</del>  | <del>A4</del>  | А3            | A2            | AT            |  |  |  |  |

|       | 216     |     | A7            | <del>A6</del>  | Ā5             | <del>4</del> 4 | - А3          | A2            | A1            |  |  |  |  |

|       | 220     |     | A7            | <del>Ā6</del>  | Ā5             | <b>A</b> 4     | Ä3            | Ā2            | <del>A1</del> |  |  |  |  |

| . ( - | 222     |     | A7            | <del>A6</del>  | Ā5             | A4             | <b>A</b> 3    | Ā2            | A]            |  |  |  |  |

| ) .   | 224     |     | A7            | <del>A6</del>  | Ā5             | <b>A</b> 4     | <del>Ā3</del> | A2            | ĀΤ            |  |  |  |  |

|       |         |     |               |                |                |                |               |               |               |  |  |  |  |

| ADDRESS<br>OCTAL |            | I6             | CONNECT       | TIONS<br>I4   | 13              | 12            |               |

|------------------|------------|----------------|---------------|---------------|-----------------|---------------|---------------|

| 226              | <b>A</b> 7 | <del>Ā6</del>  | Ā5            | A4            | <del></del> _   | A2            | Al            |

| 230              | A7         | <del>A6</del>  | <del>A5</del> | A4            | А3              | Ā2            | <u> Ā1</u>    |

| 232              | A7         | <b>A</b> 6     | A5            | A4            | АЗ              | <b>A</b> 2    | <b>A</b> 1    |

| 234              | A7         | Ā6             | Ā5            | <b>A</b> 4    | А3              | A2            | <u> </u>      |

| 236              | A7         | <del>A6</del>  | A5            | A4            | А3              | <b>A</b> 2    | Αì            |

| 240              | A7         | Ā6             | <b>A</b> 5    | <b>A</b> 4    | Ā3 <sup>-</sup> | A2            | <del>A1</del> |

| 242              | A7         | Ā6             | A5            | A4            | <del>A3</del>   | <del>A2</del> | Al            |

| 244              | A7         | Ā6             | <b>A</b> 5    | <b>A</b> 4    | <b>A3</b>       | <b>A</b> 2    | Āī            |

| 246              | A7         | <del>Ā6</del>  | A5            | <b>A</b> 4    | Ā3              | A2            | Αì            |

| 250              | A7         | <b>A6</b>      | <b>A</b> 5    | <b>A4</b>     | А3              | A2            | ΆΤ            |

| 252              | A7         | <b>A</b> 6     | A5            | Ā4            | А3              | A2            | A1            |

| 254              | A7         | <del>Ā6</del>  | <b>A</b> 5    | <del>A4</del> | А3              | A2            | ĀΤ            |

| 256              | A7         | <del>A6</del>  | <b>A</b> 5    | <del>A4</del> | А3              | A2            | Αl            |

| 260              | A7         | <del>Ā6</del>  | <b>A</b> 5    | <b>A</b> 4    | A3              | Ā2            | ĀĪ            |

| 262              | A7         | <del>Ā6</del>  | A5            | <b>A</b> 4    | <del>A3</del>   | <u>A2</u>     | A1            |

| 264              | A7         | Ā6             | A5            | A4            | Ā3              | A2            | <del>A1</del> |

| 266              | A7         | ĀG             | A5            | A4            | A3              | A2            | A1            |

| 270              | A7         | Ã <del>6</del> | <b>A</b> 5    | A4            | АЗ              | A2            | ĀT            |

| 272              | A7         | <del>A6</del>  | <b>A</b> 5    | A4            | АЗ              | A2            | Al            |

| 274              | A7         | <del>Ā6</del>  | A5            | A4            | А3              | A2            | ĀŢ            |

| 276              | A7         | <del>Ā6</del>  | <b>A</b> 5    | A4            | АЗ              | A2            | Al            |

| 300              | A7         | A6             | <del>Ā5</del> | <del>Ā4</del> | Ā3              | ĀZ            | ĀĪ            |

| 302              | A7         | A6             | <b>A5</b>     | A4            | <del>A3</del>   | <u>A2</u>     | FA            |

| 304              | A7         | <b>A</b> 6     | Ā5            | <del>A4</del> | Ā3              | A2            | <del>AT</del> |

| 306              | A7         | <b>A</b> 6     | Ā5            | A4            | <del>Ä3</del>   | A2            | ΑΊ            |

| ADDRESS<br>OCTAL | 17         | 16         | CONNECT:        | IONS<br>I4     | 13              | 12         |    |

|------------------|------------|------------|-----------------|----------------|-----------------|------------|----|

| 310              | A7         | A6         | Ā5              | Ā <del>4</del> | A3              | A2         | ĀĪ |

| 312              | A7         | A6         | <b>A</b> 5      | <del>A4</del>  | А3              | A2         | A1 |

| 314              | A7         | <b>A</b> 6 | <b>A</b> 5      | <del>Ā4</del>  | А3              | A2         | ÄΤ |

| 316              | A7         | A6         | Ā5              | <b>A4</b>      | АЗ              | A2         | Αì |

| 320              | A7         | <b>A</b> 6 | Ā <del>5</del>  | A4             | <del>A3</del>   | Ā2         | ĀT |

| 322              | A7         | A6         | Ā5              | A4             | <del>A3</del>   | Ā2         | A1 |

| 324              | A7         | <b>A6</b>  | Ā5              | A4             | <del>A3</del>   | A2         | ĀT |

| 326              | <b>A</b> 7 | <b>A</b> 6 | Ā5 <sup>-</sup> | A4             | <b>A</b> 3      | A2         | A1 |

| 330              | A7         | <b>A</b> 6 | Ā5              | A4             | АЗ              | A2         | AT |

| 332              | · A7       | <b>A</b> 6 | <b>A</b> 5      | A4             | АЗ              | Ā2         | A1 |

| 334              | A7         | <b>A6</b>  | A5              | A4             | А3              | A2         | ΆT |

| 336              | <b>A</b> 7 | <b>A</b> 6 | <b>A</b> 5      | A4             | АЗ              | A2         | Al |

| 340              | A7         | A6         | <b>A</b> 5      | <del>A4</del>  | <del>\</del> \  | Ā2         | Āī |

| 342              | A7         | <b>A</b> 6 | <b>A</b> 5      | <del>A4</del>  | Ā3              | Ā2         | A1 |

| 344              | A7         | <b>A</b> 6 | <b>A</b> 5      | <b>A</b> 4     | <del>A3</del>   | A2         | ĀT |

| 346              | <b>A</b> 7 | <b>A</b> 6 | A5              | <b>A</b> 4     | A3              | A2         | A1 |

| 350              | <b>A</b> 7 | A6         | Ą5              | <del>A</del> 4 | АЗ              | A2         | ĀT |

| 352              | A7         | A6         | A5              | <b>A</b> 4     | А3              | A2         | A1 |

| 354              | A7         | A6         | A5              | <b>A</b> 4     | Аз              | A2         | ĀT |

| 356              | A7         | A6         | <b>A</b> 5      | <b>A</b> 4     | <b>A</b> 3      | A2         | A] |

| 360              | <b>A</b> 7 | A6         | <b>A</b> 5      | A4             | <del>A3</del>   | Ā2         | ĀT |

| 362              | A7         | <b>A</b> 6 | <b>A</b> 5      | A4             | <b>A</b> 3      | Ā2         | ΑΊ |

| 364              | A7         | <b>A</b> 6 | A5              | A4             | <del>A3</del>   | A2         | AT |

| 366              | <b>A</b> 7 | <b>A</b> 6 | A5              | A4             | <del>7</del> 43 | A2         | A1 |

| 370              | A7         | <b>A</b> 6 | <b>A</b> 5      | A4             | Аз              | <b>A</b> 2 | ĀT |

: 4 •

5

| ADDRESS |          | C          | ONNECTI    | ONS       |    |    |    |   |

|---------|----------|------------|------------|-----------|----|----|----|---|

| OCTAL   | <u> </u> | 16         | 15         | 14        | 13 | 12 | IJ | _ |

| 372     | A7       | <b>A</b> 6 | <b>A</b> 5 | A4        | A3 | A2 | Al |   |

| 374     | . A7     | A6         | <b>A</b> 5 | <b>A4</b> | А3 | A2 | ΆT |   |

| 376     | A7       | <b>A6</b>  | A5         | A4        | АЗ | A2 | Αl |   |

#### I/O BAUD RATE SELECTION CHART

| BAUD RATE | 11 | 10  | 9_  | 8 | PRESET | COU<br>6 | INT<br>5 | 4 | 3 | 2 | _ 1 | 0 |

|-----------|----|-----|-----|---|--------|----------|----------|---|---|---|-----|---|

| 110       | 1  | 0   | 1   | 1 | 1      | 0        | 0        | 1 | 0 | 0 | 0   | 0 |

| 150       | 1  | . 1 | . 0 | 0 | 1      | 0        | 1        | 1 | 1 | 1 | 1   | 1 |

| 300       | 1  | 1   | 1   | 0 | 0      | 1        | 0        | 1 | 1 | 1 | 1   | 1 |

| 600       | 1  | 1   | 1   | 1 | 0      | 0        | 1        | 1 | 0 | 0 | 0   | 0 |

| 1200      | 1  | . 1 | 1   | 1 | 1      | 0        | 0        | 1 | 1 | 0 | 0   | 0 |

| 2400      | 1  | 1   | 1   | 1 | 1      | 1        | 0        | 0 | 1 | 1 | 0   | 0 |

| 4800      | 1  | 1   | 1   | 1 | 1      | 1        | 1        | 0 | 0 | 1 | 1   | 0 |

| 9600      | 1  | - 1 | 1   | 1 | 1      | 1        | 1        | 1 | 0 | 0 | 1   | 1 |

| 19200     | 1  | 1.  | 1   | 1 | 1      | 1        | 1        | 1 | 1 | 0 | 1   | 0 |

In the above chart, PRESET COUNT pads 0 through 11 correspond to pads 0 to 11 on the right side of the board. The BAUD rate listed on the left can be obtained by wiring pads 0 to 11 as described to the right of the BAUD rate listed, "+V" for 1 and "GND" for 0.

SERIAL I/O BOARD ERRATA

THE FOLLOWING CHART IS TO BE USED INSTEAD OF THE CHART INCLUDED IN THE MANUAL.

1/O BAUD RATE SELECTION CHART

| BAUD RATE |    |     |     |   | PR | RESET | COUNT | • |   |         |   |   |

|-----------|----|-----|-----|---|----|-------|-------|---|---|---------|---|---|

|           | 11 | 10  | 9   | 8 | 7  | 6     | 5     | 4 | 3 | 2       | 1 | 0 |

| 110       | 1  | 0   | 1   | 1 | 1  | 0     | 0     | 1 | 0 | 1       | 0 | 0 |

| 150       | 1  | 1   | 0   | 0 | 1  | 1     | 0     | 0 | 0 | 0       | 1 | 1 |

| 300       | 1  | 1 . | 1   | 0 | 0  | 1     | 1     | 0 | 0 | $0_{J}$ | 1 | 1 |

| 600       | 1  | 1   | 1   | 1 | 0  | 0     | 1     | 1 | 0 | 1       | 0 | 0 |

| 1200      | 1  | 1   | 1   | 1 | 1  | 0     | 0     | 1 | 1 | 1       | 0 | 0 |

| 2400      | 1  | 1   | 1   | 1 | 1  | 1     | 0     | 1 | 0 | 0       | 0 | 0 |

| 4800      | 1  | 1   | ٠٦  | 1 | 1  | 1     | 1     | 0 | 1 | 0       | 1 | 0 |

| 9600      | 1  | 1   | . 1 | 1 | 1  | 1     | 1     | 1 | 1 | 0       | 0 | 0 |

| 19200     | 1  | ì   | . 1 | 1 | 1  | Ţ     | 1     | 1 | 1 | 1       | 1 | 0 |

ON PAGE 4 IN THE THEORY OF OPERATION, THE FORMULA FOR DETERMINING THE "Preset Count Frequency" IS INCORRECT. THE NUMBER "4096" IN THE FORMULA SHOULD BE CHANGED TO 4100.

IN ORDER TO INCREASE THE OVERALL RELIABILITY OF THE 8800 SERIAL TELETYPE I/O BOARD (88-SIO C), A MODIFICATION HAS BEEN ADDED TO RAISE THE VOLTAGE ACROSS THE TELETYPE OUTPUT CONTACTS. THIS MODIFICATION HAS BEEN INSTALLED AT THE FACTORY; THEREFORE, FOLLOW THE ASSEMBLY INSTRUCTIONS DESCRIBED IN THE MANUAL AND ASSOCIATED ERRATA.

TTY

SERIAL I/O BOARD

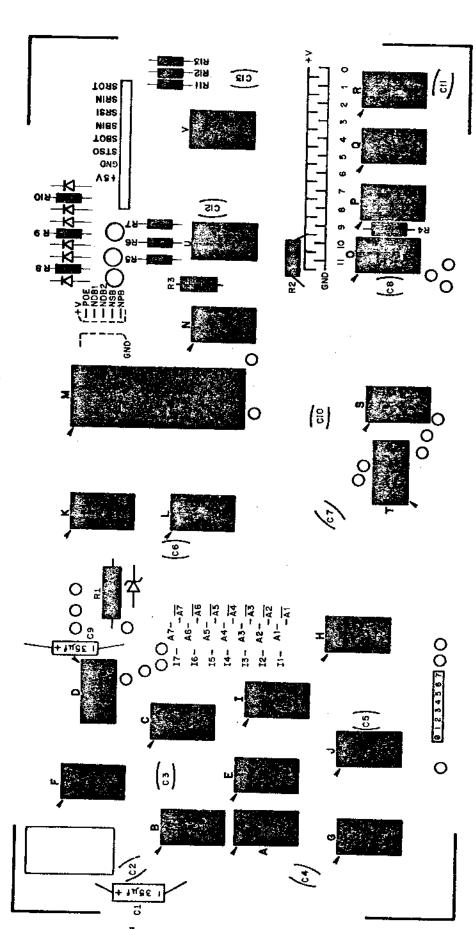

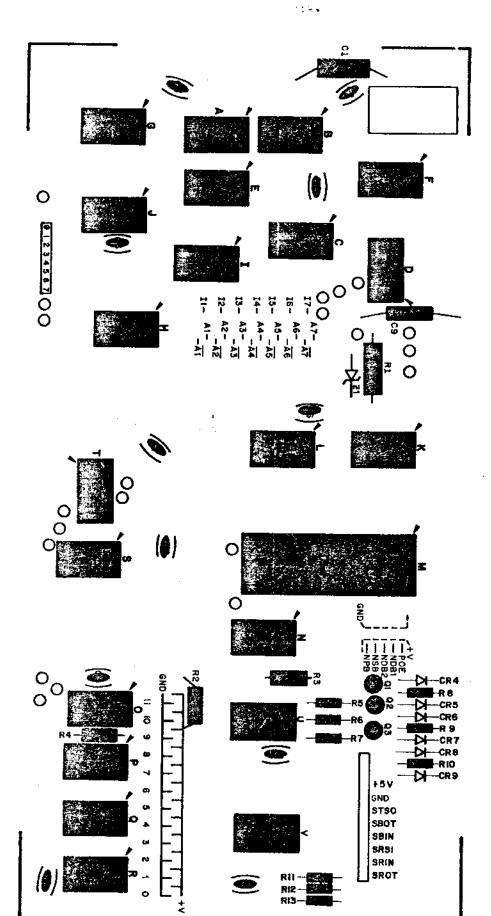

#### 8800 SERIAL I/O C BOARD ASSEMBLY

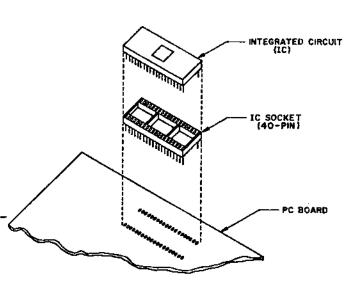

There are 22 integrated circuits (IC's) to be installed on the 8800 Serial I/O C Board. (88-SIOC) One of these, IC M, will be provided with a 40-pin IC socket. IC M itself should not be installed into the socket until the board is completely assembled.

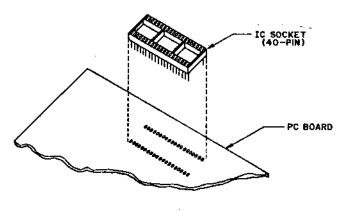

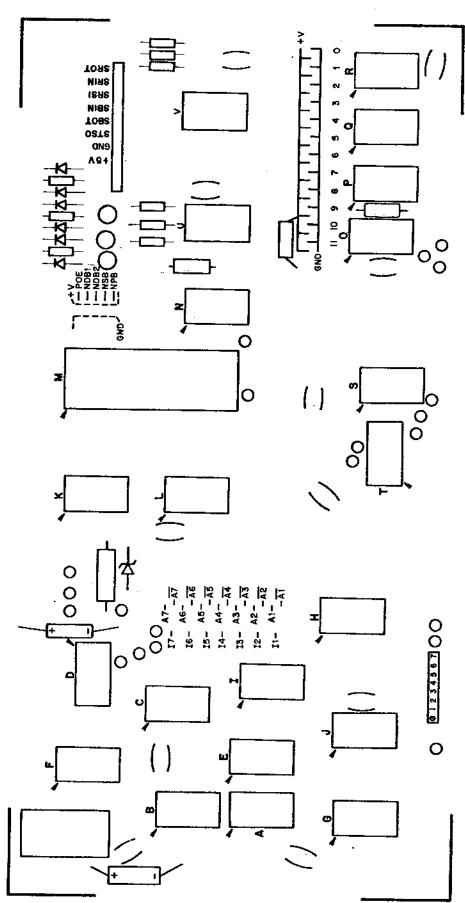

( ) Referring to the component layout, set the 40-pin IC socket included in your kit into place and secure it with a piece of masking tape. (see drawing below)

- ( ) Turn the board over and solder each pin to the foil pattern on the back side of the board. Be sure to solder each pin and be careful not to leave any solder bridges.

- ( ) Turn the board over again and remove the piece of masking tape.

- () Referring to the component layout, remove the IC with the correct part number from its holder. If there are any bent pins, straighten these using needle-nose pliers. Ensure that you chose the IC with the correct part number as you install each one.

( ) Orient the IC so that its notched end is towards the arrowhead printed on the board, and pin 1 of the IC corresponds with the arrowhead itself.

NOTE: If the IC does not have a notch on one end, refer to the IC Orientation Chart included with your manual for the identification of pin 1.

- ( ) When you have the correct orientation, start the pins on one side of the IC into their respective holes on the silk-screened side of the PC board. DO NOT PUSH THE PINS IN ALL THE WAY. If you have difficulty getting the pins into the holes, use the tip of a small screwdriver to guide them.

- () Start the pins on the other side of the IC into their holes in the same manner. When all of the pins have been started, set the IC in place by gently rocking it back and forth until it rests as close as possible to the board. Make sure that the IC is perfectly straight and as close as possible to the board; then tape it in place with a piece of masking tape.

- ( ) Turn the board over and solder each pin to the foil pattern on the back side of the board. Be sure to solder each pin and be careful not to leave any solder bridges.

- ( ) Turn the board over again and remove the piece of masking tape.

Use the same procedure to install each of the IC's. Be sure that you have the correct part number and the correct orientation as you install each one.

- ( ) Install a 40-pin socket for IC M

- ( ) IC's A, B, C, D, F, G and T are 74L00's

- ( ) IC's E and H are 74L04's

- ( ) IC I is a 74L30

- ( ) IC's J and S are 74L02's

- r IC M ( ) IC's K, L and N are 8797's

- ( ) IC 0 1s a 9601 (or 8T22A)

- ( ) IC's P, Q and R are 74L193's

- ( ) IC's U and V are 7404's

#### Resistor Installation

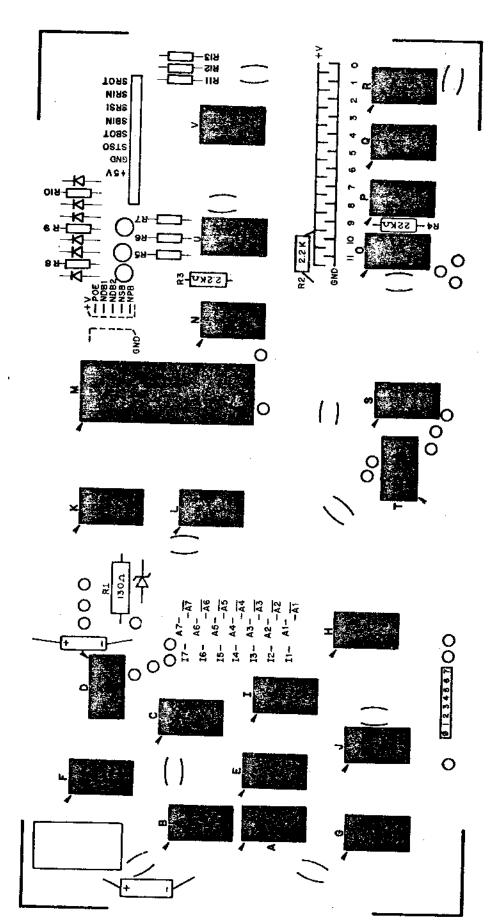

There are 13 resistors to be mounted on the 8800 Serial I/O C Board.

NOTE: Resistors are color-coded according to their value. The resistors in your kit will have four or possibly five bands of color. The fourth band in both cases will be gold or silver, indicating the tolerance. In the following instructions we will be concerned only with the three bands of color to one side of the gold or silver band. Be sure to match these three bands of color with those called for in the instructions as you install each resistor.

Using needle-nose pliers, bend the leads of the following resistors at right angles to match their respective holes on the PC board. (see component layout)

NOTE: All resistors on the 8800 Serial I/O C Board are either 1/4 or 1/2 Watt.

- ( ) Install resistor R1 (130-ohm, brownorange-brown) into the correct holes on the silk-screened side of the PC board.

- ( ) Holding the resistor in place with one hand, turn the board over and bend the two leads slightly outward.

- ( ) Solder the leads to the foil pattern on the back side of the board; then clip off any excess lead lengths.

Referring to the component layout, install the remaining resistors in the same manner. Be sure you have the correct color-coding for each one as you install them.

NOTE: Save all of the component leads that you clip off for use later in the assembly procedure.

- ] ) R1 is 130-ohm (brown-orange-brown)

- ( ) R2 & R3 are 2.2K-ohm (red-red-red)

- ( ) R4 is 22K-ohm (red-red-orange)

- ( ) R5, R6 & R7 are 2.7K-ohm (red-violet-red)

- ( ) R8, R9 & R10 are 390-ohm (orangewhite-brown)

- ( ) Rll, Rl2 & Rl3 are 220-ohm (redred-brown)

#### Capacitor Installation

There are 11 ceramic disk capacitors and 2 electrolytic capacitors to be installed on the 8800 Serial I/O C Board.

11.4

Refer to the component layout and install the ceramic disk capacitors according to the following procedure.

- ( ) Choose the capacitor with the correct value as called for in the instructions. Straighten the two leads as necessary and bend them to fit their respective holes on the PC board.

- ( ) Insert the capacitor into the correct holes from the silk-screened side of the board. Push the capacitor down until the ceramic insulation almost touches the foil pattern.

- ( ) Holding the capacitor in place, turn the board over and bend the two leads slightly outward.

- ( ) Solder the two leads to the foil pattern on the back side of the board; then clip off any excess lead lengths.

Install all of the ceramic disk capacitors in this manner. Be sure that you have the correct value capacitor as you install each one.

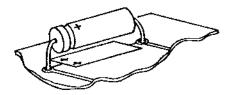

The two electrolytic capacitors for the serial I/O board have polarity requirements which must be noted before installation. Those contained in your kit may have one or possibly two of three types of polarity markings. To determine the correct orientation, look for the following: (see drawing above right)

ELECTROLYTIC CAPACITOR

One type will have plus (+) signs on the positive end; another will have a band or a groove around the positive side in addition to the plus signs. The third type will have an arrow on it; in the tip of the arrow there is a negative (-) sign and the capacitor must be oriented so the arrow points to the negative polarity side.

Referring to the component layout, install the electrolytic capacitors on the board.

- () Bend the two leads of the capacitor with the correct value at right angles to match their respective holes on the board. Insert the capacitor into the holes on the silk-screened side of the board. Be sure to align the positive polarity side with the "+" signs printed on the board.

- ( ) Holding the capacitor in place, turn the board over and bend the two leads slightly outward. Solder the leads to the foil pattern and clip off any excess lead lengths.

- ( ) Install the second electrolytic capacitor in the same manner.

( ) Cl & C9 are 35uf

( ) C2 to C7 and C10 to C13 are .luf

( ) C8 is .001uf

#### Transistor Installation

There are three PNP, EN2907, transistors to be installed on the 8800 Serial I/O C Board.

NOTE: When installing these transistors, ensure that you check the part numbers on them before soldering them into place. Some transistors are identical in physical appearance but differ in electrical characteristics. If the part numbers on your transistors do not match the numbers called for in the instructions, it may be that you have substitutions. In this case, refer to the Transistor Identification Chart included with your manual.

() These transistors are rounded and have a flat edge near one of the leads. The lead nearest this flat edge is called the emitter. The hole for the emitter is the one furthest from the Ql---Q3 markings, inside of the circle beneath the markings. If the emitter lead is placed into this hole, the other two leads should fit into their holes with little or no bending and should not cross over each other. (see drawing below)

- ( ) Orient transistor Q1 (EN2907) so that the lead nearest the flat edge aligns with the correct hole on the board. Insert the transistor into the holes from the silk-screened side of the baord.

- ( ) Holding the transistor in place, turn the board over and bend the three leads slightly outward.

- ( ) Solder the leads to the foil pattern on the back side of the board; then clip off any excess lead lengths.

Referring to the component layout, install the remaining transistors in the same manner. Be sure that you have the correct part number and the correct orientation for each one as you install them.

( ) Q1, Q2 & Q3 are EN2907's

#### Diode Installation

There are six 1N914 diodes and one 12 volt zener diode to be installed on the 8800 Serial I/O C Board.

NOTE: Diodes are marked with a band on one end indicating the cathode end. The diode <u>must be oriented</u> so that the end with the band is towards the band printed on the board when being installed.

- () Referring to the component layout, bend the leads of the zener diode Z1 at right angles to match the correct holes on the board.

- ( ) Insert the diode into the correct holes from the silk-screened side of the board. Turn the board over and bend the two leads slightly outward.

- ( ) Solder the two leads to the foil pattern on the back side of the board; then clip off any excess lead lengths.

Install diodes CR4 through CR9 in the same manner. Be sure that you have the band on the diode aligned with the band printed on the board as you install them. Failure to orient these diodes correctly may result in permanent damage to your unit.

NOTE: Part number designations for these diodes are indicated on the following page.

)CR4 through CR9 are 1N914 diodes

is a 12-volt zener diode

N4004 diodes. If IN914's are supplied

in your kit, use them preferably. be substituted with 1N4002,

The 12-volt zener will be marked

#### Voltage Regulator Installation

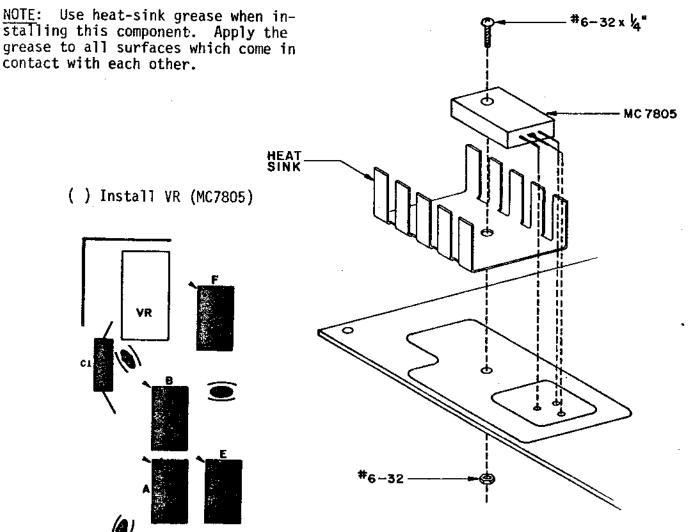

There is one MC7805 5-volt regulator to be installed on the 8800 Serial I/O C Board.

- ( ) Set the MC7805 in place on the board and align the mounting holes. (see drawing)

- ( ) Use a pencil to mark the point on each of the three leads where they line up with their respective holes on the board.

- ( ) Use needle-nose pliers to bend each of the three leads at a right angle on the points where you made the pencil marks.

NOTE: Use heat-sink grease when installing this component. Apply the grease to all surfaces which come in

- ( ) Referring to the drawing, set the regulator and heat sink in place on the silk-screened side of the board. Use the smaller, 6 pronged, heat sink instead of the 8 pronged one shown in the drawing. Secure them as shown, holding the regulator in place as you tighten the nut.

- ( ) Turn the board over and solder the three leads to the foil pattern on the back side of the board. Be sure not to leave any solder bridges.

- ( ) Clip off any excess lead lengths.

See errata sheet

#### Hardwire Connections

There are 33 hardwire connections, with one optional connection, to be made on the 8800 Serial I/O C Board.

. .

The first five connections to be made are near IC M, towards the top right corner of the board. Make these connections using 1 inch wires. Make each connection by inserting the wire from the silk-screened side of the board and soldering it on the back side. Be sure to clip off any excess lead lengths.

- ( ) Connect the pad labeled NSB according to the following information: NSB--to--GND = 1 stop bit NSB--to--+V = 2 stop bits

- ( ) Connect the pads labeled POE and NPB according to the following information:

| <u>NPB</u> | <u> P0E</u> | MODE               |

|------------|-------------|--------------------|

| GND        | GND         | <b>o</b> dd parity |

| GND        | +V          | even parity        |

| +V         | Х           | no parity          |

(X = don't care)

( ) Connect the pads labeled NDBl and NDB2 according to the following information:

| NDB1 | NDB2 | data bits/character |

|------|------|---------------------|

| GND  | GND  | 5                   |

| +V   | GND  | 6                   |

| GND  | +V   | 7                   |

| +٧   | +٧   | 8                   |

There are 9 jumper connections to be made on this board. Make these using 6 inch wires in the same manner as the previous connections with 1 inch wires.

- ( ) Connect pad -V to pad -V

- ( ) Connect pad 0 to pad 0

- ( ) Connect pad I to pad I

- ( ) Connect pad PC to pad PC

- ( ) Connect pad A to pad A

- ( ✓) Connect pad B to pad B

- (∠) Connect pad C to pad C

- ( ) Connect pad G to pad G

- ( ) Connect pad H to pad H

The connections for the address selection and the BAUD rate selection are made with component leads saved from earlier steps in the assembly procedure. Bend the leads as necessary to fit their respective holes on the board and insert them from the silk-screened side. Solder them on the back side of the board and clip off any excess lead lengths.

Refer to the I/O ADDRESS SELECTION CHART and the I/O BAUD RATE SELECTION CHART for the necessary information for making these selections.

NOTE: In the address selection, wire pads II through I7 to Al & Al through A7 & A7 as indicated in the chart to obtain the octal address listed in the left column.

Refer to the Theory of Operation manual for further explanations of these two functions.

Make all hardwire connections as described in the instructions.

#### Vectored Interrupt

This is an optional function on the 8800 system, and need not be used at all. If it is to be used, it must be used in conjunction with the 88-VI vectored interrupt card. There is one exception to this which will be explained towards the end of this section.

The 8800 Serial I/O C Board has provisions for vectored interrupt hardwire connections. This provides the user with the option of selecting a priority level for the input device and the output device, or a single priority level for both. The vectored interrupt offers levels of priority, 0 through 7, with 7 being the highest priority level.

There are three pads at the top of the board labeled "OUT", "IN" and "BH". There are eight pads at the bottom of the board labeled "VI" and numbered 0 through 7. The eight numbered pads correspond to the eight priority levels respectively.

Use 6 inch wires to make these connections in the same manner as the previous jumper connections.

You may connect the "OUT" (output device) pad to some priority level, and the "IN" (input device) pad to some priority level; or you may connect the "BH" (both devices) pad to a desired priority level for both devices. If the "BH" pad is used to set the priority level, the "OUT" and "IN" pads should not be used.

( ) Connect the vectored interrupt priority level as desired per the information above.

It is possible to obtain a <u>single</u> level of interrupt priority on this board without the necessity of the 88-VI vectored interrupt card.

This may be used only on one of the I/O cards in your system, and only one of the three pads ("OUT", "IN" and "BH") can be used to make the connection.

- ( ) You will observe three small pads to the right of the pad labeled "I" near IC H. In between these three is a larger pad with no designation.

- () For a single level of priority interrupt, connect a jumper wire between the <u>larger</u> pad described above and the <u>desired</u> pad at the top of the board. Remember, only one of the 3 pads "OUT", "IN" and "BH" may be used and only one I/O board may be connected in this manner.

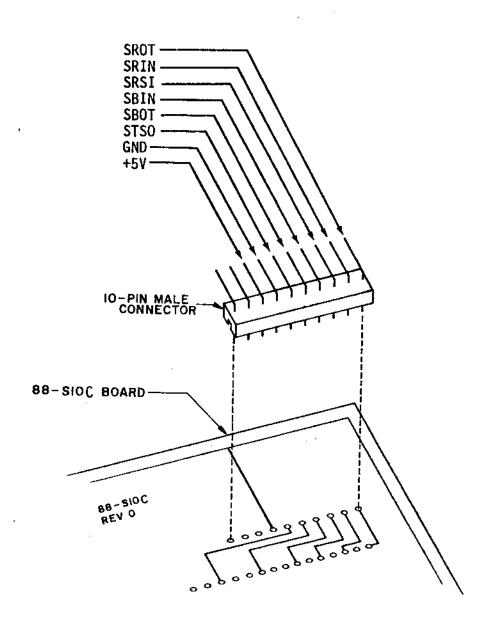

# Wafer Connector Installation

There is one 10-pin male connector to be installed on the 8800 Serial I/O C Board.

- () Referring to the drawing below, insert the 10-pin wafer connector into the correct holes on the board from the silk-screened side. Be sure to insert the side with the shorter, straight pins.

- ( ) Holding the connector in place, turn the board over and solder the 10 pins to the foil pattern on the back side of the board.

#### Board Installation

- ( ) IC M may now be installed into its socket on the 8800 Serial I/O C board. Do this very carefully and remember this is a MOS integrated circuit and very sensitive to static electricity.

- () Refer to page 64 in the assembly manual "EXPANDER BOARD 8800 M/BD ASSEMBLY" and install the edge connector provided with the board according to the procedure described there.

- () Press the 8800 Serial I/O C Board into the edge connector just installed. The board should be oriented the same way as the other boards already installed; i.e. the silkscreened side should be facing the right side of the unit viewed from the front panel.

### SERIAL I/O BOARD ERRATA

# READ THIS BEFORE PERFORMING ANY ASSEMBLY OPERATIONS!

MODIFICATION FOR INTERNAL HARDWARE INTERRUPT (for devices with no external "handshake" capability)

THIS MODIFICATION APPLIES TO REVISION O BOARDS ONLY.

Consult the Theory of Operation section of your manual for the description of the interrupt connection to the Bus and the description of the interrupt Enable-Disable.

Perform the following operations if the internal hard-ware interrupt capability is desired.

- ( ) Cut the PC land which connects Pin 19 to Pin 7 of 10 M.

- ( ) Cut the PC land which connects Pin 22 to Pin 11 of IC M. (Make this cut as close as possible to Pin 22.)

- (\*) Cut the PC land which connects Pins 3 & 4 of IC F to Pin 1 of IC C.

- (v) Cut the PC land which connects Pins 10 & 11 of IC F to Pin 9 of IC C.

- () Do not connect jumper H as instructed in the manual. Connect the pad labeled H just below IC M to pin 11 of IC T with a jumper wire.

- ( ) Connect a jumper wire from Pin 19 of IC M to Pin 9 of IC C.

- (c) Connect a jumper wire from Pin 22 of IC M to Pin 13 of IC C.

BE CAREFUL WHEN MAKING THESE MODIFICATIONS THAT YOU DO NOT CUT THE WRONG LANDS, AND THAT YOU DO NOT CREATE ANY SHORTS WHEN MAKING THE JUMPER CONNECTIONS.

SERIAL I/O SCHEMETIC

REV 1

SERIAL RS-232 INTERFACE

REV O only

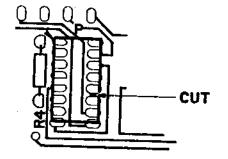

### SERIAL I/O PC BOARD MODIFICATION

The following modifications must be performed on the serial I/O boards.

BEFORE INSTALLING IC P, THERE IS A LAND CONNECTING PINS 11 & 12 WHICH MUST BE REMOVED.

Do this by making a cut, on the silk-screened side of the board, at the point where the land touches each of the two pads for pins 11 & 12. Then heat the land between the two cuts with your soldering iron and the piece of land will lift off easily. (see drawing below)

SILK-SCREENED SIDE OF PC BOARD

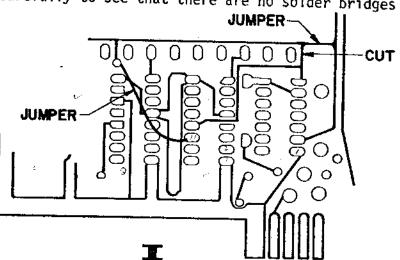

ON THE BACK SIDE OF THE BOARD (NON SILK-SCREENED SIDE) THERE IS ANOTHER PIECE OF LAND TO BE REMOVED, AND TWO JUMPERS TO BE ADDED. DO THIS AFTER PERFORMING THE ABOVE, AND AFTER INSTALLING IC P.

Referring to the drawing below, cut the vertical land at the point indicated in the drawing. Make the two cuts in the same manner as above and about 1/16 inch apart, and remove the land. Be sure to make the cuts between the two horizontal land as shown in the drawing.

Connect two jumper wires between the two lands shown in the drawing near the cut just made and between pin 11 of IC P and the small pad shown in the drawing. Be very careful when installing these two jumpers not to short any of the connections to any other pins or to any of the other lands. After completing these connections, check them over very carefully to see that there are no solder bridges or shorts.

20, )

#### SERIAL I/O BOARD ERRATA SHEET

There is one jumper connection to be made on the back of the board between one of the pads for jumper "G" and a PC land running next to it.

Locate the two pads below capacitor C9 that are labeled "A" and "G". They are located just above the address jumper pads. On the back side (non silk-screened side) of the board there is a PC land which runs between these two pads.

When installing jumper wire G, do not install this end of the jumper in the normal manner.

Insert the wire for jumper G into the hole labeled "G" just below capacitor C9 from the silk-screened side of the board. DO NOT SOLDER IT AT THIS TIME.

Holding the wire in place, turn the board over and bend the end of the wire protruding through the hole so that it lays over the land described above. Be sure that the wire does not touch any other lands and does not short over to pad "A".

Now solder the wire to pad "G" and to the land itself. Be careful not to create any solder bridges; make sure that the wire connects only pad "G" and the land.

The opposite end of jumper wire "G" should be connected in the normal manner.

PAGE 5 OF THE SERIAL I/O BOARD ASSEMBLY PROCEDURE IS TO BE CHANGED AS FOLLOWS:

THE RESISTOR BETWEEN IC 0 & IC P (R25 on the SIO A, R4 on the SIO B & SIO C) IS TO BE CHANGED FROM 22K-ohms to 7.5K-ohms, violet-green-red.

#### \*\*\*SERIAL I/O BOARD ASSEMBLY MANUAL ERRATA\*\*\*

THE FOLLOWING INFORMATION IS IN REFERENCE TO THE "HARDWIRE CONNECTIONS" SECTION OF THE I/O MANUAL ( Page 12 in the SIO A & C, Page 10 in the SIO B).

THERE ARE FIVE PADS TO BE OPTIONALLY CONNECTED TO EITHER GROUND OR +V. THE DESIGNATIONS PRINTED ON THE BOARD, POE, NDB1, NDB2, NSB AND NPB, REFER TO THE ENTIRE HORIZONTAL GROUP OF THREE PADS TO THE RIGHT OF IC M. THE PADS CLOSEST TO IC M ARE THE ONES TO BE CONNECTED TO EITHER THE SECOND VERTICAL GROUP OF FIVE PADS (GND) OR THE THIRD VERTICAL GROUP OF FIVE PADS (+V). THE POE, NDB1, NDB2, NSB AND NPB PADS THEMSELVES ARE THE FIVE PADS RUNNING VERTICALLY DIRECTLY NEXT TO IC M.