## WESTERN DIGITAL

### WD1691 FLOPPY SUPPORT LOGIC (F.S.L.)

#### **FEATURES**

- Direct interface to the FD179X

- Eliminates external FDC Logic

- Data Separation/RCLK GENERATION

- Write Precompensation Signals

- VFOE/WF Demultiplexing

- Programmable Density

- 8" or 5.25" Drive Compatible

- All inputs and outputs TTL Compatible

- Single +5V Supply

#### **GENERAL DESCRIPTION**

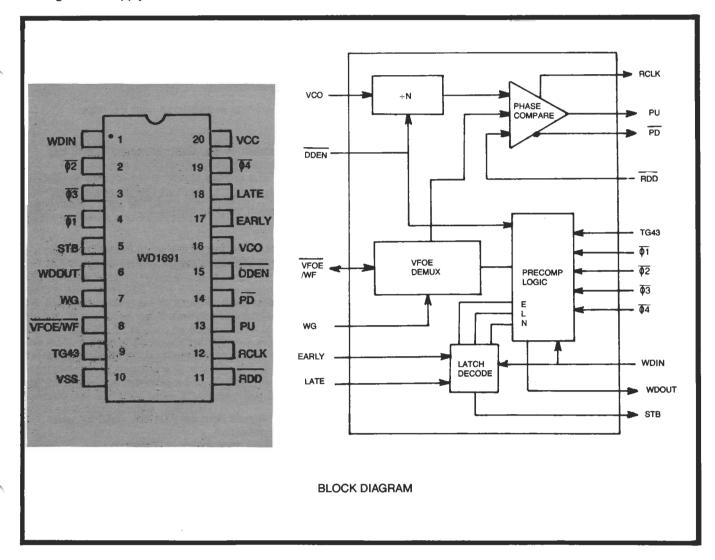

The WD1691 F.S.L. has been designed to minimize the external logic required to interface the 179X Family of Floppy Disk Controllers to a drive. With the use of an external VCO, the WD 1691 will generate the RCLK signal for the WD179X, while providing an adjustment pulse (PUMP) to control the VCO frequency. VFOE/WF de-multiplexing is also accomplished and Write Precompensation signals have been included to interface directly with the WD2143 Clock Generator.

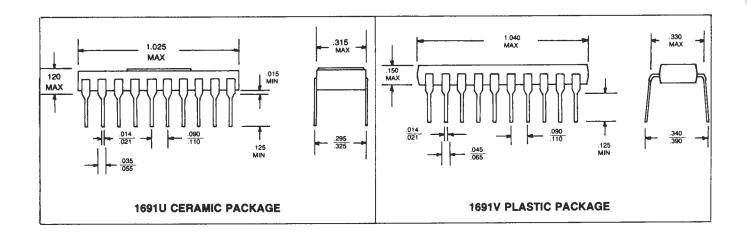

The WD1691 is implemented in N-MOS silicon gate technology and is available in a plastic or ceramic 20 pin dual-in-line package.

| PIN        | NAME                                | SYMBOL          | FUNCTION                                                                                                                                       |

|------------|-------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | WRITE DATA<br>INPUT                 | WDIN            | Ties directly to the FD179X WD pin.                                                                                                            |

| 2, 3, 4,19 | PHASE<br>2, 3, 1, 4                 | ₫2 ቒ3 ቒ1 ቒ4     | 4 Phase inputs to generate a desired Write Precompensation delay. These signals tie directly to the WD2143 Clock Generator.                    |

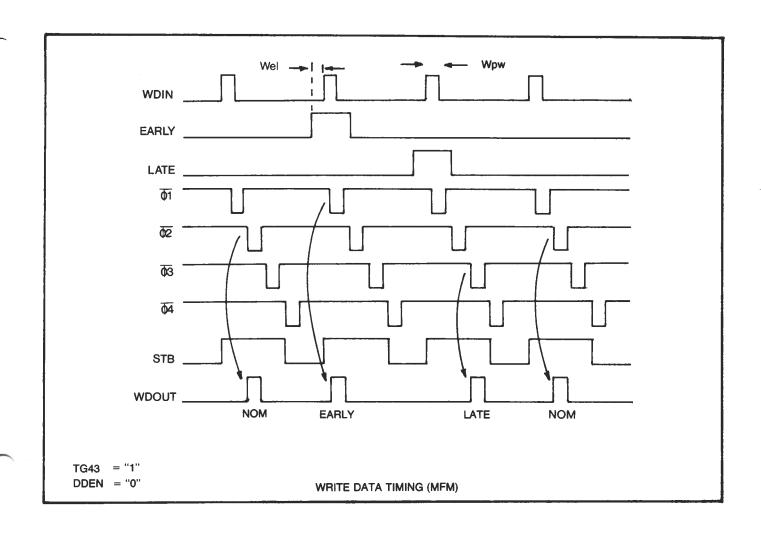

| 5          | STROBE                              | STB             | Strobe output from the 1691. Strobe will latch at a high level on the leading edge of WDIN and reset to a low level on the leading edge of 04. |

| 6          | WRITE DATA<br>OUTPUT                | WDOUT           | Serial, pre-compensated Write data stream to be sent to the disk drive's WD line.                                                              |

| 7          | WRITE GATE                          | WG              | Ties directly to the FD179X WG pin.                                                                                                            |

| 8          | VFO ENABLE/<br>WRITE FAULT          | VFOE/WF         | Ties directly to the FD179X VFOE/WF pin.                                                                                                       |

| 9          | TRACK 43                            | TG43            | Ties directly to the FD179X TG43 pin, If Write Precompensation is required on TRACKS 44-76.                                                    |

| 10         | V <sub>ss</sub>                     | V <sub>ss</sub> | Ground                                                                                                                                         |

| 11         | READ DATA                           | RDD             | Composite clock and data stream input from the drive.                                                                                          |

| 12         | READ CLOCK                          | RCLK            | RCLK signal generated by the WD1691, to be tied to the FD179X RCLK pin.                                                                        |

| 13         | PUMP UP                             | PU              | Tri-state output that will be forced high when the WD1691 requires an increase in VCO frequency.                                               |

| 14         | PUMP DOWN                           | PD              | Tri-state output that will be forced low when the WD1691 required a decrease in VCO frequency.                                                 |

| 15         | Double Density<br>Enable            | DDEN            | Double Density Select input. When Inactive (High), the VCO frequency is internally divided by two.                                             |

| 16         | Voltage<br>Controlled<br>Oscillator | vco             | A nominal 4.0MHz (8" drive) or 2.0MHz (5.25" drive) master clock input.                                                                        |

| 17, 18     | EARLY<br>LATE                       | EARLY<br>LATE   | EARLY and LATE signals from the FD179X, used to determine Write Precompensation.                                                               |

| 20         | V <sub>cc</sub>                     | V <sub>cc</sub> | + 5V ± 10% power supply                                                                                                                        |

|            |                                     |                 |                                                                                                                                                |

#### **DEVICE DESCRIPTION**

The WD1691 is divided into two sections:

- 1) Data Recovery Circuit

- 2) Write precompensation Circuit

The Data Separator or Recovery Circuit has four inputs: DDEN, VCO, RDD, and VFOE/WF; and three outputs: PU, PD and RCLK. The VFOE/WF input is used in conjunction with the Write Gate signal to enable the Data recovery circuit. When Write Gate is high, a write operation is taking place, and the data recovery circuits are disabled, regardless of the state on any other inputs.

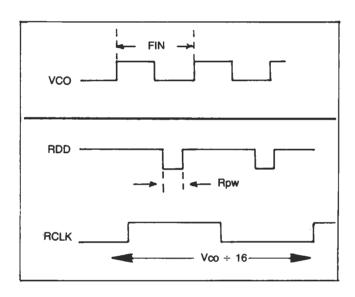

When VFOE/WF and WRITE GATE are low, the data recovery circuit is enabled. When the RDD line goes Active Low, the PU or PD signals will become active. If the RDD line has made its transition in the beginning of the RCLK window, PU will go from a HI-Z state to a Logic I, requesting an *increase* in VCO frequency. If the RDD line has made its transition at the end of the RCLK window, PU will remain in a HI-Z state while PD will go to a logic zero, requesting a decrease in VCO frequency. When the leading edge of RDD occurs in the center of the RCLK window, both PU and PD will remain tri-stated, indicating that no adjustment of the VCO frequency is needed. The RCLK signal is a divide-by-16 (DDEN=1) or a divide-by-8 (DDEN=0) of the VCO frequency.

| WG          | VFOE/WF     | RDD         | PU+PD                          |

|-------------|-------------|-------------|--------------------------------|

| 1<br>0<br>0 | X<br>1<br>0 | X<br>X<br>1 | HI-Z<br>HI-Z<br>HI-Z<br>Enable |

The Write Precompensation circuit has been designed to be used with the WD2143-01 clock generator. When the WD1691 is operated in a "single density only" mode, write precompensation as well as the WD2143-01 is not needed. In this case, \$\overline{0}1\$, \$\overline{0}2\$, \$\overline{0}3\$, \$\overline{0}4\$, and STB should be tied together, \$\overline{DDEN}\$ left open, and TG43 tied to ground.

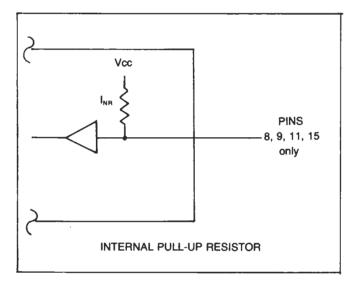

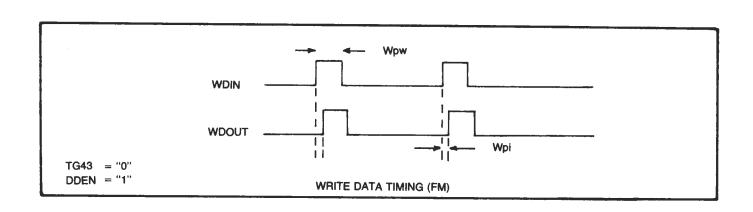

In the double-density mode ( $\overline{DDEN}=0$ ), the signals Early and Late are used to select a phase input ( $\sqrt[4]{1}-\sqrt[4]{4}$ ) on the leading edge of WDIN. The STB line is latched high when this occurs, causing the WD2143-01 to start its pulse generation.  $\sqrt[4]{2}$  is used as the write data pulse on nominal (Early=Late= $\sqrt[4]{4}$ ),  $\sqrt[4]{2}$  is used for early, and  $\sqrt[4]{3}$  is used for late. The leading edge of  $\sqrt[4]{4}$  resets the STB line in anticipation of the next write data pulse. When TG43=0 or  $\overline{DDEN}=1$ , Precompensation is disabled and any transitions on the WDIN line will appear on the WDout line. If write precompensation is desired on all tracks, leave TG43 open (an internal pull-up will force a Logic I) while  $\overline{DDEN}=0$ .

The signals, DDEN, TG43, and RDD have internal pullup resistors and may be left open if a logic I is desired on any of these lines. The minimum Voh level on PU is specified at 2.4V, sourcing 200ua. During PUMP UP time, this output will "drift" from a tri-state to .4V minimum. By tying PU and PD together, a PUMP signal is created that will be forced low for a decrease in VCO frequency and forced high for an increase in VCO frequency. To speed up rise times and stabilize the output voltage, a resistor divider can be used to set the tristate level to approximately 1.4V. This yields a worst case swing of  $\pm$  1V; acceptable for most VCO chips with a linear voltage-to-frequency characteristic.

Both PU and PD signals are affected by the width of the RAW READ (RDD) pulse. The wider the RAW READ pulse, the longer the PU or PD signal (depending upon the phase relationship to RCLK) will remain active. If the RAW READ pulse exceeds 250ns. (VCO = 4MHz, DDEN = 0) or 500ns. (VCO = 4MHz, DDEN = 1), then both a PU and PD will occur in the same window. This is undesirable and reduces the accuracy of the external integrator or low-pass filter to convert the PUMP signals into a slow moving D.C. correction voltage.

Eventually, the PUMP signals will have corrected the VCO input to exactly the same frequency multiple as the RAW READ signal. The leading edge of the RAW READ pulse will then occur in the exact center of the RCLK window, and ideal condition for the FD179X internal recovery circuits.

#### - SPECIFICATIONS -

#### **ABSOLUTE MAXIMUM RATINGS**

| Ambient Temperature under Bias  | -25° to 70°C  |

|---------------------------------|---------------|

| Voltage on any pin with respect |               |

| to Ground (vss)                 | . −0.2 to +7V |

| Power Dissipation               | 1W            |

Storage Temp.—Ceramic—65°C to +150°C Plastic—55°C to +125°C

NOTE: Maximum limits indicate where permanent device damage occurs. Continuous operation at these limits is not intended and should be limited to those conditions specified in the DC Electrical characteristics.

#### DC ELECTRICAL CHARACTERISTICS

$T_A = \oint to 70^{\circ}C; V_{CC} = 5.0V \pm 10\%; V_{ss} = OV$

| SYMBOL          | PARAMETER                 | MIN | TYP | MAX  | UNIT | TEST CONDITIONS        |

|-----------------|---------------------------|-----|-----|------|------|------------------------|

| V <sub>IL</sub> | Input Low Voltage         | 0.2 |     | +0.8 | V    |                        |

| V <sub>IH</sub> | Input High Voltage        | 2.0 |     |      | v    |                        |

| V <sub>OL</sub> | Output Low Voltage        |     |     | 0.45 | V    | I <sub>OL</sub> =3.2MA |

| V <sub>OH</sub> | High Level Output Voltage | 2.4 |     |      | V    | $I_{OH} = -200\mu a$   |

| V <sub>cc</sub> | Supply Voltage            | 4.5 | 5.0 | 5.5  | V    |                        |

| Icc             | Supply Current            |     | 40  | 100  | MA   | All outputs open       |

#### **AC ELECTRICAL CHARACTERISTCS**

$T_A = 0^{\circ}$  to 70°C;  $V_{cc} = 5V \pm 10\%$ ; Vss = OV

| SYMBOL          | PARAMETER                 | MIN | TYP | MAX | UNIT | TEST CONDITIONS |

|-----------------|---------------------------|-----|-----|-----|------|-----------------|

| FIN             | VCO Input Frequency       | .5  | 4   | 6   | MHz  | DDEN=0          |

| İ               |                           | .5  | 2   | 6   | MHz  | DDEN=1          |

| Rpw             | RDD Pulse Width           | 100 | 200 |     | ns.  |                 |

| W <sub>et</sub> | EARLY (LATE) to WDIN      | 100 |     |     | ns.  |                 |

| Pon             | PUMP UP/DN Time           | 0   |     | 250 | ns.  |                 |

| $W_{pi}$        | WDIN to WDOUT             |     |     | 80  | ns.  | DDEN=1          |

| I <sub>NR</sub> | Internal Pull-up Resistor | 4.0 | 6.5 | 10  | ΚΩ   |                 |

#### TYPICAL APPLICATIONS

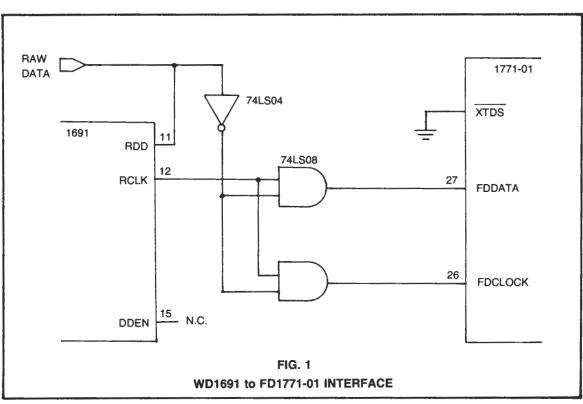

Figure 1 illustrates the 1691 to FD1771-01 floppy disk controller. The RCLK signal is used to gate the RAW data pulses which are inverted by the 74LS04 inverter. Since RCLK will be high during data and low during clock a 74LS08 is used to switch the proper clock or data pulse to the FD1771.

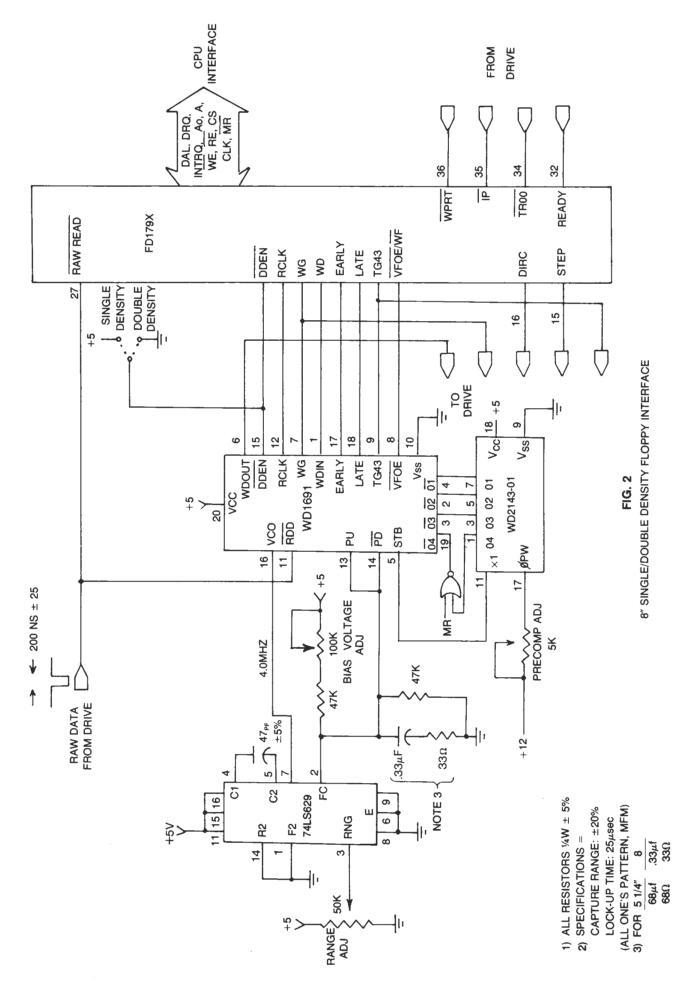

Shown in Figure 2 is a Phase-Lock Loop data separator and the support logic for a single and double-density 8" drive. The raw data (Both clock and data bits) are fed to the WD1691 and FD179X. The WD1691 outputs its PU or PD signal, which is integrated by the .33uf capacitor and 33ohm resistor to form a control voltage for the 74S124 VCO device. The 4.0MHZ nominal output of the VCO then feeds back to the WD1691 completing the loop. The WD2143-01 is also used, providing write precompensation when in double-density, from tracks 44-77. The DDEN line can either be controlled by a toggle switch or a logic level from the host system.

To adjust write precompensation, issue a command to the FD179X so that write data pulses are present. This can be done with a 'WRITE TRACK' command and the IP line open, or a continuous 'WRITE SECTOR' operation. With a scope on pin 4 of the WD1691, adjust the precomp pot for the desired value. This will range from 100 to 300 ns typically. The pulse width set on pin 4 (\$1\$) will be the desired precomp delay from nominal.

The data separator must be adjusted with the RDD or VFOE/WF line at a Logic I. Adjust the bias voltage potentiometer for 1.4V on pin 2 of the 74S124. Then adjust the range control to yield 4.0MHZ on pin 7 of the 74S124.

#### SUBSTITUTING VCO's

There are other VCO circuits available that may be substituted for the 74S124. The specifications required are:

- 1) The VCO must free run at 4.0MHz with a 1.4V control signal. The WD1691 will force this voltage 1 Volt in either direction (i.e., .4V = decrease frequency, 2.4V = increase frequency). If a ± 15% capture range is desired, then a 1 Volt change on the VCO input should change the frequency by 15%. Capture range should be limited to about ± 25%, to prevent the VCO from breaking into oscillation and/or losing lock because of noise spikes (causing abnormally quick adjustments of the VCO frequency). Jitter in the VCO output frequency may further be reduced by increasing the integration capacitor/resistor, but this will also decrease the final capture range and lock-up time.

- 2) The sink output current of the WD1691 is 3.2ma minimum. The source output current is -200ua. Therefore, source current is the limiting factor. Insure that the input circuitry of the VCO does not require source current in excess of -200ua.

Another alternative is to use a voltage follower/level shifter circuit to match the input requirements of the VCO chosen. A more complex filter can be used to convert the PUMP UP/PUMP DOWN pulses to the varying DC voltage signal required by the VCO, achieving an optimum condition between lock-up time and high frequency rejection.

This is a preliminary specification with tentative device parameters and may be subject to change after final product characterization is completed.

Information furnished by Western Digital Corporation is believed to be accurate and reliable. However, no responsibility is assumed by Western Digital Corporation for its use; nor any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Western Digital Corporation. Western Digital Corporation reserves the right to change said circuitry at any time without notice.

# This Document was scanned and contributed by:

Barry A. Watzman