# The BIOS Companion

Phil Croucher

#### Legal Bit

This book and any included software is sold as is without warranty of any kind, either express or implied, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. Neither the Author, the Publisher nor its dealers or distributors assumes any liability for any alleged or actual damages arising from their use. **Translation**: Although this information has been gathered from original manufacturer's details or practical experience, it is always changing, or scarce, so there could be technical inaccuracies or typographical errors. As a result, changes will be made to the information in this book and included software without reference to anyone, and we don't guarantee that the product suits your purposes. As well, no liability is accepted for loss of data or business or damage to equipment as a result of using the information contained herein - backups are your responsibility!

# Copyrights, etc

Windows, Windows '95, Windows NT, DOS and Xenix are trademarks and Microsoft is a registered trademark of Microsoft Corporation. Novell and NetWare are registered trademarks of Novell, Inc. Macintosh is a registered trademark of Apple Computer, Inc. VAX is a trademark of Digital Equipment Corporation. 8086, 80286, i386, i486, i486DX, i486DX2, i486DX4, i486SX, and i487SX, Intel OverDrive Processor are trademarks of Intel Corp. UNIX is a registered trademark of UNIX System Laboratories. IBM, PC, XT, AT and OS/2 are trademarks of International Business Machines Corp. PCI is a registered trademark of PCI Special Interest Group. Triton is a trademark of a company in Germany. Any code listings, although obtained from sites that are publicly accessed, may be copyrighted by their respective manufacturers. All other proprietary trade names, trademarks and names protected by copyright are fully acknowledged. They are mentioned for editorial purposes, with no intention of infringing them.

This book copyright © 1986-2004 Phil Croucher. ISBN 0-9681928-0-7

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without prior written permission from the author.

Notice is hereby given that the name PHILIP ANDREW CROUCHER, in capital letters, or any variation thereof, is claimed by Phil Croucher, which name may not be used without permission.

#### Sources

Which are gratefully acknowledged:

- Experience.

- Many conversations with technicians.

- Hundreds of motherboard manuals, not all of which were helpful!

- · AMI BIOS Tech Ref manual.

- · MR BIOS Tech Ref Manual. Thanks to Mike at Microid Research!

- Readers, including Mick O'Donnell, Martyn Smith, Chris Crook, Chris Nicholson, Dart Computers, Pat Tan, John Dallman, Ulf Boehlau, Rick and Tilman at ProData, Adrian Clint of Samsung, Peter Farrow, Kerry and Toni at Award Software, Chuck French at Unicore, Ali Kiafar at ECS/TTX, John Dann at ProData, Jerome Czeikus and Mike Echlin.

- amibios.txt, available from Jean-Paul Rodrigue in the University of Montreal, which had useful snippets, especially

the explanation of Fast Decode.

- amisetup, a shareware program from Robert Muchsel.Copyrights, etc.

#### Praise For The BIOS Companion

"The computer book of the month is The Bios Companion by Phil Croucher. Long-time readers of this column will recall I have recommended his book before. This tells you everything you ought to know about the BIOS in your system. Post codes, options, upgrades, you name it. Years ago, I called an earlier edition of this invaluable and I see no reason to change my view. Recommended."

Jerry Pournelle, Byte Magazine

"You will find more information about your motherboard assembled here than I have ever seen."

#### Frank Latchford PCCT

"Thank! I really appreciated this. I read it and was able to adjust my BIOS settings so that my machine runs about twice as fast. Pretty impressive. Thanks again."

Tony

"This book is worth far more than is charged for it. Very well written. Probably the most-used reference book in my shop. ....a great value as the feature explanations trigger your thinking and allow you to figure out many related BIOS features in some of the newer versions."

#### Amazon reader

"For those who need or want to fine tune, or simply understand, the basic and advanced features of their PC's BIOS, this book is an invaluable guide. It has a very broad range and covers both fundamental and more advanced topics as well as issues specific to particular bios types (AMI, PHOENIX, etc.) and versions. This is one book you need to have as a PC technician and a valuable resource for trouble shooting and configuring your personal PC even if your not."

#### Amazon reader

"I found The Bios companion so useful that I "just have" to have all 3 books in the set. The extra Bios Companion is going to a friend who will gain great benefit from it. Yes I definitely want all three books. Thank you very much."

#### Mike Reinbolt

"I received my package today containing the BIOS Companion book and 2 CD set.... I'm really impressed with what I did receive. I already had about HALF of the information, and to get THAT much, I had to get several books and web pages. GOOD JOB!!

I had more time to go thru the book and think that you should change the word "HALF" to "FOURTH".

I commend you on the great job you did. That's a hell of a lot of work for any major company to do, let alone an individual."

#### Craig Stubbs

"I thoroughly enjoyed my purchase! The BIOS Companion is worth the cost just for the beep-code section alone. I am new to computers and have found the book and your site to be quite informative."

#### pcworker

"I thought the BIOS Companion was quite good. Just chock full of the kind of info I had been looking for. First book I've gotten that was worth the more than price I paid."

Tony

"While you are appreciative of my order, I am likewise appreciative of your efforts to make such a reference available. BIOS's are the most mysterious things in the computing world to figure out. I realize the BIOS manufactures have made great effort to provide detailed information in the BIOS help (F1) (ok, so that's a bit of sarcasm). Traditionally, I have had to piece bits of information together that I have found at various locations. Once again thanks."

#### Brian Presson, System Engineer

"The Bios companion is an absolute must for anyone who builds or configures PC's! It is by far worth the money you pay for it. Phil Croucher has done a superb job! He explains in great detail all of the settings that even most PC technicians have no idea of what they do or effect, and mostly some very helpful suggestions on system settings as well. An Absolute Must have!"

Larry Stark, LPG Computers

Memphis, TN

"I purchased the 2000 edition of the complete The BIOS Companion - PDF from DigiBuy today. Any way you look at it, the information contained is well worth the \$15 dollar investment. I must personally thank you for publishing such a wonderful resource for techies such as myself. Thank you again for all of the hard work."

Sincerely, Boyd Stephens

"I spent two hours going through the different sections therein. Everything is there and I can only say, 'AWSOME'."

Robert, San Francisco

"Hi, Phil

The book is absolutely phenomenal!! - Congratulations! This is exactly the kind of reference many people (including our instructors) need - everything in one place, beautifully organised, crammed full of essential, UNDERSTANDABLE, info."

Alain Hendrikse, South Africa

"Your BIOS guide I had from 1994 was one of those 'never throw it away' items that I knew I would need an update for."

Adrian Clint

# Contents

| 1 | The BIOS                            | 1  |

|---|-------------------------------------|----|

|   | BIOS Data Area                      | 2  |

|   | What Happens When You Switch On     | 13 |

|   | How old is my BIOS?                 | 13 |

|   | Identifying Your BIOS               | 14 |

|   | What's in my machine (using debug)? | 37 |

|   | Where Can I Get A New BIOS?         | 40 |

|   | Flash BIOS Upgrades                 | 40 |

|   | Recovering A Corrupt BIOS           | 43 |

|   | DMI                                 | 44 |

|   | Facilities Provided                 | 44 |

| 2 | The Motherboard                     | 47 |

|   | The Central Processor               | 49 |

|   | Chip Reference Chart                | 63 |

| 3 | Memory                              | 67 |

|   | Static RAM                          | 6  |

|   | Dynamic RAM                         | 6  |

|   | Wait states                         | 69 |

|   | Shadow RAM                          | 70 |

|   | Random Access Memory                | 77 |

|   | CMOS Memory Map                     | 83 |

|   | Numbers On Chips                    | 87 |

| 4 | Bus Types                           | 90 |

|   | ISA                                 | 90 |

|   | EISA                                | 93 |

|   | Micro Channel Architecture          | 91 |

|   | Local Bus                           | 93 |

|   | PCMCIA                              | 93 |

|   | USB                                 | 94 |

|   | FireWire                            | 95 |

#### **CONTENTS**

| 5  | Expansion Cards            | 95  |

|----|----------------------------|-----|

|    | Direct Memory Access (DMA) | 95  |

|    | Base Memory Address        | 98  |

|    | Base I/O Address           | 99  |

|    | Interrupt Setting          | 101 |

| 6  | Performance                | 105 |

| 7  | Open Sesame                | 107 |

|    | Setup Programs             | 108 |

| 8  | Softmenu Setup             | 109 |

| 9  | Standard CMOS Setup        | 111 |

|    | Settings                   | 111 |

| 10 | Advanced CMOS Setup        | 119 |

|    | Settings                   | 119 |

| 11 | Advanced Chipset Setup     | 133 |

|    | Refresh                    | 134 |

|    | Data Bus                   | 139 |

|    | Cacheing                   | 152 |

|    | Memory                     | 164 |

|    | Miscellaneous              | 193 |

| 12 | VGA BIOS                   | 207 |

|    | AGP                        | 207 |

| 13 | Power Management           | 217 |

| 14 | Plug and Play/PCI          | 233 |

|    | ESCD                       | 234 |

|    | PCI Identification         | 234 |

|    | PCI Slot Configuration     | 256 |

# CONTENTS •

| 15 | Peripheral Setup       | 289                                |

|----|------------------------|------------------------------------|

|    | System Monitor Setup   | 298                                |

| 16 | Nasty Noises           | 301                                |

|    | ALR                    | 301                                |

|    | Ambra                  | 301                                |

|    | AMI                    | 301                                |

|    | AST                    | 302                                |

|    | Award                  | 307                                |

|    | Compaq                 | 308                                |

|    | Dell (Phoenix)         | 311                                |

|    | IBM                    | 312                                |

|    | MR BIOS                | 313                                |

|    | Mylex/Eurosoft<br>NEC  | 313<br>314                         |

|    | Packard Bell           | 315                                |

|    | Phoenix                | 315                                |

|    | Quadtel                | 316                                |

|    | Tandon                 | 316                                |

|    |                        |                                    |

| 17 | Error Messages & Codes | 317                                |

|    | AMI                    | 317                                |

|    | AST                    | 319                                |

|    | Award                  | 320                                |

|    | HP Vectra              | 322                                |

|    | Olivetti               | 324                                |

|    | Phoenix                | 325                                |

| 18 | Post Codes             | 327                                |

|    |                        | What is a POST Diagnostic Card?328 |

|    | ACER                   | 329                                |

|    | ALR                    | 330                                |

|    | Ambra                  | 331                                |

|    | AMI                    | 331                                |

|    | Arche Technologies     | 354                                |

|    | AST                    | 356                                |

|    | AT&T                   | 358                                |

|    | Award                  | 364                                |

|    | Chips and Technologies | 388                                |

|    | Compaq                 | 391                                |

#### **CONTENTS**

| Dell                       | 396 |

|----------------------------|-----|

| DTK                        | 398 |

| Eurosoft                   | 399 |

| Faraday A-Tease            | 399 |

| Headstart                  | 399 |

| HP                         | 400 |

| IBM                        | 406 |

| Intel                      | 411 |

| Landmark                   | 426 |

| Magnavox                   | 427 |

| Micronics                  | 427 |

| MR BIOS                    | 428 |

| Mylex/Eurosoft             | 434 |

| NCR                        | 435 |

| Olivetti                   | 438 |

| Packard Bell               | 443 |

| Philips/Magnavox/Headstart | 443 |

| Phoenix                    | 444 |

| Quadtel                    | 457 |

| SuperSoft                  | 459 |

| Tandon                     | 460 |

| Tandy                      | 464 |

| Wyse                       | 464 |

| Zenith                     | 464 |

THE BIOS

he instructions that turn a PC into a useful machine come in three stages, starting with application programs, which are loaded by an operating system, which in turn is loaded by a bootstrap loader in the BIOS (the Basic Input/Output System). There are several in a PC, a good example being the one on the video card that controls the interface between it and the computer. However, we are concerned with the System BIOS, which is a collection of assembly language routines that allow programs and the components of a PC to communicate with each other at low level. It therefore works in two directions at once and is active all the time your computer is switched on. In this way, software doesn't have to talk to a device directly, but can call a BIOS routine instead. However, the BIOS is quite an Achilles Heel and can produce many incompatibilities, so these days it is often bypassed by 32-bit software (DOS relied on it totally) - some functions have migrated to the operating system, starting with Power Management (see ACPI), but NT and W2K have long been replacing BIOS Code with their own Hardware Abstraction Layer (HAL) in the Shadowed ROM area traditionally used by the BIOS after the machine has started.

LinuxBIOS is an Open Source project aimed at replacing it with a little hardware initialization and a compressed Linux kernel that can be booted from a cold start (inside 3 seconds at last count). Linux, once bootstrapped, does not make use of BIOS calls, as it has all the low level hardware drivers itself. In addition, a "trusted BIOS" is being developed that can be included in any system that requires high assurance, such as NetTop. Some access to the Video BIOS is also allowed by some manufacturers.

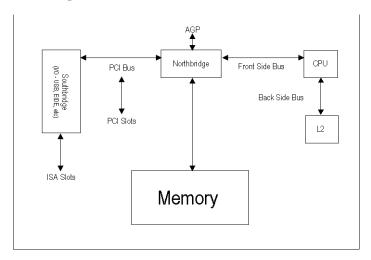

For the moment, though, the System BIOS will work in conjunction with the chipset, which is really what manages access to system resources such as memory, cache and the data buses, and actually is the subject of this book, as all those advanced settings relate to the chipset and not the BIOS as such.

On an IBM-compatible, you will find the BIOS embedded into a ROM on the motherboard, together with hard disk utilities and a CMOS setup program, although this will depend on the manufacturer (the BIOS and CMOS are separate items). The ROM will usually occupy a 64K segment of upper memory at F000 in an ISA system, and a 128K segment starting at E000 with EISA or similar. It's on a chip so it doesn't get damaged if a disk fails, as sometimes used to happen on the Victor 9000/Sirius, which had the BIOS and system on the boot floppy.

Older machines, such as 286s, will have two ROMs, labelled *Odd* and *Even*, or *High* and *Low* (they must be in the right slots), because of the 16-bit bus, but these days there tends to be only one-look for one with a printed label (older 386s sometimes had 4). You can get away with one because BIOS code is often copied into Shadow RAM (explained later), and not actually executed from ROM, but from extended memory. In addition, much of the code is redundant once the machine has started, and it gets replaced by the operating system anyway. Some newer machines may actually have two single-chip BIOSes, so if one fails, the back-up kicks in. Well, in theory, anyway - there have been reports of the BIOSes flashing each other out, so later backups have become read-only.

A *Flash ROM* allows you to change BIOS code without replacing chip(s). Flash ROM, or *programmable read-only nonvolatile RAM*, if you want to be posh, is similar to the EEPROM, being a storage medium that doesn't need a continuous power source, but deals with several blocks of memory at once, rather than single bytes, making it slightly faster, but only just. Also, Flash devices can be programmed in situ, whereas EEPROMS need a special device.

Older BIOSes used EPROMs, which require ultra violet light to erase them, so were a more permanent solution. Even older BIOSes used PROMs, which can't be changed at all once programmed. All are *nonvolatile*, which means that they don't need a continuous source of power to keep information in them. Actually, this does include CMOS chips, as the power referred to is mains and not battery power, but the A+ exam might not agree.

#### **BIOS DATA AREA**

As well as ROM space, the BIOS takes 256 bytes of low memory as a *BIOS Data Area*, which contains details about the Num Lock state, keyboard buffer, etc. DOS, or whatever, loads higher than this, so it's quite safe. When power is applied, the BDA is created at memory location 0040:0000h. Here is what's in it:

| Hex | Dec | Service | Size    |

|-----|-----|---------|---------|

| 00h | 0   | Int 14h | 2 bytes |

| 02h | 2   | Int 14h | 2 bytes |

| 04h | 4   | Int 14h | 2 bytes |

| 06h | 6   | Int 14h | 2 bytes |

| 08h | 8   | Int 17h | 2 bytes |

| 0Ah | 10  | Int 17h | 2 bytes |

| 0Ch | 12  | Int 17h | 2 bytes |

| 0Eh | 14  | POST    | 2 bytes |

| 10h | 16  | Int 11h | 2 bytes |

#### Function

Base I/O address for serial port 1 (COM 1)

Base I/O address for serial port 2 (COM 2)

Base I/O address for serial port 3 (COM 3)

Base I/O address for serial port 4 (COM 4)

Base I/O address for parallel port 1 (LPT 1)

Base I/O address for parallel port 2 (LPT 2)

Base I/O address for parallel port 3 (LPT 3)

Base I/O address for parallel port 4 (LPT 4)

Equipment Word

```

Bits 15-14 - parallel ports installed

00b = 1 parallel port

01b = 2 parallel ports

03b = 3 parallel ports

Bits 13-12 are reserved

Bits 11-9 - serial ports installed

000b = none

001b = 1 serial port

002b = 2 serial ports

003b = 3 serial ports

004b = 4 serial ports

Bit 8 is reserved

Bit 7-6 - floppy drives installed

0b = 1 floppy drive

1b = 2 floppy drives

Bits 5-4 - video mode

00b = EGA or later

01b = color 40x25

10b = color 80x25

```

11b = monochrome 80x25

| Hex                      | Dec                  | Service                    | Size                                   | Function  Bit 3 is reserved  Bit 2 - PS/2 mouse  0b = not installed  1b = installed  Bit 1 - math coprocessor  0b = not installed  1b = installed  Bit 0 - boot floppy  0b = not installed  1b = installed                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------|----------------------|----------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12h<br>13h<br>15h<br>17h | 18<br>19<br>21<br>22 | POST<br>Int 12h<br>Int 16h | 1 byte<br>2 bytes<br>2 bytes<br>1 byte | Interrupt flag - Manufacturing test Memory size in Kb Error codes for AT+; Adapter memory size Keyboard shift flags 1  Bit 7 - Insert  0b = Insert off 1b = Insert on  Bit 6 - CapsLock 0b = CapsLock off 1b - CapsLock on  Bit 5 - NumLock 0b = NumLock off 1b = NumLock on  Bit 4 - ScrollLock 0b = ScrollLock off 1b = ScrollLock off 1b = ScrollLock on  Bit 3 - Alt key 0b = Alt key is up 1b = Alt key is down  Bit 2 - Control key 0b = Control key is down  Bit 1 - Left Shift key is up 1b = Left Shift key is down  Bit 0 - Right Shift key 0b = Right Shift key is up |

| 18h                      | 23                   | Int 16h                    | 1 byte                                 | 1b = Right Shift key is down Keyboard shift flags 2  Bit 7 - Insert key 0b = Insert key is up 1b = Insert key is down Bit 6 - CapsLock 0b = CapsLock is key is up 1b = CapsLock key is down Bit 5 - NumLock key is down Bit 5 - NumLock key 0b = NumLock key is up 1b = Numlock key is down  Bit 4 - ScrollLock key 0b = ScrollLock key is up 1b = ScrollLock key is down Bit 3 - Pause key 0b = pause key is inactive 1b = Pause key is active Bit 2 - SysReg key 0b = SysReg key is up 1b = SysReg key is down                                                                 |

|            | _        |                    |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|----------|--------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hex        | Dec      | Service            | Size             | Function  Bit 1 - Left Alt key  0b = Left Alt key is up  1b = Left Alt key is down  Bit 0 - Right Alt key  0b = Right Alt key is up  1b = Right Alt key is down                                                                                                                                                                                                                                                                                                                             |

| 19h        | 24       | Int 09h            | 1 byte           | Alt Numpad work area                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1Ah        | 26       | Int 16h            | 2 bytes          | Pointer - next character in keyboard buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1Ch        | 28       | Int 16h            | 2 bytes          | Pointer - last character in keyboard buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1Eh        | 60       | Int 16h            | 32 bytes         | Keyboard buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3Eh        | 61       | Int 13h            | 1 byte           | Floppy disk drive calibration status                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|            |          |                    |                  | Bits 7-4 are reserved Bit 3 = floppy drive 3 (PC, XT) Bit 2 = floppy drive 2 (PC, XT) Bit 1 = floppy drive 1 Bit 0 = floppy drive 0 0b not calibrated                                                                                                                                                                                                                                                                                                                                       |

|            |          |                    |                  | 1b calibrated                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3Fh        | 62       | Int 13h            | 1 byte           | Floppy disk drive motor status                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|            |          |                    |                  | Bit 7 - current operation  0b = read or verify operation 1b = write or format operation Bit 6 is not used Bit 5-4 - drive select  00b = Drive 0  01b = Drive 1  10b = Drive 2 (PC, XT)  11b = Drive 4 (PC, XT)  Bit 3 - drive 3 motor 0b = motor off 1b = motor on Bit 2 - drive 2 motor 0b = motor off 1b = motor off |

| 40h<br>41h | 63<br>64 | Int 13h<br>Int 13h | 1 byte<br>1 byte | Floppy disk drive motor time-out Floppy disk drive status Bit 7 - drive ready status 0b = drive ready 1b = drive not ready (time out) Bit 6 - seek status 0b = no seek error detected 1b = seek error detected Bit 5 - floppy disk controller test 0b = floppy disk controller passed 1b = floppy disk controller failed                                                                                                                                                                    |

| Hex        | Dec      | Service            | Size             | Function  Bit 4-0 error codes  00000b = no errors  00001b = illegal function requested  00010b = address mark not found  00011b = write protect error  00100b = sector not found  00110b = diskette change line active  01000b = DMA overrun  01001b = DMA boundary error  01100b = unknown media type  10000b = CRC error during read                                                                                                                                                                                                                                                                                                                         |

|------------|----------|--------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 42h        | 65       | Int 13h            | 1 byte           | Hard disk and floppy controller status register 0  Bit 7-6 - the interrupt code  00b = command completed normally 01b = abnormal termination 10b = abnormal termination, ready on, diskette changed 11b = seek command not completed Bit 5 - seek command not completed 1b = seek command completed 1b = seek command completed Bit 4 - drive fault 0b = no drive fault 1b = drive fault Bit 3 - drive ready 0b = drive ready 1b = drive not ready Bit 2 - head state when interrupt occurred 00b = drive 0 01b = drive 1 10b = drive 2 (PC, XT) 11b = drive 3 (PC, XT) Bit 1-0 indicates drive select 00b = drive 0 01b = drive 1 10b = drive 1 10b = drive 2 |

| 43h        | 66       | Int 13h            | 1 byte           | 11b = drive 3 (PC, XT)  Floppy drive controller status register 1  Bit 7, 0b = no error  1b = access beyond last cylinder  Bit 6, 0b = not used  Bit 5, 1b = CRC error during read  Bit 4, 1b = DMA overrun  Bit 3, 0b = not used  Bit 2, 1b = Sector not found or read ID fail  Bit 1, 1b = medium write protected  Bit 0, 1b = missing address mark                                                                                                                                                                                                                                                                                                          |

| 44h        | 67       | Int 13h            | 1 byte           | Floppy drive controller status register 2 Bit 7, 0b = not used Bit 6, 1b = deleted data address mark Bit 5, 1b = CRC error detected Bit 4, 1b = wrong cylinder Bit 3, 1b = condition of equal during verify Bit 2, 1b = sector not found during verify Bit 1, 1b = bad cylinder Bit 0, 1b = address mark not found on read                                                                                                                                                                                                                                                                                                                                     |

| 45h<br>46h | 68<br>69 | Int 13h<br>Int 13h | 1 byte<br>1 byte | Floppy disk controller: cylinder number<br>Floppy disk controller: head number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 47h        | 70       | Int 13h            | 1 byte           | Floppy disk controller: sector number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 48h 71 49h 72 Int 10h 1 byte Active video mode setting 4Ah 74 Int 10h 2 bytes Textoolumns per row for the active video mode 4Ch 76 Int 10h 2 bytes Textoolumns per row for the active video mode 4Eh 78 Int 10h 2 bytes Size of active video in page bytes 5Dh 80 Int 10h 2 bytes Cursor position for video page 1 5Dh 82 Int 10h 2 bytes Cursor position for video page 1 5Dh 84 Int 10h 2 bytes Cursor position for video page 2 5Dh 85 Sh 86 Int 10h 2 bytes Cursor position for video page 2 5Dh 86 Sh 10h 10h 2 bytes Cursor position for video page 3 5Dh 87 Sh 90 Int 10h 2 bytes Cursor position for video page 3 5Dh 90 Int 10h 2 bytes Cursor position for video page 4 5Dh 90 Int 10h 2 bytes Cursor position for video page 5 5Dh 92 Int 10h 2 bytes Cursor position for video page 6 5Dh 96 Int 10h 2 bytes Cursor position for video page 6 5Dh 97 Int 10h 1 byte Cursor position for video page 7 5Dh 90 Int 10h 1 byte Cursor position for video page 7 5Dh 90 Int 10h 1 byte Active video page 9 5Dh 90 Int 10h 1 byte Active video page 9 5Dh 90 Int 10h 1 byte Active video page 9 5Dh 90 Int 10h 1 byte Active video page 9 5Dh 90 Int 10h 1 byte Active video page 9 Int 10h 1 byte Active video page 1 Int 10h                                                                                                                                                                                                                                                                                                          | Hex  | Dec | Service | Size    | Function                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|---------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 49h       72       Int 10h       1 byte       Active video mode setting         4Ah       74       Int 10h       2 bytes       Textcolumns per row for the active video mode         4Ch       76       Int 10h       2 bytes       Size of active video in page bytes         4Eh       78       Int 10h       2 bytes       Offset address of active video page 1         50h       80       Int 10h       2 bytes       Cursor position for video page 2         52h       82       Int 10h       2 bytes       Cursor position for video page 1         54h       84       Int 10h       2 bytes       Cursor position for video page 2         56h       86       Int 10h       2 bytes       Cursor position for video page 3         58h       88       Int 10h       2 bytes       Cursor position for video page 4         5Ch       92       Int 10h       2 bytes       Cursor position for video page 5         5Ch       92       Int 10h       2 bytes       Cursor position for video page 7         62h       97       Int 10h       1 byte       Active video from the video display adapter video page 10         65h       100       Int 10h       1 byte       Active video from the video page 10         65h       100 <td></td> <td></td> <td>Service</td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |     | Service |         |                                                                                                                                                                                                                                                                                               |

| 4Ah 74 Int 10h 2 bytes Size of active video in page bytes 4Eh 78 Int 10h 2 bytes Size of active video in page bytes 4Eh 78 Int 10h 2 bytes Offset address of active video page relative to start of video RAM 50h 80 Int 10h 2 bytes Cursor position for video page 0 52h 82 Int 10h 2 bytes Cursor position for video page 1 54h 84 Int 10h 2 bytes Cursor position for video page 2 56h 86 Int 10h 2 bytes Cursor position for video page 3 58h 88 Int 10h 2 bytes Cursor position for video page 3 58h 90 Int 10h 2 bytes Cursor position for video page 4 56h 90 Int 10h 2 bytes Cursor position for video page 4 56h 91 Int 10h 2 bytes Cursor position for video page 5 56h 92 Int 10h 2 bytes Cursor position for video page 6 56h 96 Int 10h 2 bytes Cursor position for video page 7 60h 96 Int 10h 2 bytes Cursor position for video page 7 60h 97 Int 10h 1 byte Cursor position for video page 8 61h 99 Int 10h 1 byte Video display adapter Video display adapter Wideo display adapter Wideo display adapter Internal mode register 61h 100 Int 10h 1 byte Video display adapter internal mode register 61h 100 Int 10h 1 byte Video display adapter internal mode register 61h 100 Int 10h 1 byte Video display adapter internal mode register 61h 101 Int 10h 1 byte Video display adapter internal mode register 61h 101 Int 10h 1 byte Video display adapter internal mode register 61h 101 Int 10h 1 byte Video display adapter internal mode register 61h 101 Int 10h 1 byte Video display adapter internal mode register 61h 101 Int 10h 1 byte Video display adapter internal mode register 61h 101 Int 10h 1 byte Video display adapter internal mode register 61h 101 Int 10h 1 byte Video display adapter internal mode register 61h 101 Int 10h 1 byte Video display adapter internal mode register 61h 101 Int 10h 1 byte Video display adapter internal mode register 61h 101 Int 10h 1 byte Video display adapter internal mode register 61h 101 Int 10h 1 byte Video display adapter internal mode register 61h 101 Int 10h 1 byte Video display adapter internal mode register 61h 10h 10h 10h  |      |     | Int 10h | ,       | ,                                                                                                                                                                                                                                                                                             |

| 4Ch 76 Int 10h 2 bytes Offset address of active video page relative to start of video RAM  50h 80 Int 10h 2 bytes Cursor position for video page 1  54h 82 Int 10h 2 bytes Cursor position for video page 1  54h 84 Int 10h 2 bytes Cursor position for video page 1  55h 86 Int 10h 2 bytes Cursor position for video page 2  56h 86 Int 10h 2 bytes Cursor position for video page 3  58h 88 Int 10h 2 bytes Cursor position for video page 4  5Ah 90 Int 10h 2 bytes Cursor position for video page 5  5Ch 92 Int 10h 2 bytes Cursor position for video page 5  5Ch 92 Int 10h 2 bytes Cursor position for video page 6  5Eh 94 Int 10h 2 bytes Cursor position for video page 7  60h 96 Int 10h 2 bytes Cursor position for video page 7  60h 97 Int 10h 1 byte Active video page  63h 99 Int 10h 2 bytes I/O port address for the video display adapter of the video display adapter |      |     |         | ,       | · ·                                                                                                                                                                                                                                                                                           |

| ## AEh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |     |         | •       | •                                                                                                                                                                                                                                                                                             |

| 50h       80       Int 10h       2 bytes       Cursor position for video page 0         52h       82       Int 10h       2 bytes       Cursor position for video page 1         54h       84       Int 10h       2 bytes       Cursor position for video page 2         56h       86       Int 10h       2 bytes       Cursor position for video page 3         58h       88       Int 10h       2 bytes       Cursor position for video page 4         5Ah       90       Int 10h       2 bytes       Cursor position for video page 5         5Ch       92       Int 10h       2 bytes       Cursor position for video page 6         5Eh       94       Int 10h       2 bytes       Cursor position for video page 7         60h       96       Int 10h       2 bytes       Cursor position for video page 7         62h       97       Int 10h       1 byte       Active video page 9         65h       100       Int 10h       1 byte       Video display adapter internal mode register         8it 5       0b = attribute bit background intensity 1b = attribute bit background intensity 1b = attribute bit background intensity 1b = attribute bit patces or patcental 1b = video signal enabled         8it 2 - color operation 1b = monochrome operation 1b = monochrome operation 1b = monochrome operation 1b = monochrome operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |     |         | ,       | Offset address of active video page relative to start                                                                                                                                                                                                                                         |

| 52h 82 Int 10h 2 bytes Cursor position for video page 1 54h 84 Int 10h 2 bytes Cursor position for video page 2 56h 86 Int 10h 2 bytes Cursor position for video page 3 58h 88 Int 10h 2 bytes Cursor position for video page 4 5Ah 90 Int 10h 2 bytes Cursor position for video page 5 5Ch 92 Int 10h 2 bytes Cursor position for video page 6 5Eh 94 Int 10h 2 bytes Cursor position for video page 7 60h 96 Int 10h 2 bytes Cursor shape 62h 97 Int 10h 1 byte Active video page 63h 99 Int 10h 2 bytes I/O port address for the video display adapter 65h 100 Int 10h 1 byte Video display adapter internal mode register 65h 100 Int 10h 1 byte Video display adapter internal mode register 65h 100 Int 10h 1 byte Video display adapter internal mode register 65h 100 Int 10h 1 byte Video display adapter internal mode register 65h 100 Int 10h 1 byte Video display adapter internal mode register 65h 100 Int 10h 1 byte Video display adapter internal mode register 65h 100 Int 10h 1 byte Video display adapter internal mode register 65h 10 = attribute bit background intensity 65h 10 = attribute bit controls blinking 65h 15 - mode 6 graphics operation 66h 15 - mode 27 attribute bit background ober on the monochrome operation 66h 101 Int 10h 1 byte Color paette 67h 101 Int 10h 1 byte Color paette 67h 102 Bit 7, 0b = not used 67h 103 Int 10h 1 byte Color paette 67h 103 Adapter ROM offset address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 50h  | 80  | Int 10h | 2 bytes |                                                                                                                                                                                                                                                                                               |

| 54h 84 Int 10h 2 bytes Cursor position for video page 2 56h 86 Int 10h 2 bytes Cursor position for video page 3 58h 88 Int 10h 2 bytes Cursor position for video page 4 5Ah 90 Int 10h 2 bytes Cursor position for video page 5 5Ch 92 Int 10h 2 bytes Cursor position for video page 6 5Eh 94 Int 10h 2 bytes Cursor position for video page 6 6Ch 97 Int 10h 1 byte Cursor shape 6Ch 97 Int 10h 1 byte Active video page 6Sh 99 Int 10h 2 bytes I/O port address for the video display adapter 6Sh 100 Int 10h 1 byte Video display adapter internal mode register  Bit 7, 0b = not used Bit 5 0b = attribute bit background intensity 1b = attribute bit controls blinking Bit 4, 1b = mode 6 graphics operation Bit 3 - video signal disabled 1b = video signal enabled  Bit 2 - color operation 0b = color operation 0b = color operation 1b = monochrome operation Bit 0, 1b = mode 4/5 graphics operation Bit 0, 1b = mode 4/5 graphics operation Bit 0, 1b = mode 5 foreground color 0b = green/red/yellow 1b = cyan/magenta/white Bit 4 - background color 0b = normal background color 1b = intensified border color (mode 2) 2 and background color (mode 5) Bit 2 - red Bit 1 - green Bit 0 - blue  67h 103 2 bytes Adapter ROM offset address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      | 82  | Int 10h | ,       |                                                                                                                                                                                                                                                                                               |

| 56h 86 Int 10h 2 bytes Cursor position for video page 3 58h 88 Int 10h 2 bytes Cursor position for video page 4 5Ah 90 Int 10h 2 bytes Cursor position for video page 5 5Ch 92 Int 10h 2 bytes Cursor position for video page 6 5Eh 94 Int 10h 2 bytes Cursor position for video page 7 60h 96 Int 10h 1 byte Cursor shape 62h 97 Int 10h 1 byte Active video page 63h 99 Int 10h 2 bytes I/O port address for the video display adapter 65h 100 Int 10h 1 byte Video display adapter internal mode register 65h 100 Int 10h 1 byte Video display adapter internal mode register 65h 100 Int 10h 1 byte Bit 7, 0b = not used 65t 5 0 b = attribute bit background intensity 1b = attribute bit controls blinking 65h 1b = video signal 66h 1b = video signal 67h 1b = video signal 68h 1b = video signal 69h = video signal 69h = video signal 60h = video signal 61h = video signal 60h = video signal 61h =  |      |     |         | ,       |                                                                                                                                                                                                                                                                                               |

| 58h 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |     |         | ,       |                                                                                                                                                                                                                                                                                               |

| SAh 90 Int 10h 2 bytes Cursor position for video page 5 SCh 92 Int 10h 2 bytes Cursor position for video page 6 SEh 94 Int 10h 2 bytes Cursor position for video page 7 60h 96 Int 10h 2 bytes Cursor shape 62h 97 Int 10h 1 byte Active video page 63h 99 Int 10h 2 bytes I/O port address for the video display adapter 65h 100 Int 10h 1 byte Video display adapter internal mode register  Bit 7, 0b = not used Bit 5 0b = attribute bit background intensity 1b = attribute bit controls blinking Bit 4, 1b = mode 6 graphics operation Bit 3 - video signal disabled 1b = video signal enabled  Bit 2 - color operation 0b = color operation 1b = monochrome operation Bit 0, 1b = mode 4/5 graphics operation Bit 0, 1b = mode 2/3 test operation Bit 6, 0b = not used Bit 5 - mode 2/3 test operation Color palette Bit 7, 0b = not used Bit 6, 0b = not used Bit 6, 0b = not used Bit 6, 0b = not used Bit 5 - mode 5 foreground colors 0b = green/red/yellow 1b = cyan/magenta/white Bit 4 - background color 0b = normal background color 1b = intensified background color 1b = intensified background color Bit 3 - intensified background color Bit 2 - red Bit 1 - green Bit 0 - blue  67h 103 2 bytes Adapter ROM offset address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |     |         | ,       |                                                                                                                                                                                                                                                                                               |

| SCh 92 Int 10h 2 bytes Cursor position for video page 6  5Eh 94 Int 10h 2 bytes Cursor position for video page 7  60h 96 Int 10h 1 byte Active video page  62h 97 Int 10h 1 byte Active video page  63h 99 Int 10h 2 bytes I/O port address for the video display adapter  65h 100 Int 10h 1 byte Video display adapter internal mode register  8it 7, 0b = not used  8it 6, 0b = not used  8it 5  0b = attribute bit background intensity  1b = attribute bit controls blinking  8it 4, 1b = mode 6 graphics operation  8it 3 - video signal  0b = video signal disabled  1b = video signal enabled  8it 2 - color operation  0b = color operation  1b = monochrome operation  8it 1, 1b = mode 4/5 graphics operation  8it 1, 1b = mode 4/5 graphics operation  8it 1, 1b = mode 2/3 test operation  66h 101 Int 10h 1 byte Color palette  8it 7, 0b = not used  8it 6, 0b = not used  8it 7, 0b = not used  8it 6, 0b = not used  8it 6, 0b = not used  8it 7, 0b = not used  8it 6, 0b = not used  8it 6, not not used  8it 7, ob = not used  8it 6, not not used  8it 7, not not used  8it 6, not not used  8it 7, not not used  8it 7, not not used  8it 6, not not used  8it 7, not not used  8it 7, not not used  8it 7, not not used  8it 6, not not used  8it 6, not not used  8it 7, not not used  8it 7, not not used  8it 6, not not used  8it 7, not not used  8it 7, not not used  8it 6, not not used  8it 7, not not used  8it 1, 1 = mode 4/5 graphics operation  9                                          |      |     |         | ,       |                                                                                                                                                                                                                                                                                               |

| SEh 94 Int 10h 2 bytes Cursor position for video page 7 60h 96 Int 10h 2 bytes Cursor shape 62h 97 Int 10h 1 byte Active video page 63h 99 Int 10h 2 bytes I/O port address for the video display adapter 65h 100 Int 10h 1 byte Video display adapter internal mode register 65h 100 Int 10h 1 byte Video display adapter internal mode register 65h 100 Int 10h 1 byte Bit 7, 0b = not used 65h 10h = attribute bit background intensity 65h 10h = attribute bit controls blinking 65h 10h = attribute bit controls blinking 65h 10h = monochrome operation 65h 10h = monoch |      |     |         | •       |                                                                                                                                                                                                                                                                                               |

| 60h 96 Int 10h 2 bytes Cursor shape 62h 97 Int 10h 1 byte Active video page 63h 99 Int 10h 2 bytes I/O port address for the video display adapter 65h 100 Int 10h 1 byte Video display adapter internal mode register 65h 100 Int 10h 1 byte Video display adapter internal mode register 65h 100 Int 10h 1 byte Video display adapter internal mode register 65h 100 Int 10h 1 byte Video display adapter internal mode register 65h 10 e attribute bit controls blinking 65h 20 e attribute bit ackips adapter 65h 20 e attribute bit ackip |      |     |         |         |                                                                                                                                                                                                                                                                                               |

| 62h 97 Int 10h 1 byte Active video page 63h 99 Int 10h 2 bytes I/O port address for the video display adapter 65h 100 Int 10h 1 byte Video display adapter internal mode register  Bit 7, 0b = not used Bit 6, 0b = not used Bit 5 = 0b = attribute bit background intensity 1b = attribute bit controls blinking Bit 3 - video signal 0b = video signal disabled 1b = video signal enabled  Bit 2 - color operation 0b = color operation 1b = monochrome operation Bit 1, 1b = mode 4/5 graphics operation Bit 0, 1b = mode 4/5 graphics operation Bit 7, 0b = not used Bit 5 - mode 5 foreground color 0b = green/red/yellow 1b = cyan/magenta/white Bit 4 - background color 0b = normal background color 1b = intensified border color (mode 2) and background color (mode 2) and background color (mode 2) and background color (mode 5) Bit 2 - red Bit 1 - green Bit 0 - blue  67h 103 2 bytes Adapter ROM offset address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | * * |         | ,       | 1 1 0                                                                                                                                                                                                                                                                                         |

| 63h 99 Int 10h 2 bytes I/O port address for the video display adapter 65h 100 Int 10h 1 byte Video display adapter internal mode register  Bit 7, 0b = not used Bit 6, 0b = not used Bit 5  0b = attribute bit background intensity 1b = attribute bit controls blinking Bit 4, 1b = mode 6 graphics operation Bit 3 - video signal disabled 1b = video signal enabled  Bit 2 - color operation 0b = color operation 1b = monochrome operation Bit 1, 1b = mode 4/5 graphics operation Bit 0, 1b = mode 2/3 test operation  66h 101 Int 10h 1 byte Color palette Bit 7, 0b = not used Bit 6, 0b = not used Bit 6 + background colors 0b = green/red/yellow 1b = cyan/magenta/white Bit 4 - background color 0b = normal background color 1b = intensified background color Bit 3 - intensified border color (mode 2) and background color (mode 5) Bit 2 - red Bit 1 - green Bit 0 - blue  67h 103 2 bytes Adapter ROM offset address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |     |         | ,       | •                                                                                                                                                                                                                                                                                             |

| Signature   Sign   |      |     |         | ,       |                                                                                                                                                                                                                                                                                               |

| Bit 7, 0b = not used Bit 6, 0b = not used Bit 6, 0b = not used Bit 6, 0b = not used Bit 5  Ob = attribute bit background intensity 1b = attribute bit controls blinking Bit 4, 1b = mode 6 graphics operation Bit 3 - video signal Ob = video signal disabled 1b = video signal enabled  Bit 2 - color operation 0b = color operation 1b = monochrome operation Bit 0, 1b = mode 4/5 graphics operation Bit 0, 1b = mode 4/5 graphics operation Bit 7, 0b = not used Bit 7, 0b = not used Bit 6, 0b = not used Bit 6, 0b = not used Bit 5 - mode 5 foreground colors 0b = green/red/yellow 1b = cyan/magenta/white Bit 4 - background color 0b = normal background color 1b = intensified background color 1b = intensified background color Bit 3 - intensified border color (mode 2) and background color (mode 5) Bit 2 - red Bit 1 - green Bit 0 - blue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |     |         | •       |                                                                                                                                                                                                                                                                                               |

| 0b = attribute bit background intensity 1b = attribute bit controls blinking Bit 4, 1b = mode 6 graphics operation Bit 3 - video signal 0b = video signal disabled 1b = video signal enabled  Bit 2 - color operation 0b = color operation 1b = monochrome operation Bit 1, 1b = mode 4/5 graphics operation Bit 1, 1b = mode 4/5 graphics operation Bit 0, 1b = mode 2/3 test operation  66h 101 Int 10h 1 byte Color palette Bit 7, 0b = not used Bit 6, 0b = not used Bit 6, 0b = not used Bit 5 - mode 5 foreground colors 0b = green/red/yellow 1b = cyan/magenta/white Bit 4 - background color 0b = normal background color 0b = normal background color Bit 3 - intensified border color (mode 2) and background color (mode 5) Bit 2 - red Bit 1 - green Bit 0 - blue  67h 103 2 bytes Adapter ROM offset address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0011 | 100 | int ton | 1 byte  | Bit 7, 0b = not used<br>Bit 6, 0b = not used                                                                                                                                                                                                                                                  |

| Ob = color operation 1b = monochrome operation Bit 1, 1b = mode 4/5 graphics operation Bit 1, 1b = mode 4/5 graphics operation Bit 1, 1b = mode 2/3 test operation  66h 101 Int 10h 1 byte Color palette Bit 7, 0b = not used Bit 6, 0b = not used Bit 5 - mode 5 foreground colors 0b = green/red/yellow 1b = cyan/magenta/white Bit 4 - background color 0b = normal background color 1b = intensified background color Bit 3 - intensified border color (mode 2) and background color (mode 5) Bit 2 - red Bit 1 - green Bit 0 - blue  67h 103 2 bytes Adapter ROM offset address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |     |         |         | 0b = attribute bit background intensity 1b = attribute bit controls blinking Bit 4, 1b = mode 6 graphics operation Bit 3 - video signal 0b = video signal disabled                                                                                                                            |

| Bit 7, 0b = not used Bit 6, 0b = not used Bit 6, 0b = not used Bit 5 - mode 5 foreground colors 0b = green/red/yellow 1b = cyan/magenta/white Bit 4 - background color 0b = normal background color 1b = intensified background color Bit 3 - intensified border color (mode 2) and background color (mode 5) Bit 2 - red Bit 1 - green Bit 0 - blue  67h 103 2 bytes Adapter ROM offset address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |     |         |         | 0b = color operation<br>1b = monochrome operation<br>Bit 1, 1b = mode 4/5 graphics operation                                                                                                                                                                                                  |