Tandy 1000SX

# Technical Reference Manual

TANDY 1000 SX

TECHNICAL REFERENCE MANUAL

## Tandy 1000 SX Technical Reference Manual Copyright 1986, Tandy Corporation. All rights reserved.

Reproduction or use without the express written permission from Tandy Corporation, of any portion of this manual is prohibited. While reasonable efforts have been taken in the preparation of this manual to assure its accuracy, Tandy Corporation assumes no liability resulting from any errors or omissions in this manual, or from the use of the information obtained herein.

#### TANDY 1000 SX CONTENTS

MAIN LOGIC BOARD

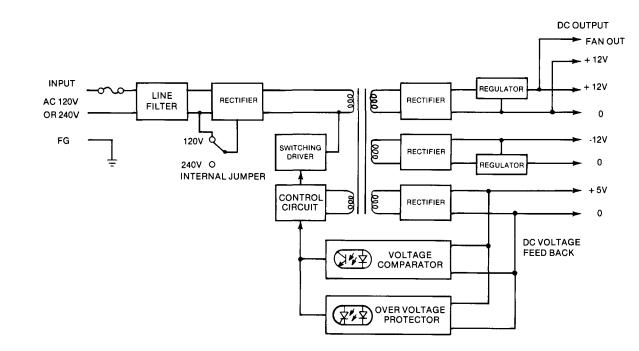

POWER SUPPLIES

KEYBOARD

8087 COPROCESSOR

RS-232 INTERFACE BOARD

MOUSE CONTROLLER/CALENDAR

PLUS NETWORK 4 INTERFACE

DEVICES

Note: Complete information for the Disk Drives for this unit is available through your local store. They will order the desired Service Manual from Radio Shack National Parts, Fort Worth, Texas.

### Foldout Page Insertion Guide

## To Be Inserted after Page 12 of the Main Logic Section

Light Blue to System

Timing Diagram

Sheets 1 of 2 and 2 of 2

Big Blue To System

Timing Diagram

Sheets 1 of 2 and 2 of 2

Tan to System Timing Diagram

Sheet 1 of 1

# To Be Inserted at the end of the Main Logic Section

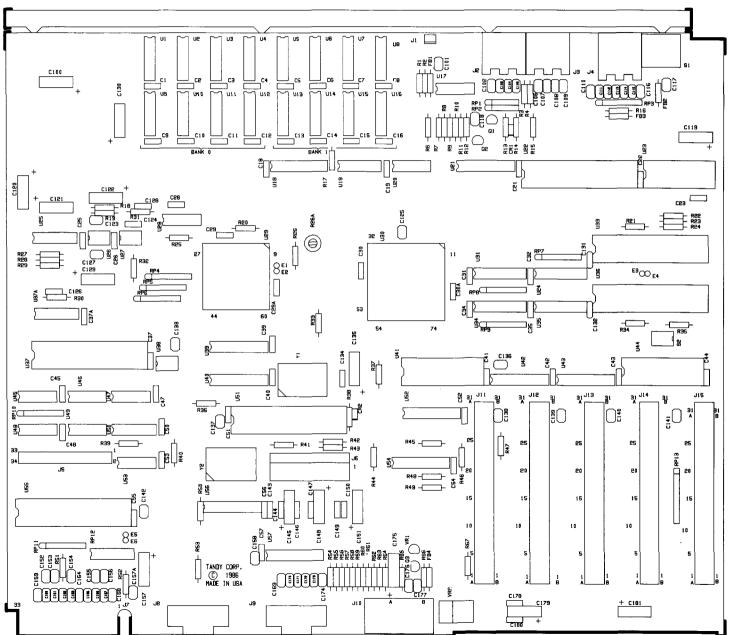

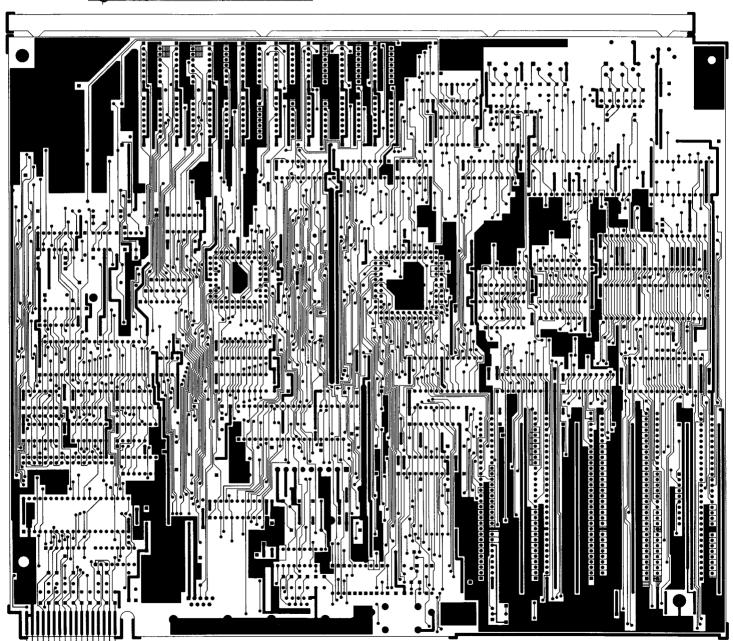

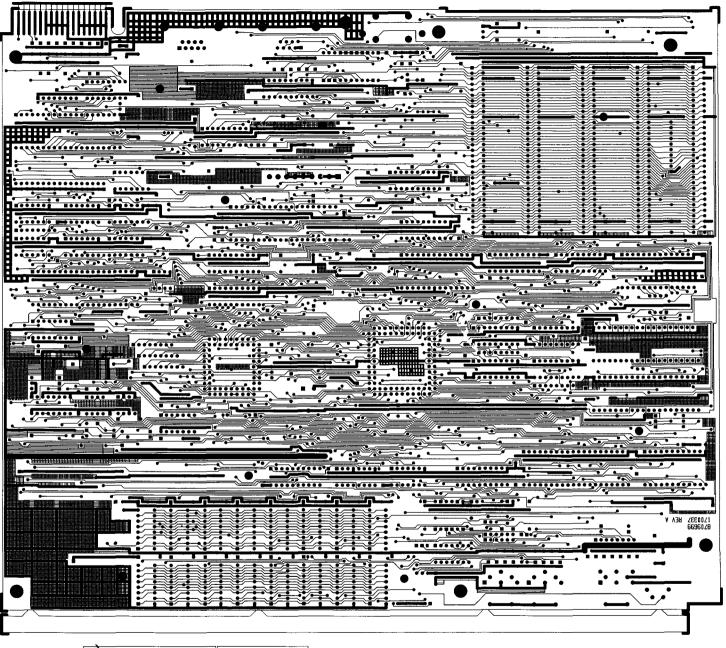

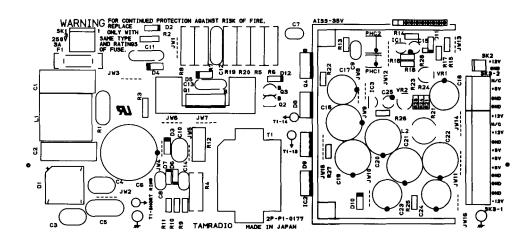

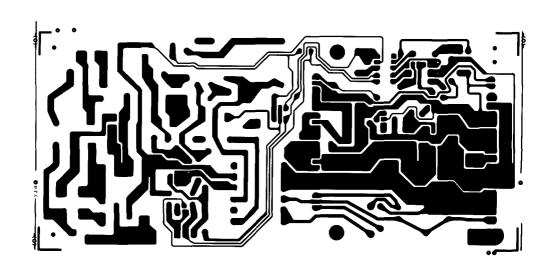

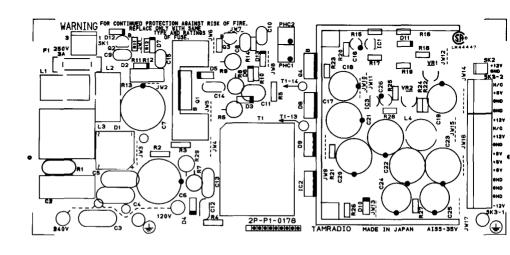

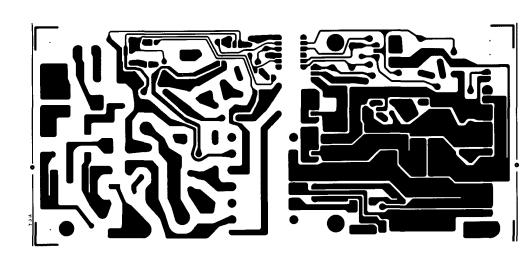

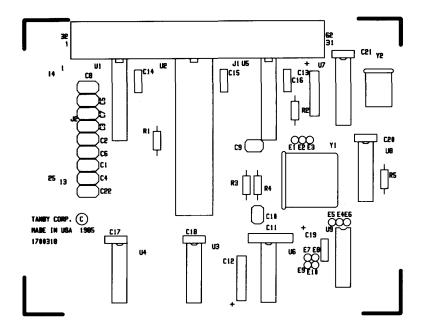

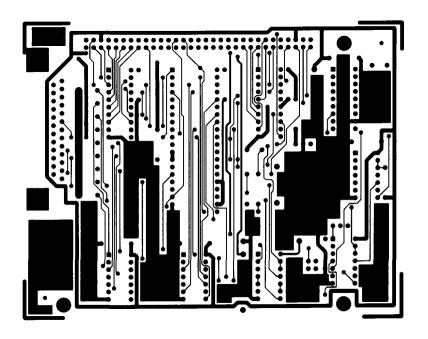

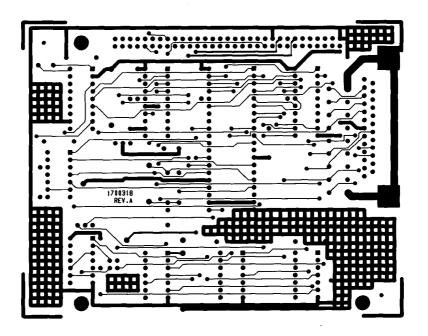

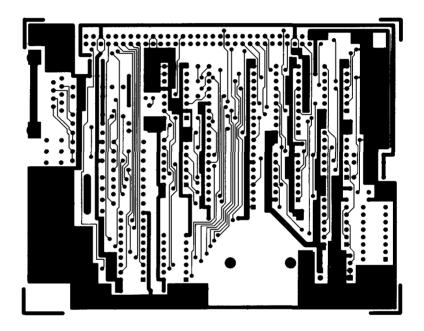

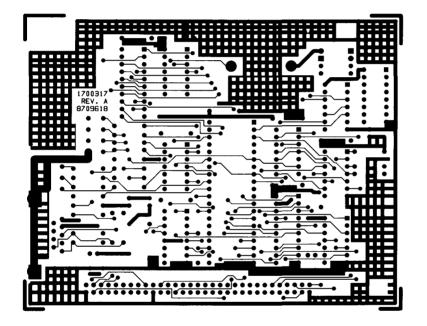

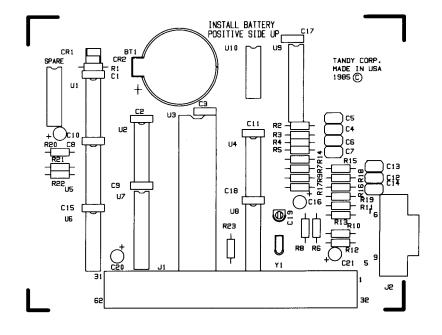

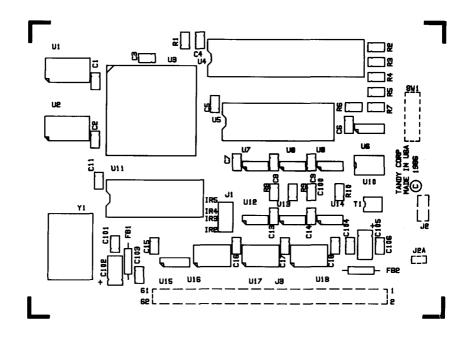

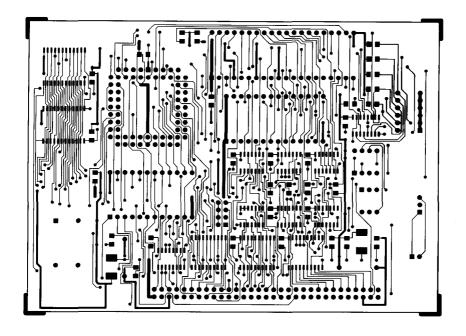

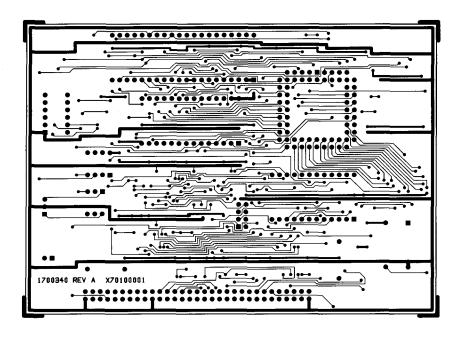

PCB Art (Silkscreen, Component and Solder

1700337 Rev. A

Sides)

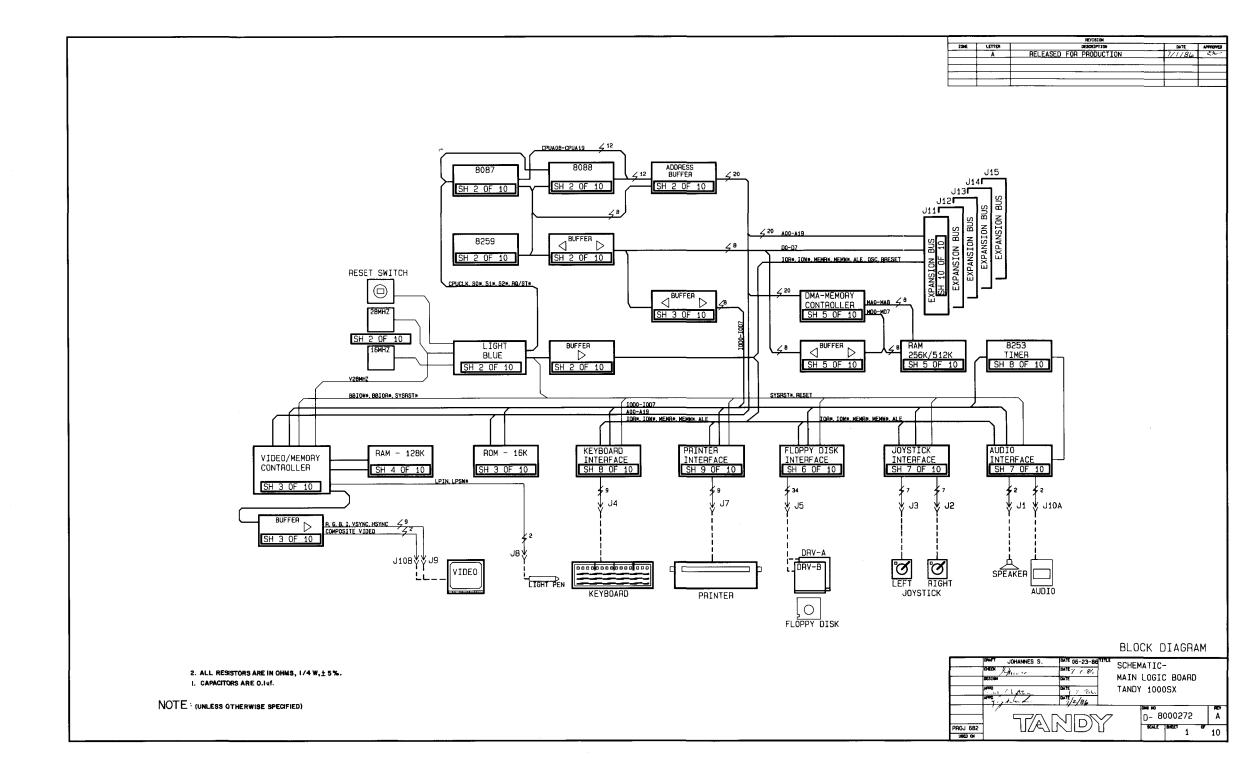

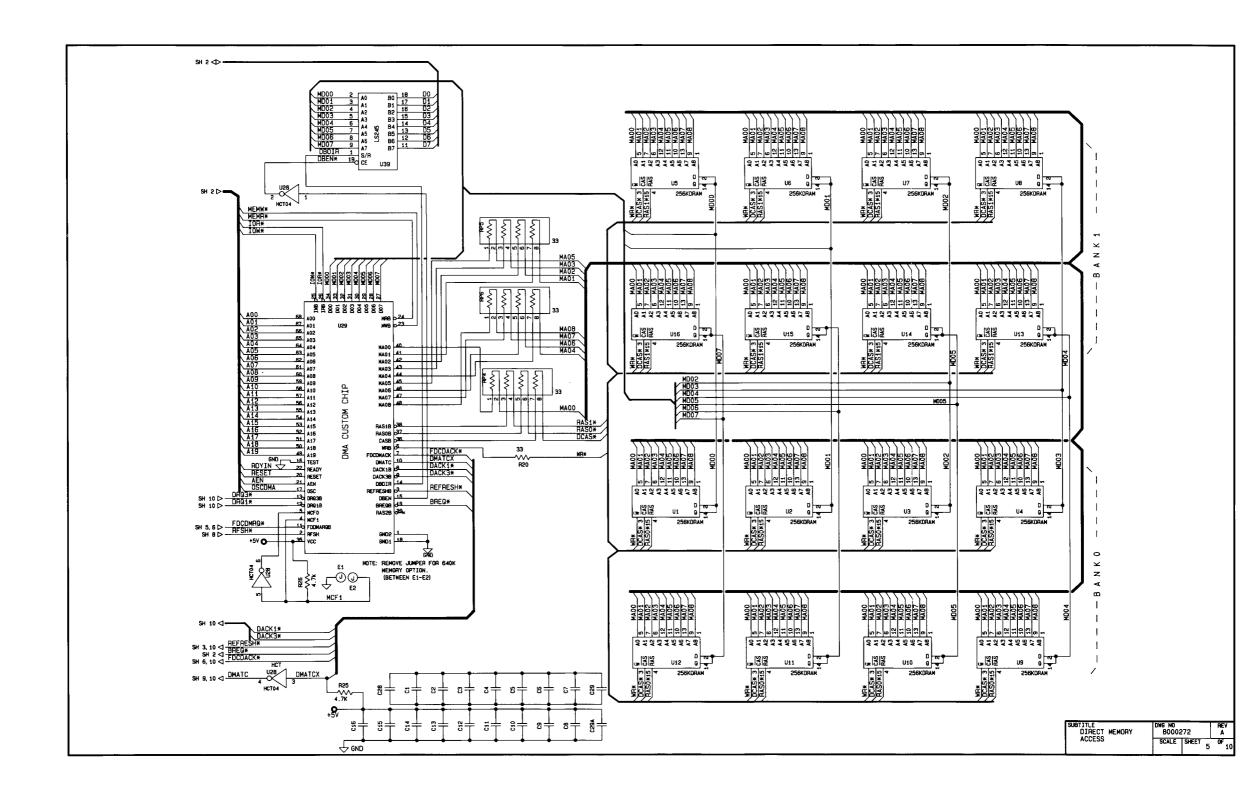

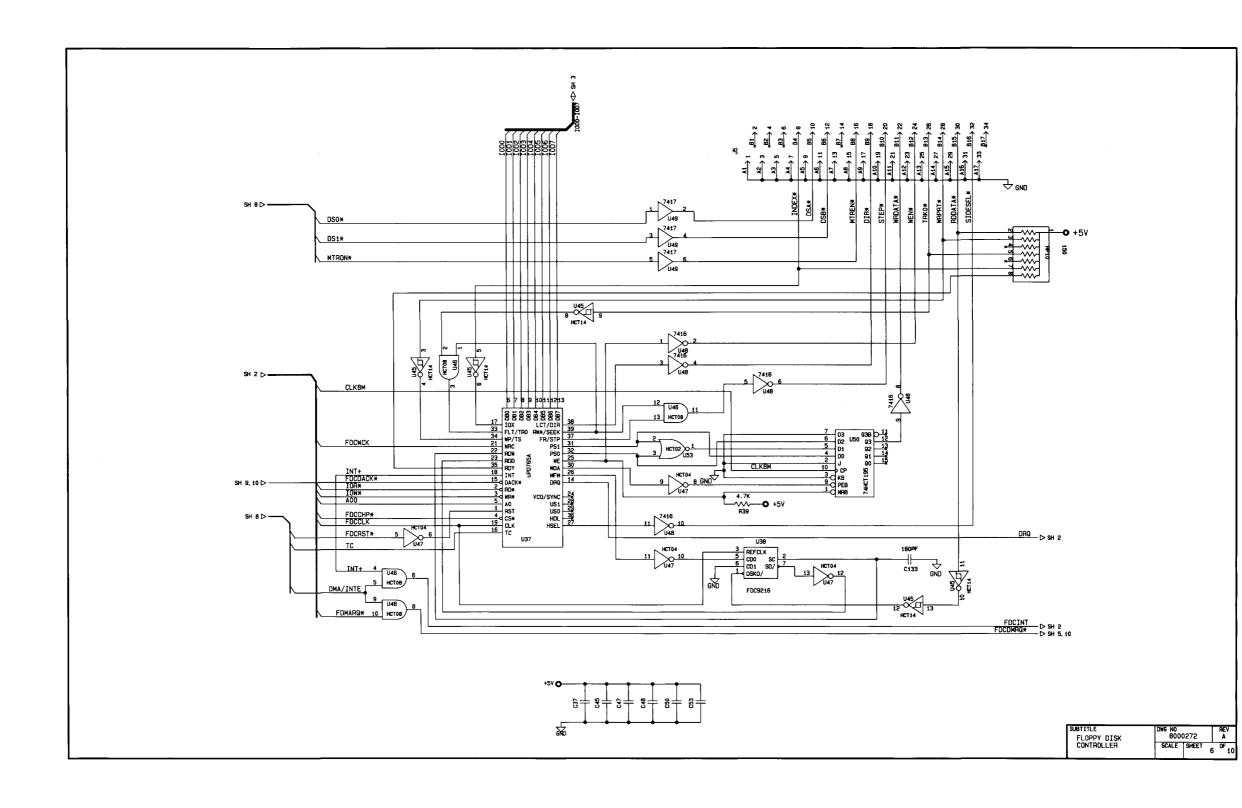

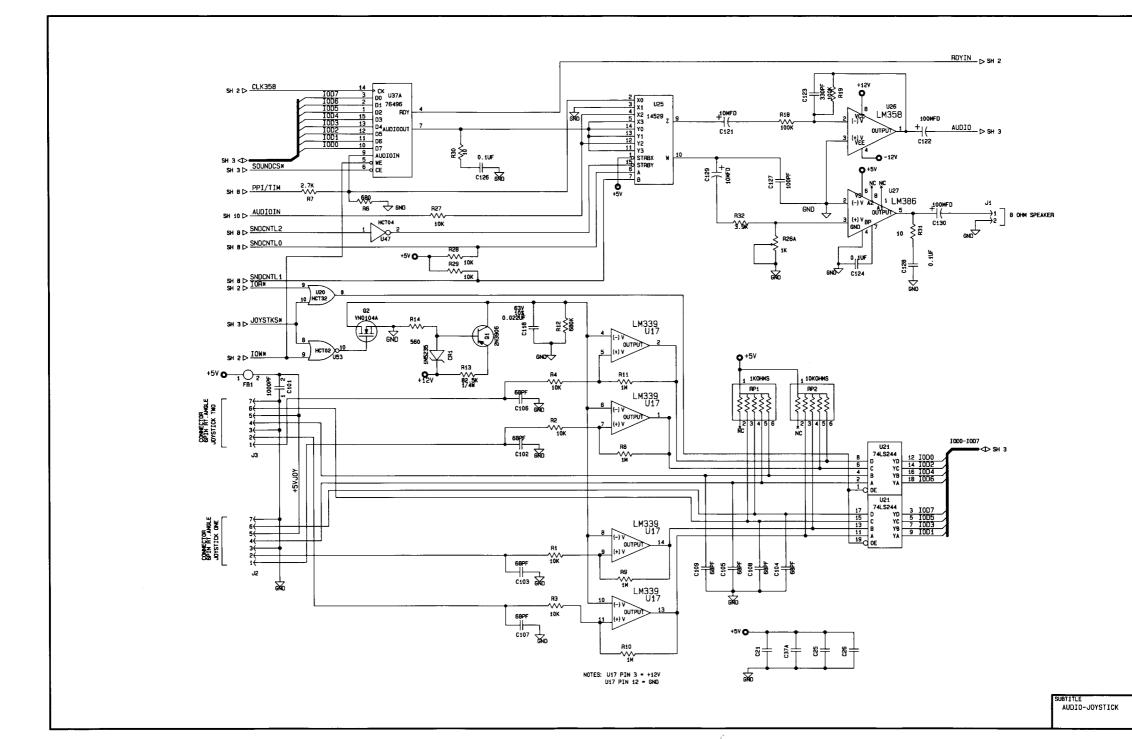

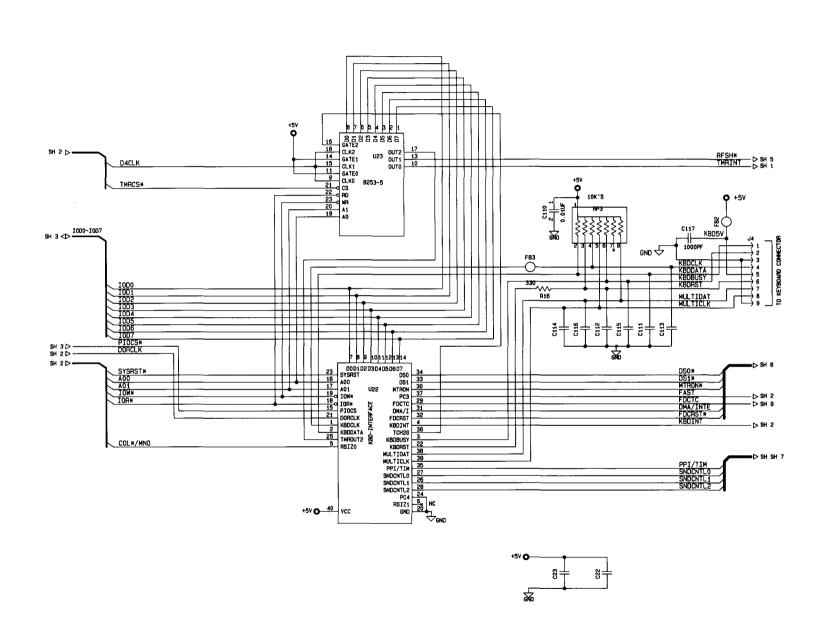

Main Logic Schematic

8000272

Sheets 1 of 10 thru 10 of 10

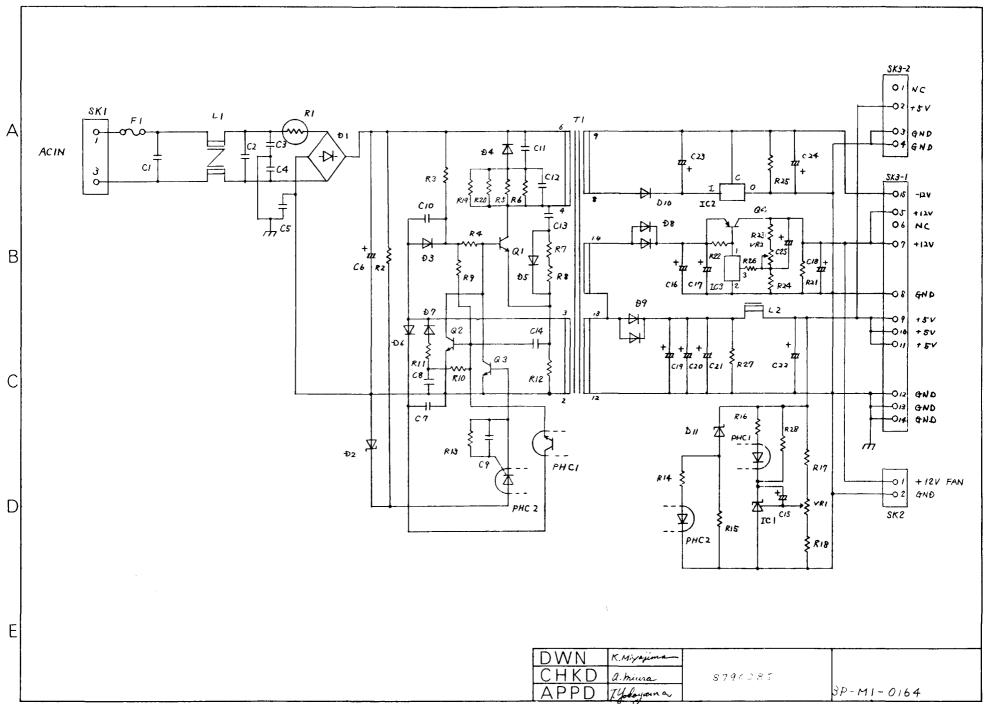

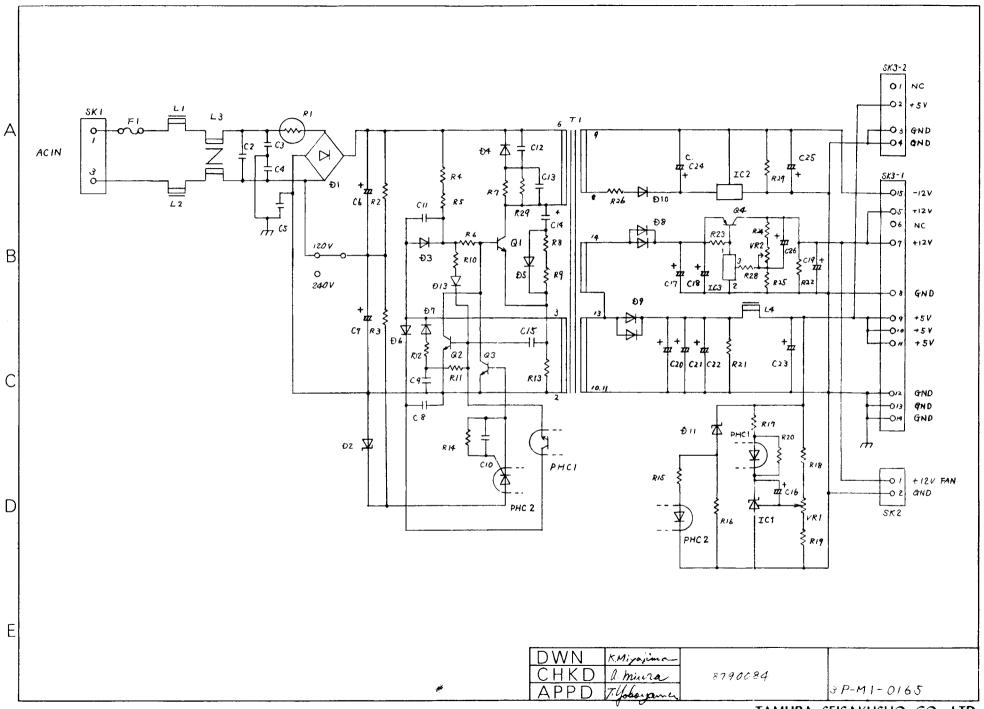

# To Be Inserted <u>at the end of the 67 Watt Single Input Power Supply</u>

Schematic

8790085 3P-M1-0164

To Be Inserted at the end of the 67 Watt Dual Input Power Supply

Schematic

8790084 3P-M1-0165

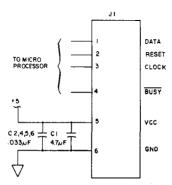

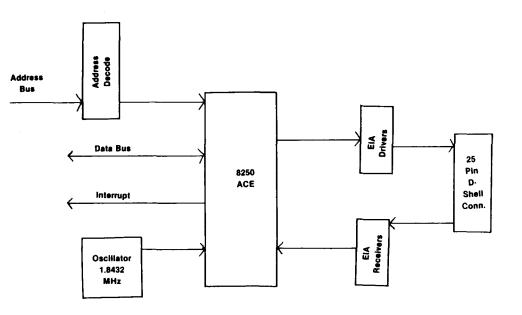

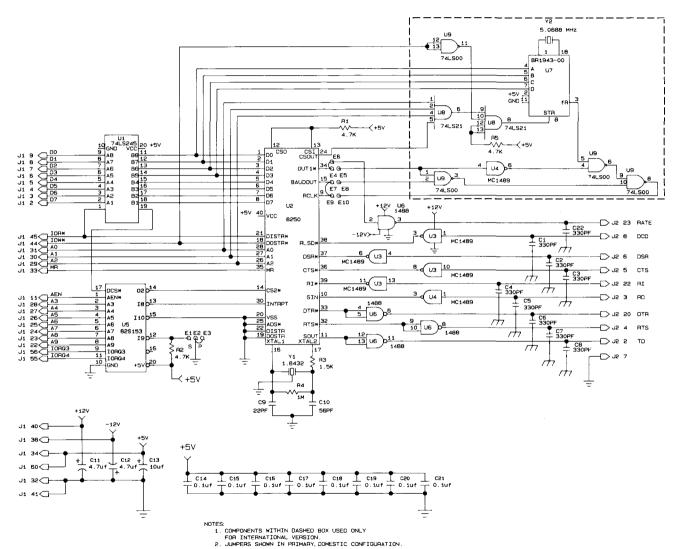

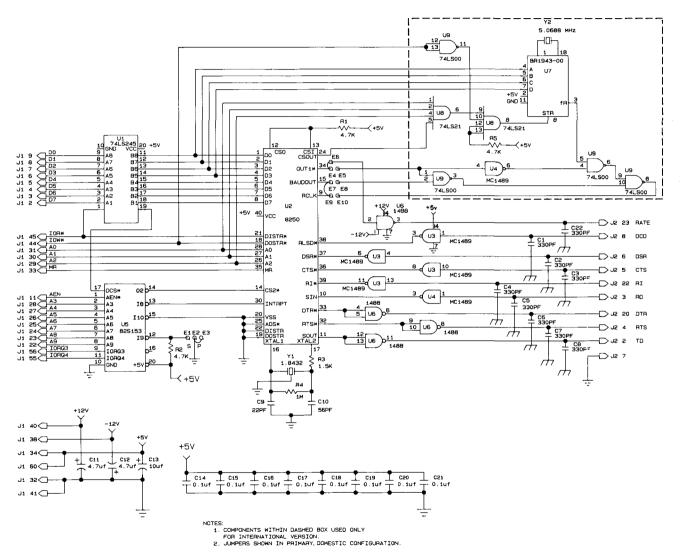

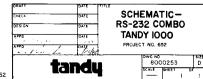

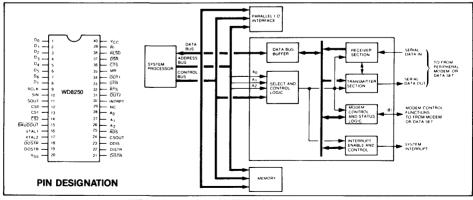

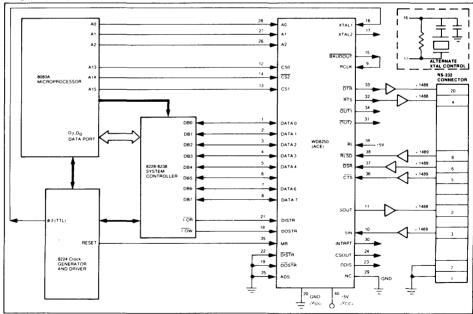

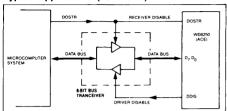

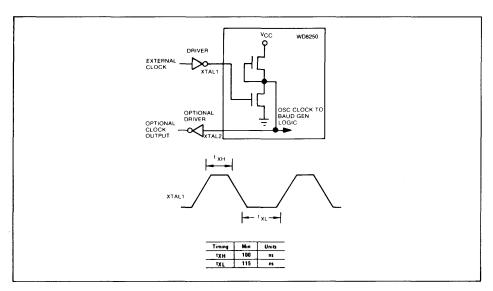

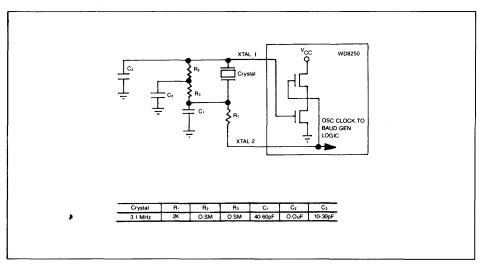

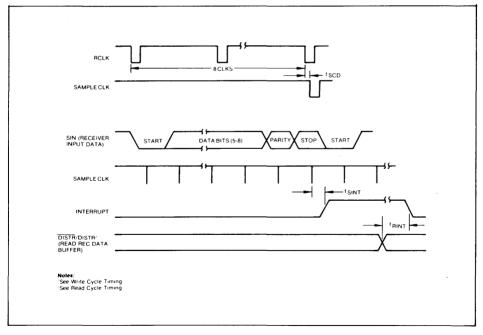

# To Be Inserted <u>just before WD 8250 Asynchronous</u> Communication Element Specification of RS-232 Section

Schematic of RS-232

8000253 (Rev. A)

Board

Sheet 1 of 1

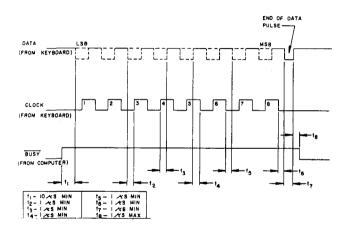

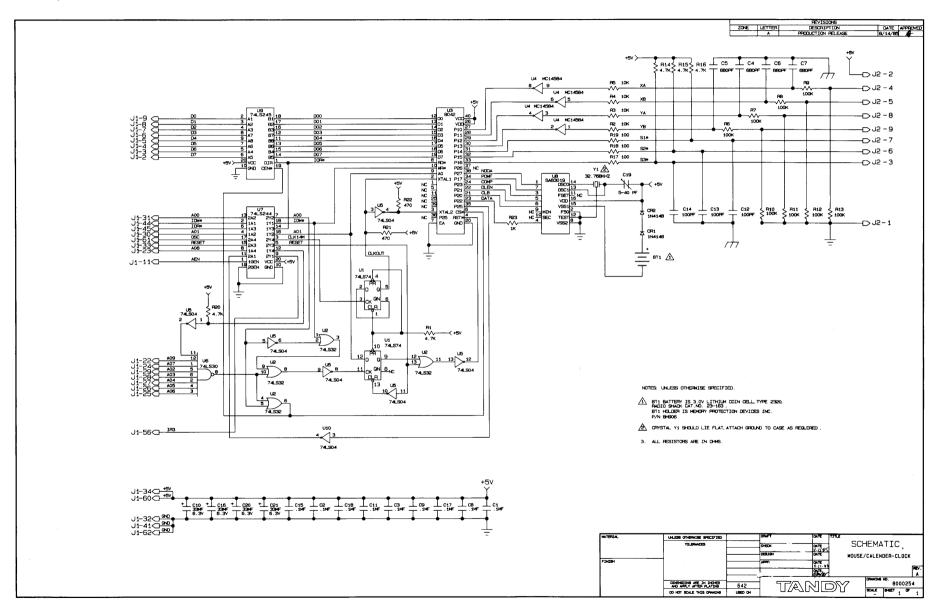

# To Be Inserted <u>after Page 22 of the Mouse Controller/Calendar Section</u>

Schematic

8000254

Sheet 1 of 1

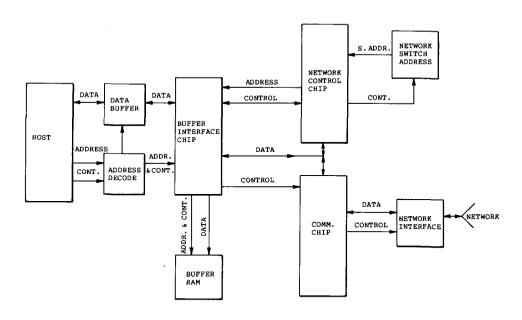

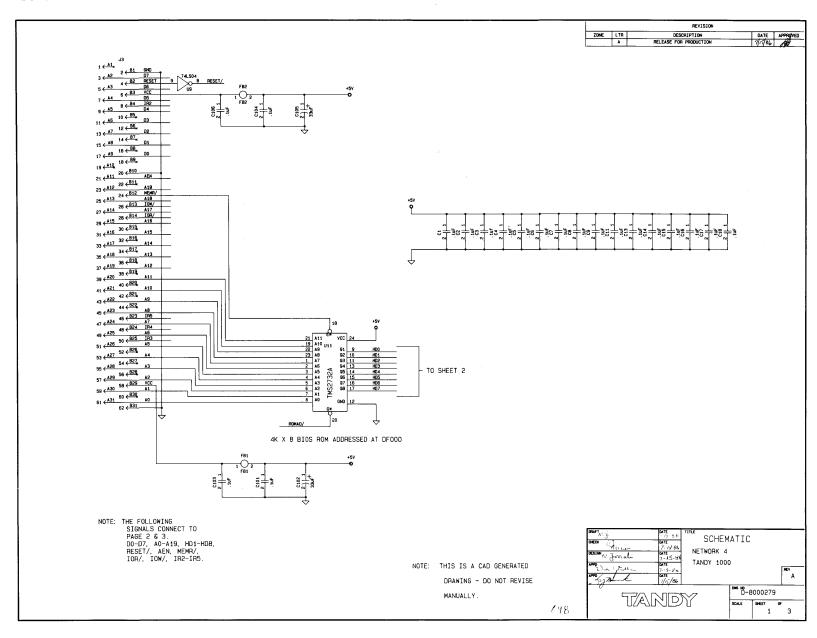

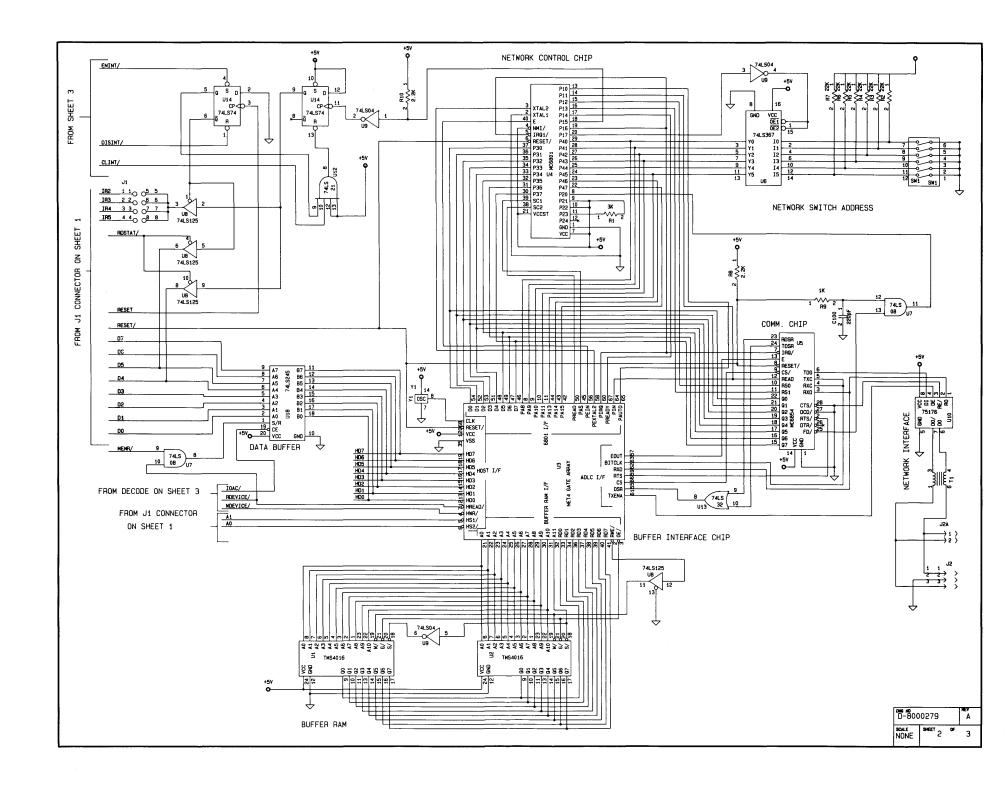

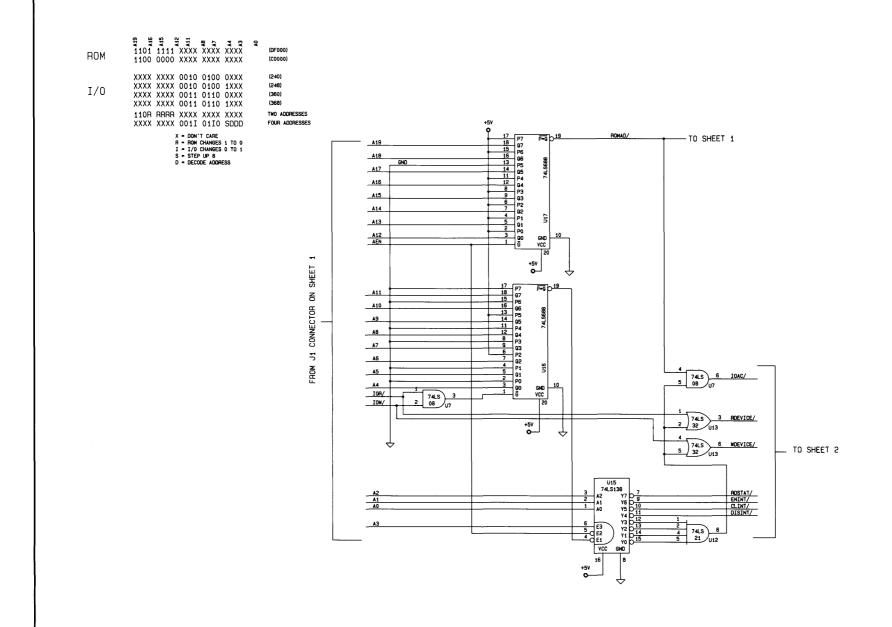

# To Be Inserted at the end of the PLUS Network 4 Interface Section

Schematic

D-8000279

Sheets 1,2 and 3 of 3

| TANDY COMPUTER PRODUCTS |  |

|-------------------------|--|

|                         |  |

|                         |  |

|                         |  |

|                         |  |

| MAIN LOGIC BOARD        |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

|                         |  |

# MAIN LOGIC BOARD CONTENTS

| INTRODUCTION        | . 1 |

|---------------------|-----|

| SPECIFICATIONS      | . 3 |

| SYSTEM TIMING       |     |

| THEORY OF OPERATION | 19  |

| PARTS LIST          |     |

| PCB ART             |     |

| SCHEMATICS          |     |

|                     |     |

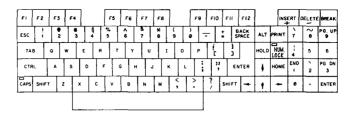

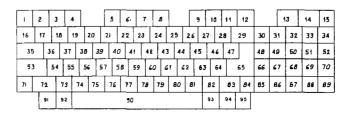

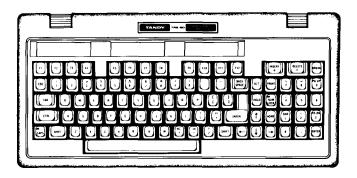

#### INTRODUCTION TO THE TANDY 1000 SX COMPUTER

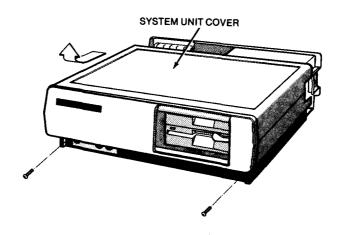

The Tandy 1000 SX Computer is modular in design to allow maximum flexibility in system configuration. The computer consists of a Main Unit, a detachable keyboard with coiled cable, and a monitor. The Main Unit is supplied with two internal floppy disk drives. The standard types of monitors used with the Tandy 1000 SX are the monochrome composite and the color RGB monitor. Since these units are modular, they may be placed on top of the Main Unit or at any convenient location.

The Tandy 1000 SX comes standard with 384K of system RAM. An optional 8 additional 256K RAM chips may be added on the system board to expand the memory to a full 640K bytes, the maximum RAM allowed by the system memory map.

Other features include a parallel printer port, two built-in joystick interfaces, a speaker for audio feedback, and a light pen interface.

The Main Unit is the heart of the Tandy 1000 SX. It houses the Main Logic Assembly, system power supply, and floppy disk drives.

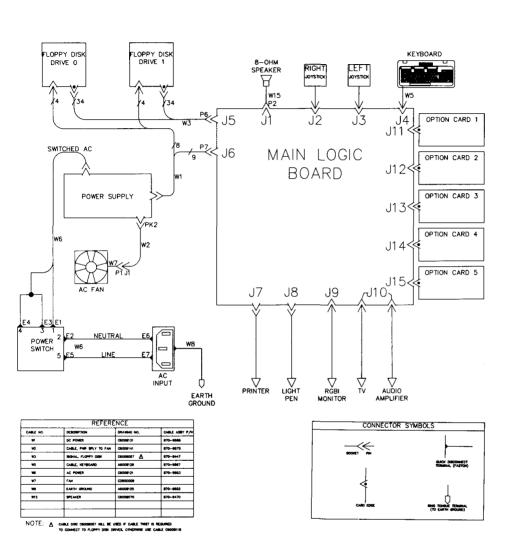

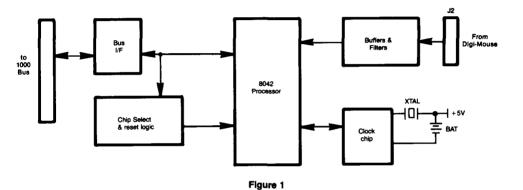

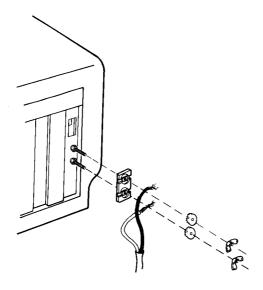

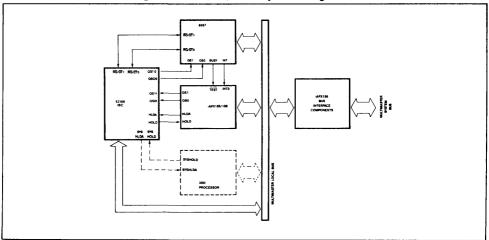

The Main Logic Assembly is a large board mounted to the bottom of the Main Unit and interconnected to the keyboard, power supply, and disk drives by a series of cables. The illustration in Figure 1 shows the major components of a Tandy 1000 SX system.

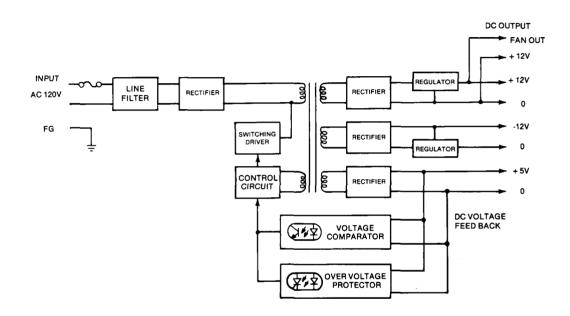

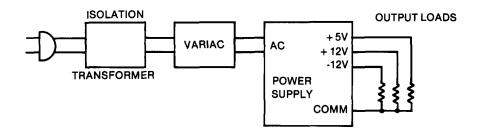

The Power Supply is a 67W switching regulator type, designed to provide adequate power capacity for a fully configured system using all the option slots.

The Floppy Disk Drive uses 5 1/4" double-sided, double-density diskettes to read, write, or store data. These are soft sector diskettes. The Disk Drive assembly is installed in the main unit. The floppy disk stores approximately 360K bytes (formatted) of data. All system programs, with the exception of the system startup sequence, are stored on disk.

Either a monochrome or a color display may be used with the Tandy 1000 SX. The monochrome monitor is a high-resolution green phosphor display which provides excellent visual quality. It features a 12" screen with an anti-glare surface. Each display is capable of 25 lines of 80 characters. The character matrix is 8 wide x 9 high.

Figure 1. TANDY 1000 SX Interconnect Diagram

#### - TANDY COMPUTER PRODUCTS -

## SPECIFICATIONS (Computer and Keyboard)

Intel 8088 - 2 Processor:

Computer - 16 3/4" x 13 1/2" x 5 3/4" Dimensions:

Keyboard - 16 1/4" x 8" x 1.5"

Computer - 18 lbs (with 2 Floppy Disk Drives) Weight:

Keyboard - 3 lbs 4 oz.

#### Power Requirements:

Range: 105 VAC to 135 VAC

Nominal: 120 VAC, 60 Hz, 3 Amp maximum

#### With 2 Floppy Disk Drives, 640K Memory:

AC Current: 350 - 400 mA with Floppy doing R/W tests.

Leakage Current: 0.5 mA

Disk Drive:

|        | +5 VDC      | +12 VDC          |

|--------|-------------|------------------|

| Idle   | 330 mA      | 160 mA           |

| R/W    | 300 mA      | 330 mA           |

| D /147 | 220 m3 /Min | . ) 600 mm / / k |

220 mA (Min.) 600 mA (Max.) 1700 mA 360 mA R/W Main Logic Board: 1700 mA

Option Cards: -12VDC, 9 m,A

#### Operating Environment:

Temperature: 55 to 85 degrees F (13 to 30 degrees C)

Humidity: 40% to 80% non-condensing

#### Non-Operating Environment:

Temperature: -40 to +160 degrees F (-40 to 71 degrees C)

20% to 90% non-condensing Humidity:

## Disk Drive Specifications

#### Power:

Supply Voltage +5 VDC Input +12 VDC Input

Ripple

0 to 50 kHz 100 mV 100 mV Tolerance

Including Ripple +/-5% +/-5%

Standby Current

Nominal 190 mA 160 mA Worst Case 220 mA 190 mA

Operating Current

600 mA Nominal 260 mA Worst Case 300 mA 1000 mA

## Environment:

#### Temperature

Operating 40 to 115 degrees F (4 to 46C) Nonoperating -8 to 140 degrees F (-22 to 60C)

Relative Humidity

Operating 20% to 80% (noncondensing) Nonoperating 5% to 95% (noncondensing)

## Connector Pin Assignments

J1 -- Speaker Interface (2-Pin Vertical Header)

1 -- Sound 2 -- Ground

J2 -- Right Joystick (6-Pin Rt. Angle Circular Din)

1 -- Y Axis 3 -- Ground 2 -- X Axis 4 -- Switch 1

5 -- +5 VDC 6 -- Switch 2

J3 -- Left Joystick

(6-Pin Rt. Angle Circular Din)

1 -- Y Axis

2 -- X Axis

3 -- Ground 4 -- Switch 1 5 -- +5 VDC 6 -- Switch 2

J4 -- Keyboard Interface (8-pin Rt. Angle Circular Din)

1 -- KBDDATA 2 -- KBDBUSY\*

3 -- Ground 4 -- KBDCLK

5 -- +5 VDC 6 -- KBDRST

4 -- MULTIDATA 8 -- MULTICLK

8 -- -12 VDC

```

Floppy Disk Interface (Dual 17-Pin Vertical Header)

J5 <del>--</del>

1 -- Ground

2 -- NC

4 -- NC

3 -- Ground

5 -- Ground

6 -- NC

7 -- Ground

8 -- INDEX*

9 -- Ground

10 -- DSO*

11 -- Ground

12 -- DS1*

14 -- NC

13 -- Ground

16 -- MTRON*

15 -- Ground

18 -- DIR*

17 -- Ground

19 -- Ground

20 -- STEP*

21 -- Ground

22 -- WRDATA*

24 -- WEN*

23 -- Ground

25 -- Ground

26 -- TRK0*

28 -- WRPRT*

27 -- Ground

29 -- Ground

30 -- RDDATA*

32 -- SIDESELECT*

31 -- Ground

33 -- Ground

34 -- DRVRDY*

J6 --

DC POWER

(9-PIN VERTICAL HEADER)

1 -- +5 VDC

2 -- +5 VDC

4 -- Ground

3 -- +5 VDC

5 -- Ground

6 -- Ground

```

7 -- +12 VDC

```

J7 --

Parallel Interface

(34-Pin Card Edge)

1 -- PPSTROBE*

2 -- Ground

3 -- PPDATA0

4 -- Ground

5 -- PPDATA1

6 -- Ground

7 -- PPDATA2

8 -- Ground

9 -- PPDATA3

11 -- PPDATA4

13 -- PPDATA5

10 -- Ground

12 -- Ground

13 -- PPDATA5

14 -- NC

15 -- PPDATA6

17 -- PPDATA7

19 -- PPACK*

16 -- Ground

18 -- Ground

20 -- Ground

22 -- Ground

21 -- PPBUSY

23 -- PPPAEM

24 -- Ground

25 -- PSEL*

26 -- NC

25 -- PSEL*

27 -- PPAUTOF*

28 -- PPFAULT

29 -- NC

30 -- PPINIT*

32 -- NC

34 -- +5V

31 -- Ground

33 -- Ground

J8 --

Light Pen

(9-Pin Connector Male Rt. Angle D-Subminiature)

1 -- +5 VDC

2 -- Ground

3 -- LPIN

4 -- LPSW*

5 -- NC

6 -- NC

7 -- NC

8 -- NC

9 -- NC

RGBI Video

(9-Pin Socket Rt. Angle D-Subminiature)

1 -- Ground

2 -- Ground

3 -- Red

4 -- Green

5 -- Blue

6 -- Intensity

7 -- Video

8 -- HSYNC

9 -- VSYNC

J10 --

Composite Output

(Dual Rt. Angle RCA-Type Phone Jack)

```

B -- Audio

A -- Video

# J11, J12, J13, J14, J15 -- Expansion Interface Connectors (Dual 31-Pin Card Edge)

| A01 | <br>NMI   | B01         | <br>Ground    |

|-----|-----------|-------------|---------------|

| A02 | <br>D7    | B02         | <br>BRESET    |

| A03 | <br>D6    | B03         | <br>+5 VDC    |

| A04 | <br>D5    | B04         | <br>IR2       |

| A05 | <br>D4    | B05         | <br>-5 VDC    |

| A06 | <br>D3    | B06         | <br>FDCDMARQ* |

| A07 | <br>D2    | B07         | <br>-12 VDC   |

| 80A | <br>Dl    | B08         | AUDIOIN       |

| A09 | <br>Dl    | B09         | <br>+12 VDC   |

| A10 | <br>READY | B10         | Ground        |

| All | <br>AEN   | Bll         | <br>MEMW*     |

| A12 | <br>A19   |             | MEMR*         |

| A13 | <br>A18   | B13         | <br>IOW*      |

| Al4 | <br>Al7   | B14         | <br>IOR*      |

| A15 | <br>Al6   | <b>B</b> 15 | <br>DACK3*    |

| A16 | <br>Al5   | Bl6         | <br>DRQ3*     |

| Al7 | <br>A14   | B17         | <br>DACK1*    |

| A18 | <br>A13   | B18         | DRQ1*         |

|     | Al2       | B19         | REFRESH*      |

| A20 | <br>All   |             | CLK           |

| A21 | <br>A10   | B21         | IR7           |

| A22 | <br>A09   | B22         |               |

| A23 | <br>A08   | B23         | IR5           |

| A24 | <br>A07   | B24         | IR4           |

| A25 | A06       | B25         | IR3           |

| A26 | A05       | B26         | FDCDACK*      |

| A27 | A04       | B27         | DMATC         |

| A28 | <br>A03   | B28         | ALE           |

| A29 | <br>A02   | B29         | +5 VDC        |

| A30 | A01       | B30         | <br>osc       |

| A31 | <br>A00   | B31         | <br>Ground    |

| Tandy 1000 SX and IBM I/O Bus Cross Reference Chart                                                                                         |              |

|---------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Pin No. Description                                                                                                                         |              |

| B21 IBM - Interrupt Request 7.                                                                                                              |              |

| TANDY 1000 SX - Optional Interrupt Requ                                                                                                     | est 7.       |

| B22 IBM - Interrupt Request 6.                                                                                                              |              |

| TANDY 1000 SX - Optional Interrupt Requ                                                                                                     | est 6.       |

| Pin No. Signal Name Description                                                                                                             |              |

| B08 AUDIOIN IBM - Reserved                                                                                                                  |              |

| TANDY 1000 SX - Audio input i supplied from an optional boa the I/O bus to a multiplexer main logic board for an outputhe external speaker. | rd on on the |

Note: All other pins are identical to the IBM PC. See Section 3 for the connector pin assignments.

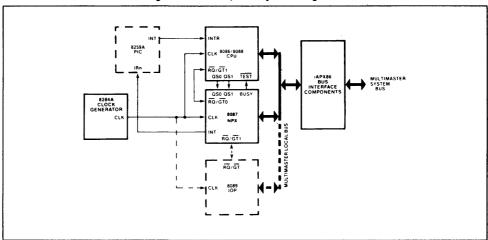

#### BUS INTERFACE SPECIFICATIONS

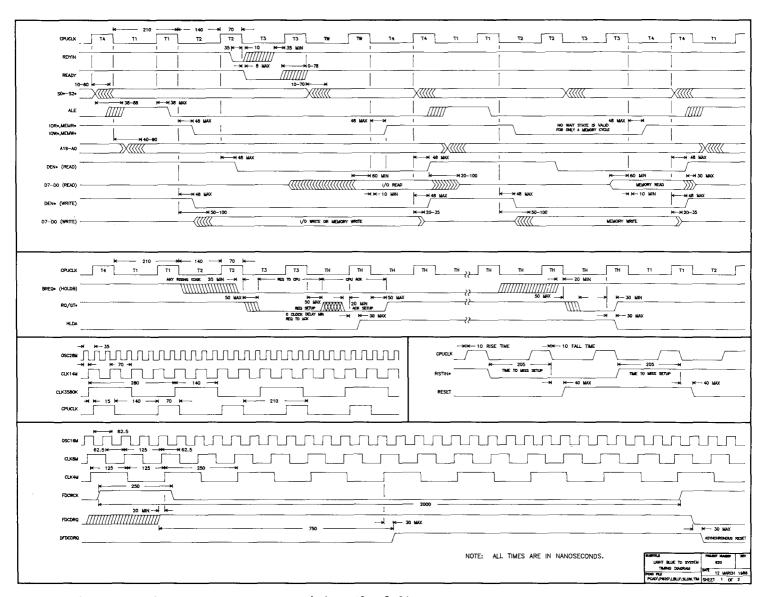

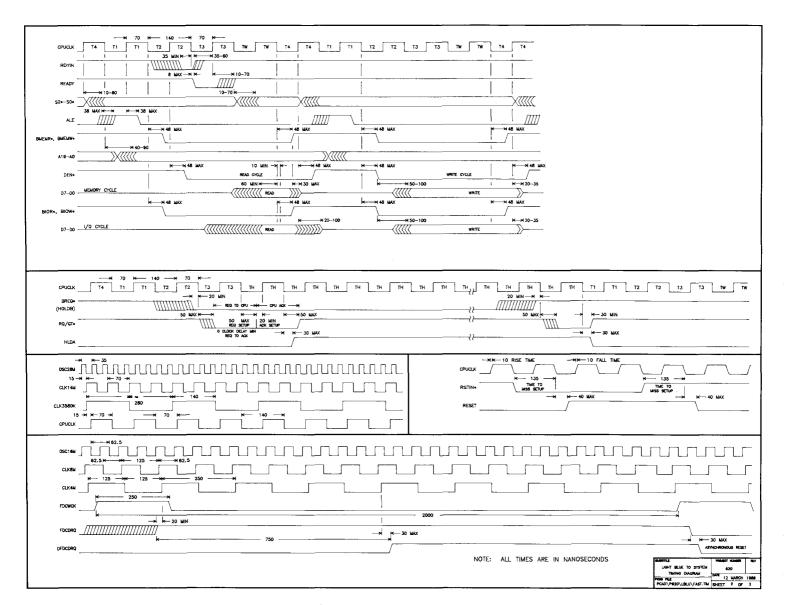

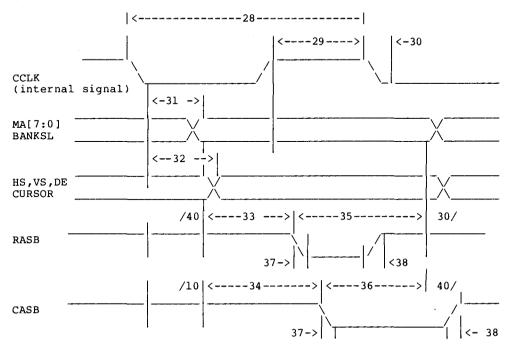

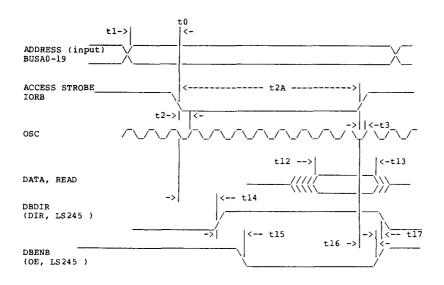

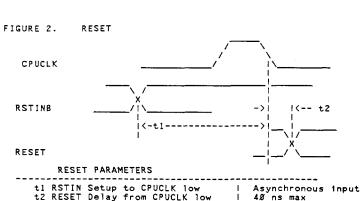

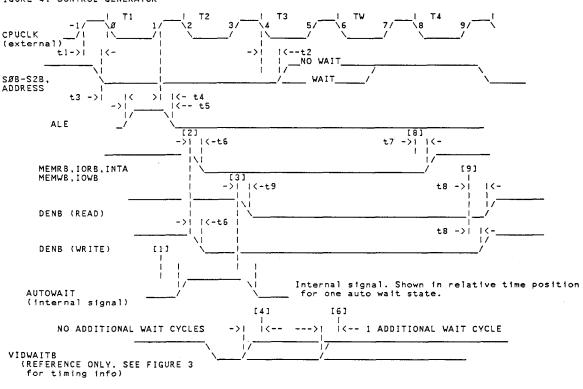

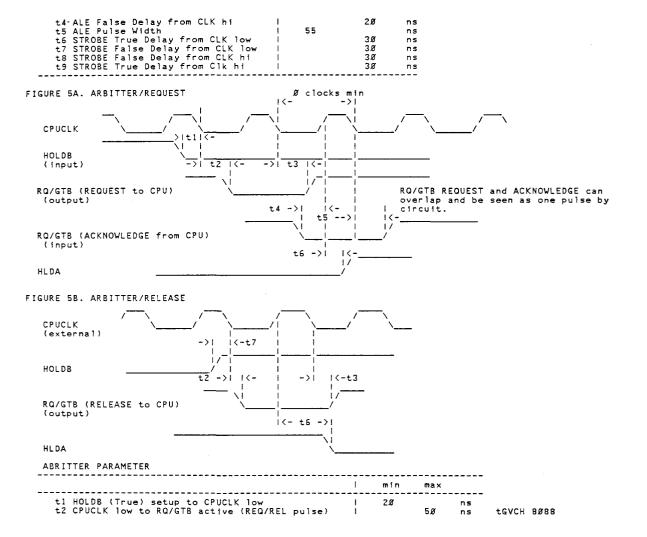

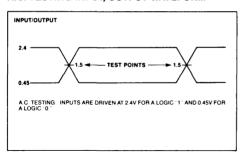

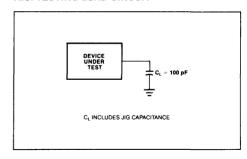

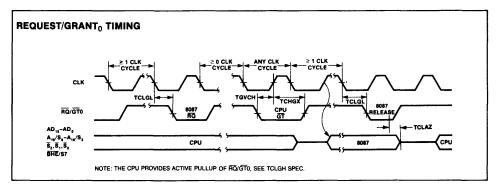

This specification is for the primary bus on the Tandy 1000 SX main logic board, which also is available to the option board connectors. The specification describes the signals in the following manner. See Figures 2 - 4.

- o The following signal nomenclature is used in the schematic and literature. Signals designated with the suffix "\*" are logically "true low" (normal inactive state is high); if they are not so designated, the signal is logically "true high."

- o Direction -- input or output -- is referenced to the CPU.

- Brief functional description of the signal.

- o Description of the "drive" or "load" characteristics of the signal. This includes the specific source by IC type and reference designator, drive capability for "output" signals, and actual load for "input" signals. The drive/load is defined in "unit loads" and specified as "high/low." This specification is for the main logic board only. Some signals have an alternate source, an external bus master such as the DMA.

- o 1 Unit Load (UL) is defined as: Ioh = .04mA @ 2.4V Iol = 1.6mA @ 0.5V

#### Signal Listing

| A00 - A19                    | 0           | ADDRESS                                                                   | SOURCE: 43,42,U54 Drive - 65/15 UL Latch Strobe - ALE Output Enable - AEN Alternate external source |

|------------------------------|-------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| D0-D7                        | 1/0         | DATA                                                                      | SOURCE: U52<br>Drive - 37/15 UL<br>Direction Control -<br>READ* (CPU read signal)<br>Enable - DEN*  |

| ALE<br>IOW*<br>IOR*<br>MEMW* | 0<br>0<br>0 | ADDRESS LATCH STROBE I/O WRITE STROBE I/O READ STROBE MEMORY WRITE STROBE | SOURCE: U56 Drive - 50/7.5 UL Output Enable - AEN Pull-Up - 4.7K Ohms                               |

## \_\_\_\_ TANDY COMPUTER PRODUCTS ---

| MEMR*    | 0 | MEMORY READ STROBE        | Alternate external source                                                                                                                                   |

|----------|---|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK      | 0 | CPU CLOCK                 | 4.77MHz, 33% duty<br>cycle, 7.16MHz, 50%<br>duty cycle.<br>SOURCE: U54<br>Drive - 75/7.5 UL                                                                 |

| OSC      | 0 | OSCILLATOR                | 14.32MHz, 50% duty<br>cycle<br>SOURCE: U54<br>Drive - 75/7.5 UL                                                                                             |

| NMI      | I | NON-MASKABLE<br>INTERRUPT | To System NMI<br>Load: 1/1 UL, Ull7                                                                                                                         |

| READY    | I | SYSTEM WAIT               | SOURCE: OPEN-COLLECTOR OR 3-STATE BUFFERS Load: 1 UL and 1.0K ohm pull-up. 10/0.9 UL Set LOW by Peripherals (I/O or Memory) to extend READ or WRITE cycles. |

| BRESET   | 0 | SYSTEM RESET              | Power On or Manual<br>SOURCE: U54<br>Drive: 75/7.5 UL                                                                                                       |

| AEN      | 0 | BUS GRANT                 | To external masters<br>SOURCE: U82<br>Drive - 75/7.5 UL                                                                                                     |

| IR2      | I | INTERRUPT REQUEST#2       | To system interrupt controller                                                                                                                              |

| IR3      | I | INTERRUPT REQUEST#3       | Load: 1 UL and 2.2K                                                                                                                                         |

| IR4      | I | INTERRUPT REQUEST#4       | pull-down                                                                                                                                                   |

| IR5      | I | INTERRUPT REQUEST#5       |                                                                                                                                                             |

| IR6      | I | INTERRUPT REQUEST#6       |                                                                                                                                                             |

| IR7      | I | INTERRUPT REQUEST#7       |                                                                                                                                                             |

| AUDIO IN | I |                           | From External Sound<br>Source<br>Load: 10k ohms.                                                                                                            |

#### ..... TANDY COMPUTER PRODUCTS -

| AUDIO                           | 0           |                                                                         | To External Source<br>Drive: 1.25 Volts P-P<br>into 10K                           |

|---------------------------------|-------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| DRQ1                            | I           | REQUEST DMA<br>CHANNEL#1                                                | Load: 8237A-5/9517A                                                               |

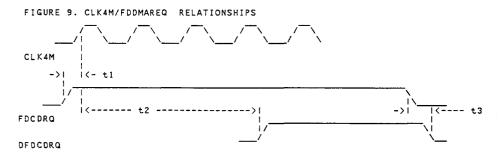

| FDCDMARQ                        | I           | REQUEST DMA<br>CHÂNNEL#2                                                | 1 MOS load 40/160 UL                                                              |

| DRQ3                            | I           | REQUEST DMA<br>CHANNEL#3                                                |                                                                                   |

| REFRESH* DACK1* FDCDACK* DACK3* | 0<br>0<br>0 | ACKNOWLEDGE DRQ0* ACKNOWLEDGE DRQ1* ACKNOWLEDGE DRQ2* ACKNOWLEDGE DRQ3* | Dedicated output<br>acknowledges from DMA.<br>Drive: 8237A-5/9517A<br>2/2 UL      |

| DMATC                           | 0           | TERMINAL COUNT                                                          | Used by DMA Controller<br>to indicate Terminal<br>Count reached.<br>Drive: 2/2 UL |

<sup>+5</sup>VDC +5VDC 4% 0.6 Amps per slot available on the bus. +12VDC +12VDC 5% 0.1 Amps per slot available on the bus. -12VDC -12VDC +8.3% - 25% 0.06 Amps available on the bus. GROUND Power Return for +5, +12, -12 VDC.

#### - TANDY COMPUTER PRODUCTS -

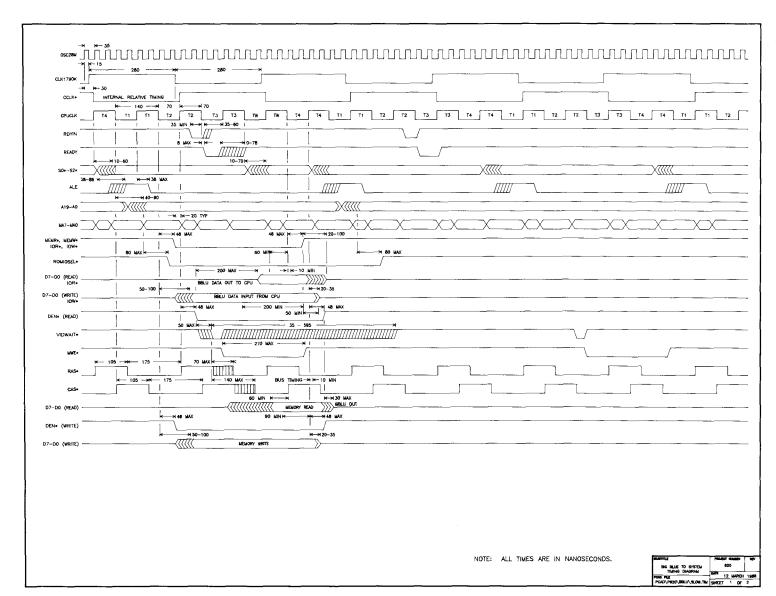

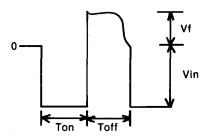

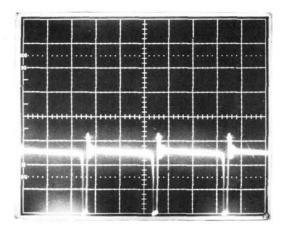

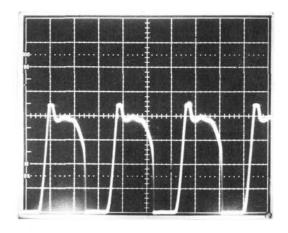

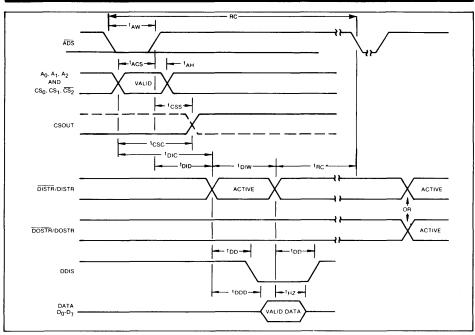

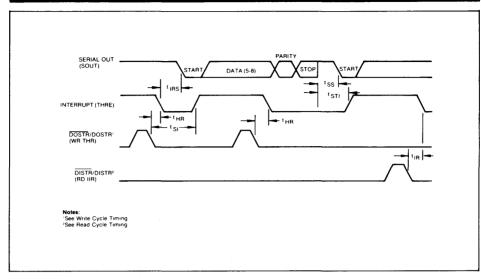

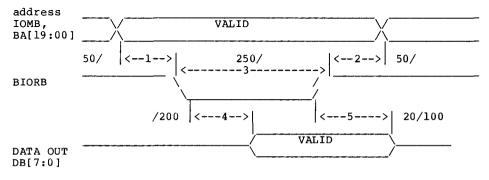

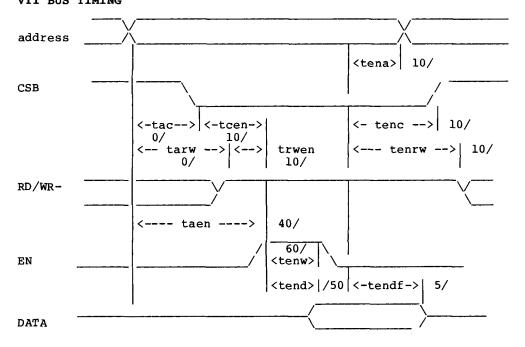

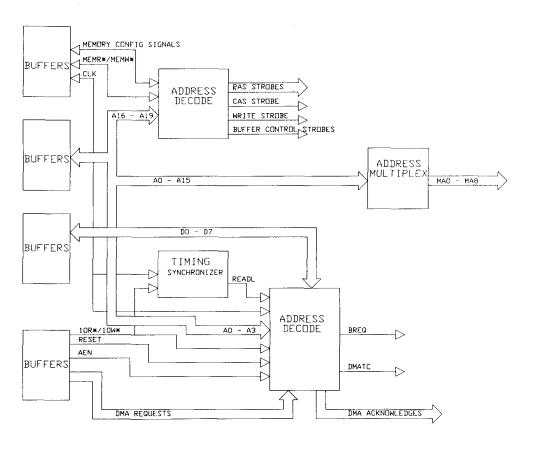

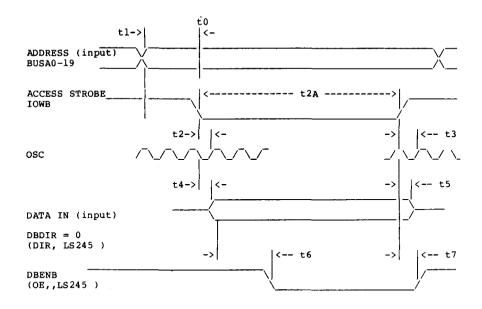

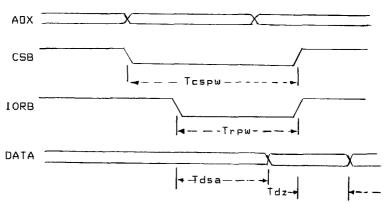

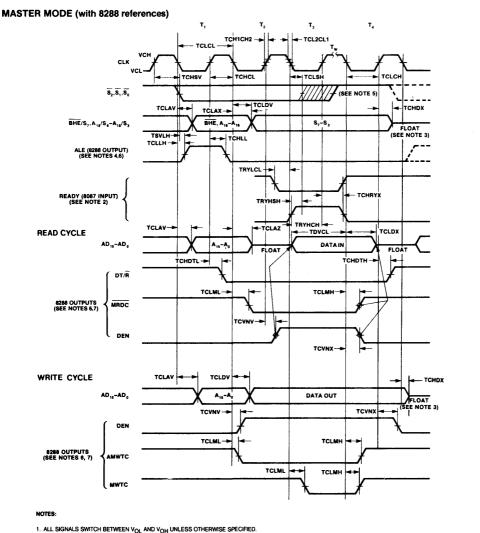

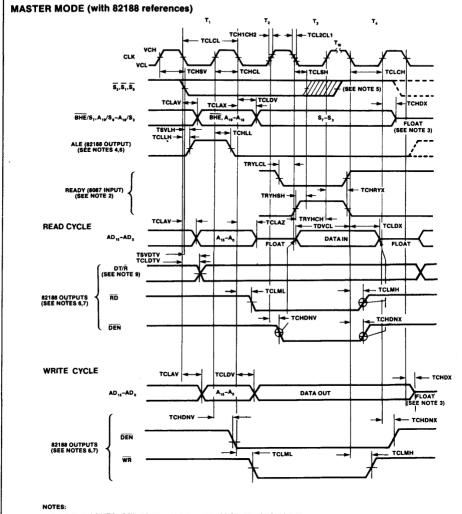

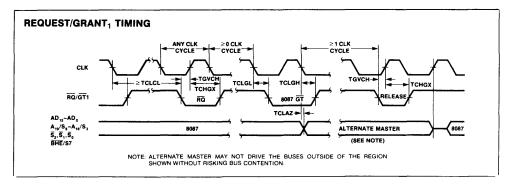

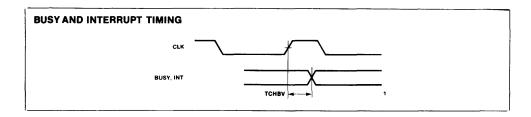

Figure 2. Light Blue to System Timing (1 of 2)

#### \_ TANDY COMPUTER PRODUCTS -

Figure 2. Light Blue to System Timing (2 of 2)

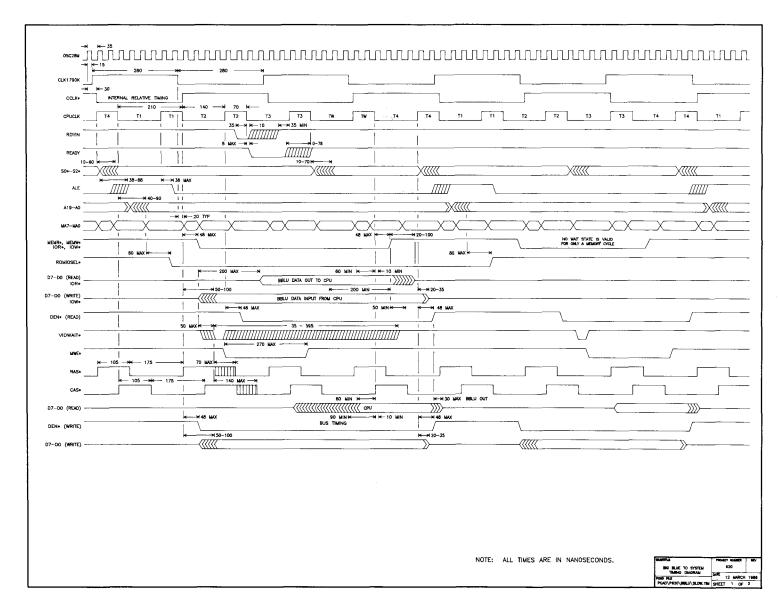

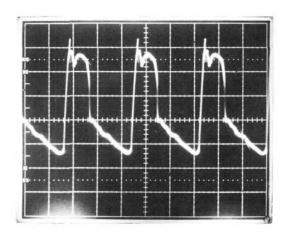

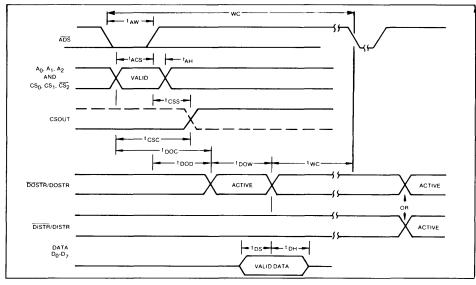

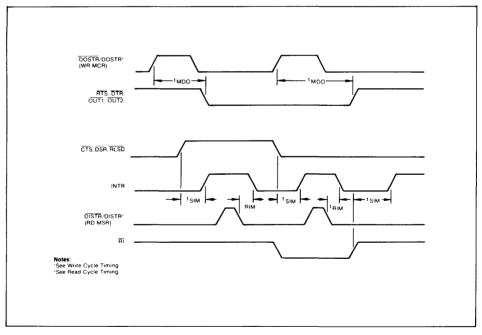

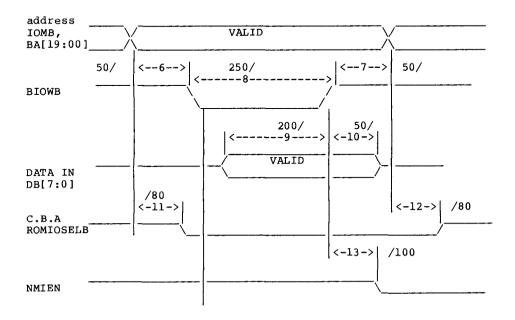

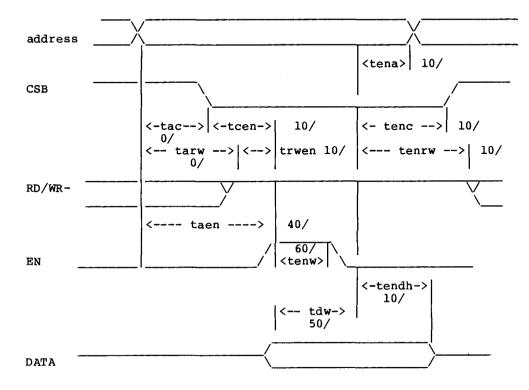

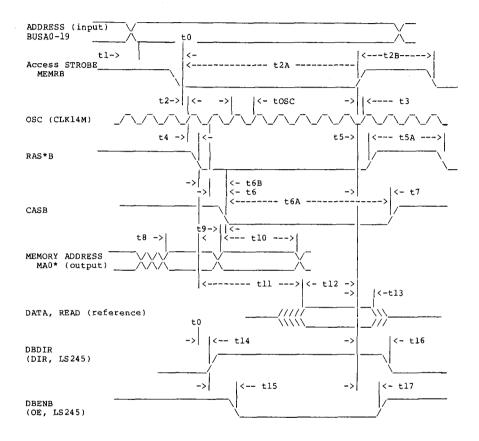

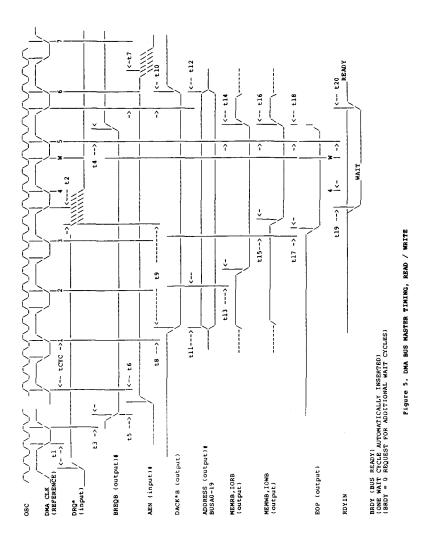

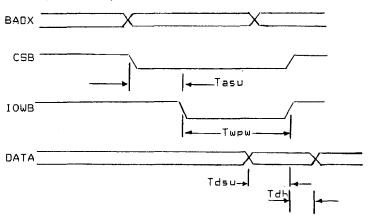

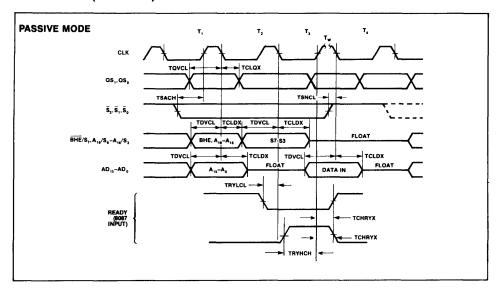

Figure 3. Big Blue to System Timing (1 of 2)

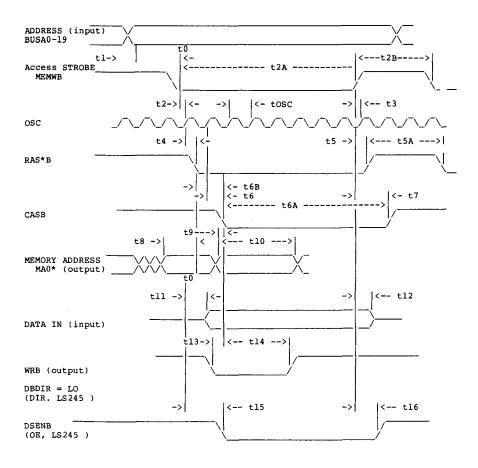

Figure 3. Big Blue to System Timing (2 of 2)

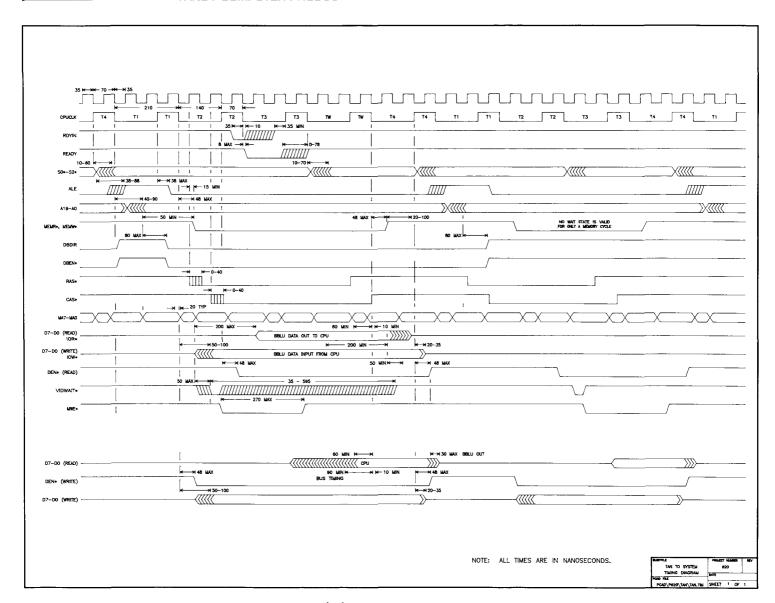

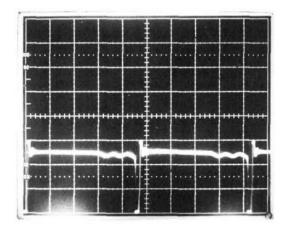

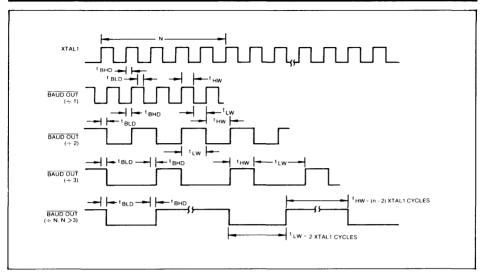

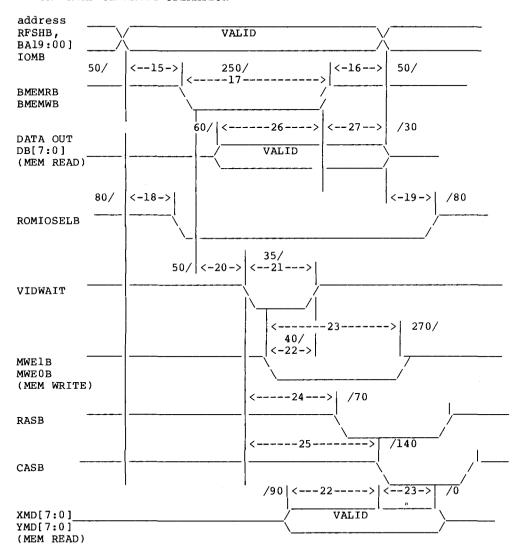

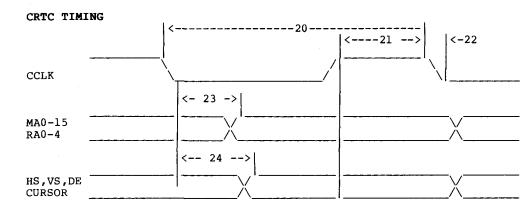

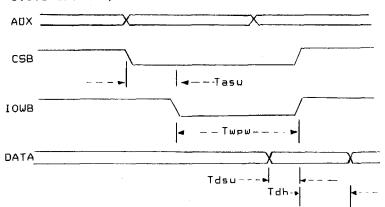

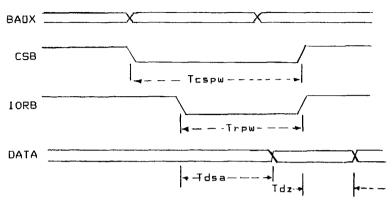

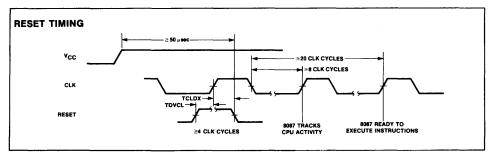

Figure 4. Tan to System Timing

## Tandy 1000 SX Theory of Operation

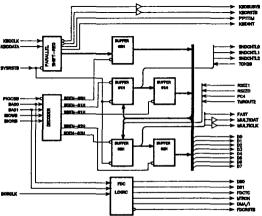

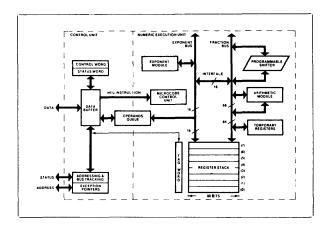

The block diagram for the Tandy 1000 SX (sheet 1 of the schematic) shows the main elements of the computer system. The most important single element is the Central Processor Unit (CPU). The other major elements of the Tandy 1000 SX are the Timing and CPU Control chip, the video interface, the Direct Memory Access controller (DMA) and system memory, system Read Only Memory (ROM), system timer (8253), expansion bus, and five input/output (I/O) interfaces (keyboard, printer, floppy disk, joystick, and sound).

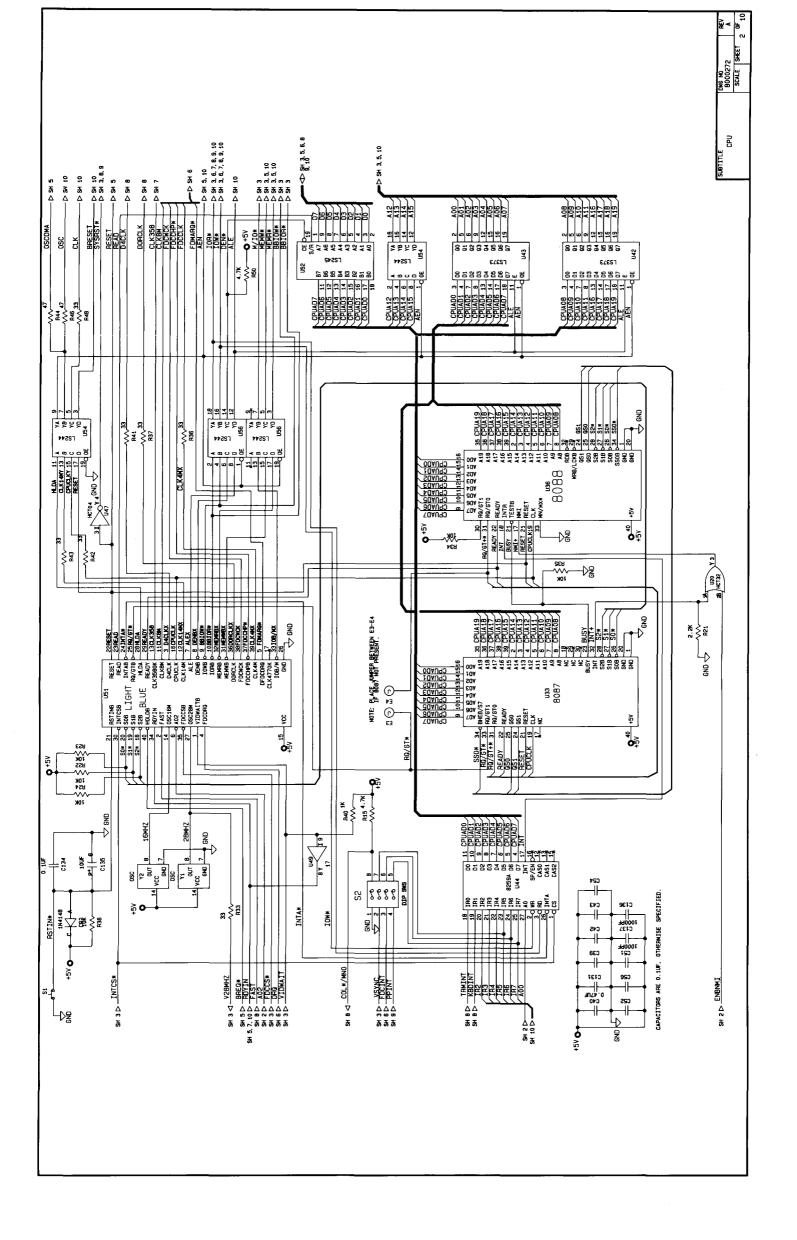

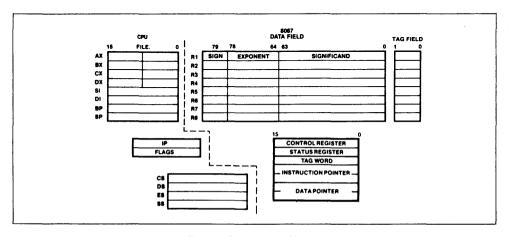

The CPU section of the Tandy 1000 SX consists of the 8088 CPU chip, the 8259A interrupt controller chip, and an optional 8087 numeric co-processor. These three devices share the CPU address/data bus, which is buffered before being supplied to the rest of the computer.

The CPU data bus is buffered by U52 (74LS245) before being supplied to the rest of the computer. The address bus is buffered as follows: 16 of 22 address bus lines are latched and buffered by U42 and U43 (74LS373). Four lines (Al2-Al5) are buffered by 1/2 of U54 (74LS244).

#### CPU Bus

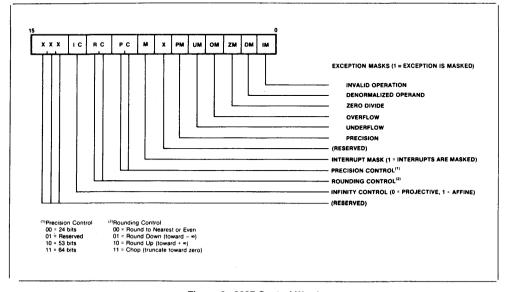

The 8087 numeric data co-processor option provides up to 100 times the performance of the CPU alone on numeric applications. To install this option in your Tandy 1000 SX, simply remove the jumper connecting E3 to E4 and install the 8087-2 part in the socket for U33.

Also on the CPU bus, the 8259A interrupt controller chip supplies the maskable interrupt input to the CPU. The 8259A has eight interrupt inputs controlled through software commands. It can mask (disable) and prioritize (arrange priority) to generate the interrupt input to the CPU. The eight interrupts are assigned as follows:

| #0 | Timer Channel 0        | Software Timer         |

|----|------------------------|------------------------|

| #1 | Keyboard               | Keyboard Code Receiver |

| #2 | Interrupt on the Bus   | Hard Disk Controller   |

| #3 | Interrupt on the Bus   | Modem                  |

| #4 | Interrupt on the Bus   | RS-232                 |

| #5 | Vertical Sync          | Optional Bus Interrupt |

| #6 | Floppy Disk Controller | Optional Bus Interrupt |

| #7 | Printer                | Optional Bus Interrupt |

#### --- TANDY COMPUTER PRODUCTS -

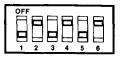

Interrupts 0 and 1 are connected to system board functions as indicated in the chart. Interrupts 2 - 4 are connected directly to the expansion bus, with the normally assigned functions listed in the chart. Interrupts 5 - 7 are connected through a switch to the system board function listed, and are also connected to the expansion bus. To use interrupt 5, 6, or 7 on the bus, the system board function must be disconnected (set the appropriate switch to off). Please note that disconnecting the normal system board function may cause some application programs to fail or operate incorrectly.

After being buffered, the CPU address/data bus is connected directly to the 5 expansion bus connectors. Also, the address bus is directly connected to the rest of the system board. The data bus is separately buffered by (U40) before being supplied to system board.

Ul8 is a programmed logic device that is used to provide the ROM chip select signal, enable gating for the non-maskable interrupt, and chip select and direction signals for U40 (the system board data buffer). Table 1 lists the equations for U40.

The Tandy 1000 SX uses a 128K ROM to store the BIOS and diagnostic operating code. The ROM chip select enables the ROM for the top 64K of memory (F0000 - FFFFFF).

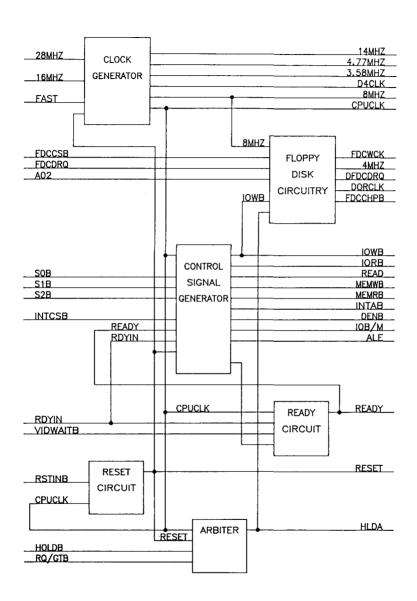

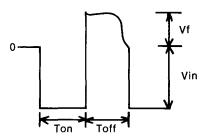

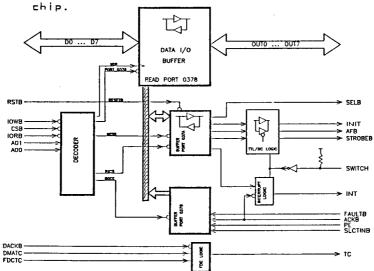

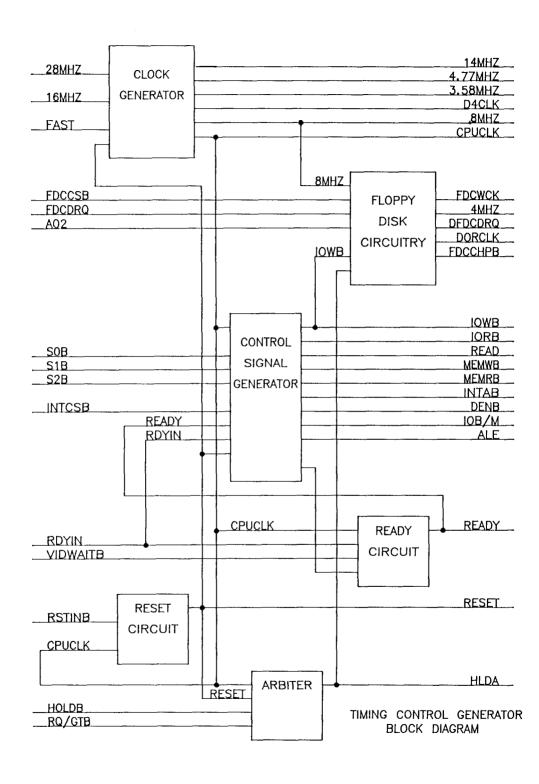

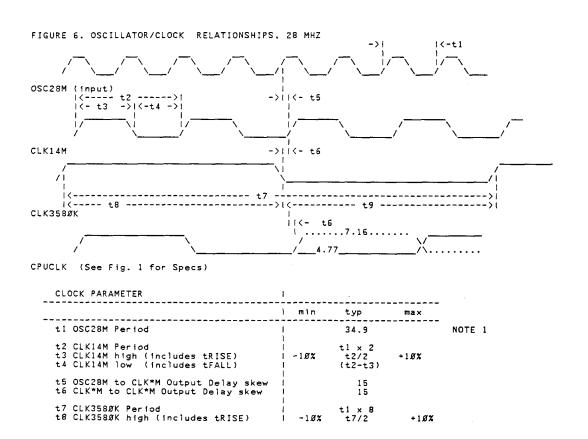

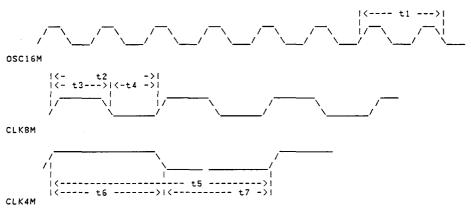

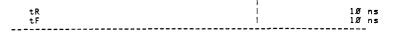

The next major functional block of the Tandy 1000 SX is the CPU control and timing chip (light blue). A block diagram of this 40 pin custom part is shown in Figure 5. This chip accepts 16MHz and 28.6 MHz clock signals from the master oscillator circuits and generates clocks for all of the other circuitry on the board. This chip also generates the system reset signal and derives the CPU control signals based on status inputs from the CPU chip. The last major function of this part is to generate timing signals and a chip select signal for the FDC.

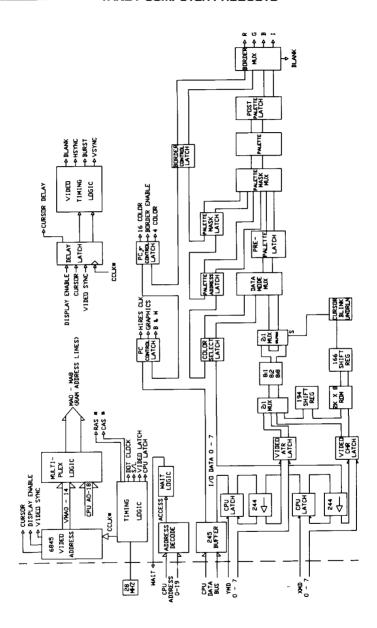

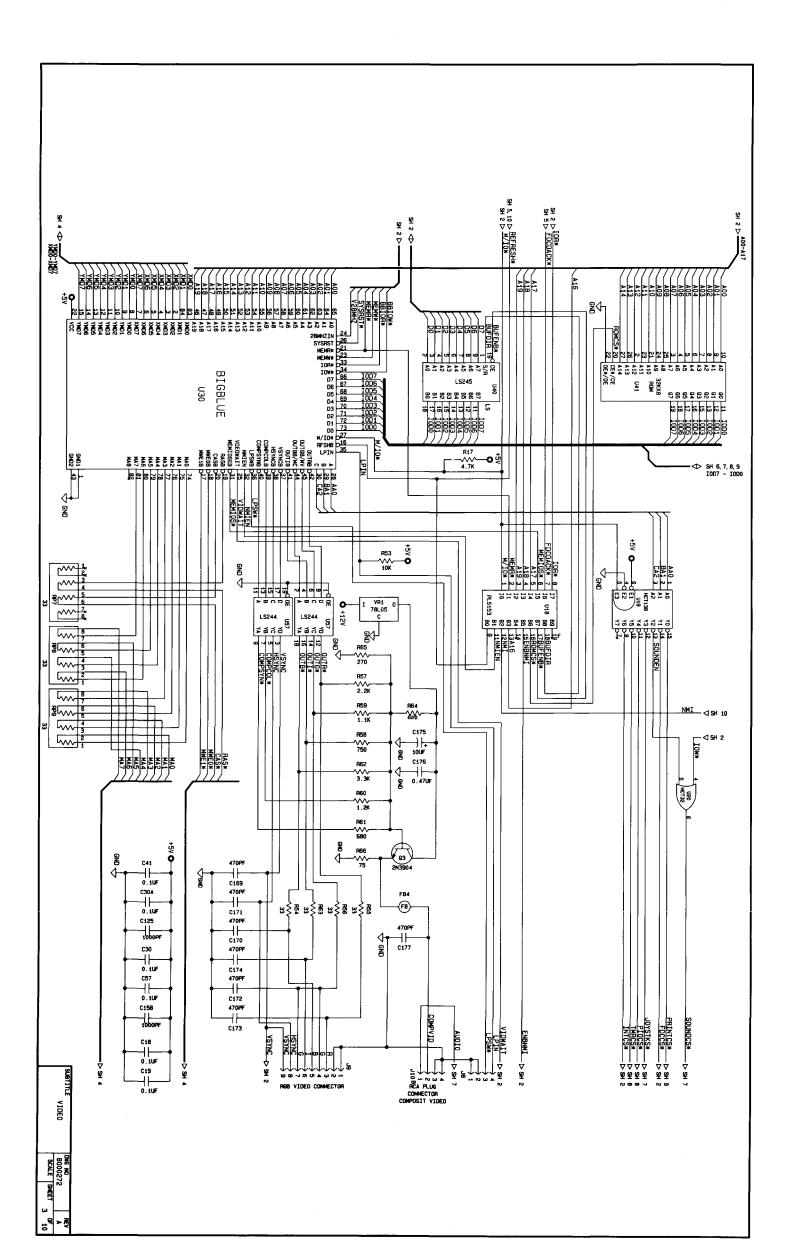

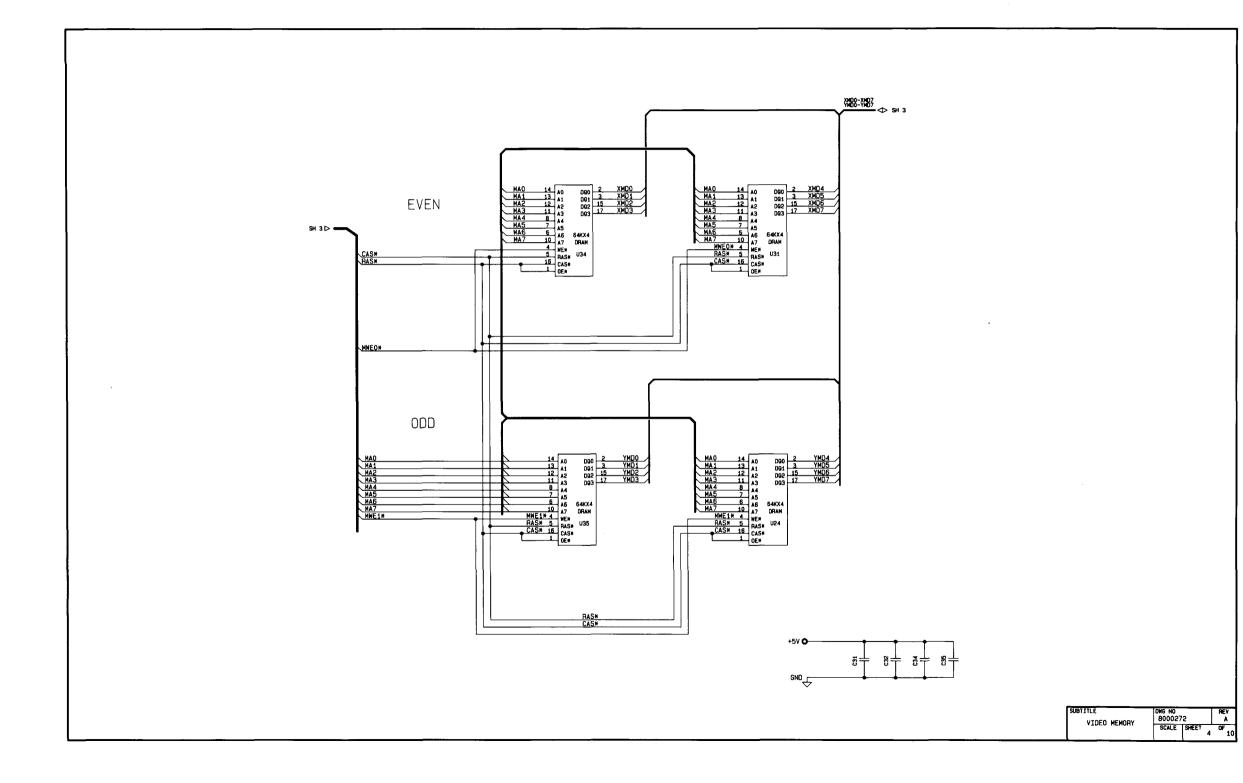

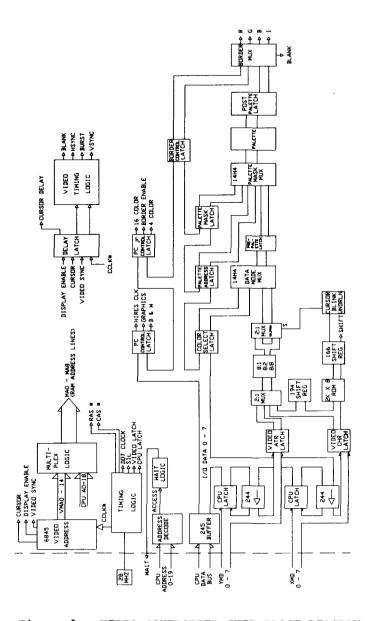

The next major block of the Tandy 1000 SX is the video interface circuitry. A block diagram of the video interface custom circuitry is shown in Figure 6. This custom part contains all of the logic necessary to generate an IBM compatible color video display. The video interface logic consists of the 84 pin custom video circuit, 4 - 64K X 4 RAMS, a 74LS244 buffer, and associated logic for generation of composite video.

#### System Control IFL

#### Inputs

```

PIN 1

!mio

=

PIN 2

=

!memr

PIN 3

=

a19

PIN 4

=

al8

PIN 5

=

al7

PIN 6

=

!memios

!fdcack

PIN 7

=

PIN 8

=

lior

PIN 9

!refresh

=

PIN 11

=

nmien

PIN 12

nmi

=

PIN 13

al6

=

```

#### Outputs

```

PIN 14 =

PIN 15 = enbnmi

PIN 16 = !romcs

PIN 17 = !bufenb

PIN 18 = bufdir

PIN 19 =

```

#### Logic Equations

Table 1

Figure 5. Timing Control Generator Block Diagram

Figure 6. Video Controller Block Diagram

The Tandy 1000 SX video interface circuitry controls 128K of memory. This RAM is shared by the CPU and the video. Normally, the video only requires 16K or 32K for the video screen and the remainder of the 128K is available for system memory uses.

The Tandy 1000 SX video interface custom circuit is composed of a 6845 equivalent design, dynamic RAM address generation/timing, and video attribute controller logic.

Normal functioning of the video interface custom circuit is as follows. After the 6845 is programmed with a correct set of operating values (Table 2), the address inputs to the dynamic RAMs are generated by a 4:1 multiplexer. This Mux switches between video (6845) addresses and CPU address as well as between row and column address. Also, the video interface chip provides the RAM timing signals and generates a wait signal to CPU for proper synchronization with the video RAM access cycles.

The outputs from the RAM chips are only connected to the video interface custom circuit, so all CPU read/write operations are buffered by this part. During a normal display cycle, video data from the RAM chips is first latched in the Video Attribute latch and the Video Character latch. The video interface requires a memory organization of 64K X 16 and will latch 16 bits of memory during each access to RAM. From the output of the two latches, the data is supplied to the character ROM for the Alpha modes or to the shift registers for graphics modes. A final 2:1 Mux is used to switch between foreground or background in the alpha modes.

From the 2:1 Mux the RGBI data is combined with the PC color select data and latched in the Pre-Palette latch. This latch synchronizes the RGBI data before it is used to address the Palette. The palette mask Mux is used to switch between incoming RGBI data and the palette address register. During a CPU write to the palette, this address register selects one of the 16 palette locations. Also, the Palette mask Mux allows any of the input RGBI bits to be set to zero.

The palette allows the 16 colors to be remapped in any desired organization. Normally, the palette is set for a 1:1 mapping (red = red, blue = blue, etc.) for PC compatibility. However, instantly changing the on-screen colors is a very powerful tool for animation or graphics programs.

Tandy 1000 SX Reference Manual

## PROGRAMMING TABLE FOR THE 6845 All Values in Hex (Decimal)

| Register<br>Address          | 40 x 25<br>Alpha  | 80 x 25<br>Alpha | Low Res.<br>Graphics | High Res.<br>Graphics | 40 x 25<br>Alpha | 80 x 25<br>Alpha | Low Res<br>Graphics | High Res<br>Graphics |

|------------------------------|-------------------|------------------|----------------------|-----------------------|------------------|------------------|---------------------|----------------------|

| UO Horizontal Total          | 38 (56)           | 71 (113)         | 38 (56)              | 71 (113)              | 38 (56)          | 71 (113)         | 38 (56)             | 71 (113)             |

| Horizontal<br>01 Displayed   | 28 (40)           | 50 (80)          | 28 (40)              | 50 (80)               | 28 (40)          | 50 (80)          | 28 (40)             | 50 (80)              |

| Horizontal                   |                   |                  |                      |                       |                  |                  |                     |                      |

| 02 Sync Position             | 2D (45)           | 59 (89)          | 2D (45)              | 59 (89)               | 2D (45)          | 59 (89)          | 2D (45)             | 59 (89)              |

| Horizontal<br>03 Sync Width  | 08 (8)            | 10 (16)          | 08 (8)               | 10 (16)               | 08 (8)           | 10 (16)          | 08 (8)              | 10 (16)              |

| 04 Vertical Total            | 1C (28)           | IC (28)          | 7F (127)             | 3F (63)               | lF (31)          | lF (31)          | 7F (127)            | 3F (63)              |

| Vertical<br>05 Total Adjust  | 01 (1)            | 01 (1)           | 06 (6)               | 06 (6)                | 06 (6)           | 06 (6)           | 06 (6)              | 06 (6)               |

| Vertical<br>06 Displayed     | 19 (25)           | 19 (25)          | 64 (100)             | 32 (50)               | 19 (25)          | 19 (25)          | 64 (100)            | 32 (50)              |

| Vertical<br>07 Sync Position | 1A (26)           | <br> 1A (26)     | 70 (112)             | 38 (56)               | 1C (28)          | 1C (28)          | 70 (112)            | 38 (56)              |

| 08 Interlace Mode            | <del>02 (2)</del> | 02 (2)           | 02 (2)               | 02 (2)                | 02 (2)           | 02 (2)           | 02 (2)              | 02 (2)               |

| Max Scan<br>09 Line Address  | 08 (8)            | 08 (8)           | 01 (1)               | 03 (3)                | 07 (7)           | 07 (7)           | 01 (1)              | 03 (3)               |

| 10 Cursor Start              | 06 (6)            | 06 (6)           | 06 (6)               | 06 (6)                | 06 (6)           | 06 (6)           | 06 (6)              | 06 (6)               |

| 11 Cursor End                | 07 (7)            | 07 (7)           | 07 (7)               | 07 (7)                | 07 (7)           | 07 (7)           | 07 (7)              | 07 (7)               |

| Start<br>12 Address (High)   | 00 (0)            | 00 (0)           | 00 (0)               | 00 (0)                | 00 (0)           | 00 (0)           | 00 (0)              | 00 (0)               |

| Start<br>13 Address (Low)    | 00 (0)            | 00 (0)           | 00 (0)               | 00 (0)                | 00 (0)           | 00 (0)           | 00 (0)              | 00 (0)               |

| Monitor                      | l<br>Mode         | '——              | l                    | TV Mode               | I                | 1                | ·                   | ıi                   |

Table 2

After the Palette, the RGBI data is resynchronized in the Post Palette register. The final logic before the RGBI data is buffered off the chip is the Border Mux. This Mux allows the Border to be replaced with any color selected by the border color latch. This latch is normally disabled in PC modes, but it is used in all PC jr modes.

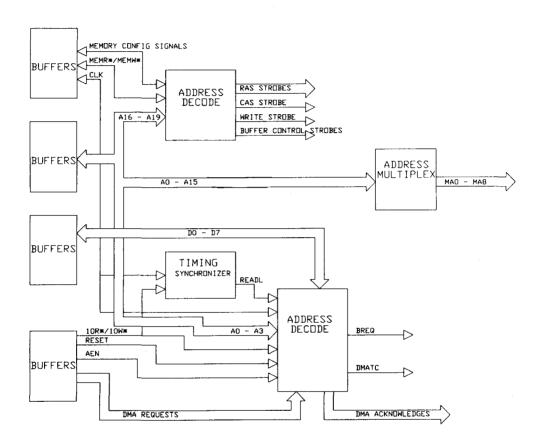

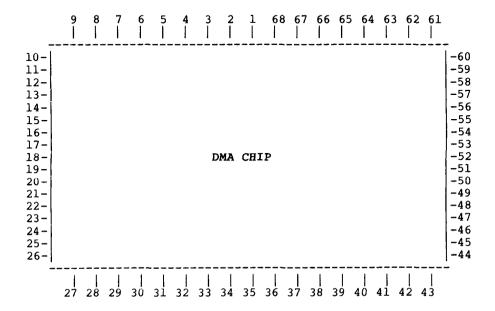

The next major functional block in the Tandy 1000 SX is the DMA/Memory controller chip. A block diagram for this part is shown in Figure 7. This custom part is composed of the equivalent of an 8237A-5 Direct Memory Access chip and a small amount of additional logic to complete the DMA function. Also, this chip provides timing and refresh addresses to the system memory. In the Tandy 1000 SX, this system memory is 256K and may be expanded to 512K of memory (with the video/system memory, this is a total of 640K on the main logic board). To expand the memory to 640K total, simply remove the jumper connecting El to E2 and add the 8 additional RAM chips in Bank 1.

The final system function other than I/O is the 8253 timer chip. This part is composed of three independent programmable counters. The clock for all three counters is 1.1925 MHz. Counter 0 and 1 are permanently enabled. Counter 2 is controlled by port Hex 0062, bit 0. Counter #0 is connected to system interrupt #0 and is used for software timing functions. Counter #1 is used for timing of the refresh function. Counter 2 is connected to the sound circuit and also to port Hex 0061, bit 5.

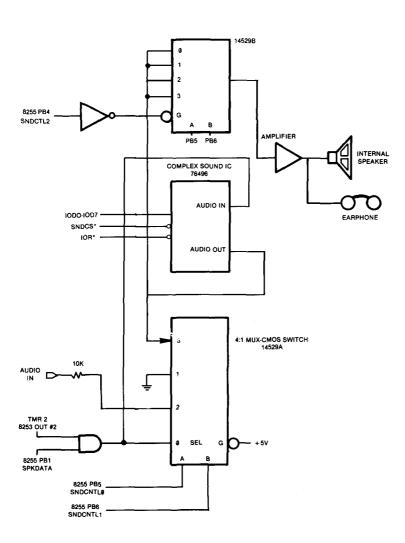

The sound circuit is one of the five I/O functions of the Tandy  $1000~\rm SX$ . The circuit provides sound output for the internal speaker and also for an external sound circuit. A functional block diagram of this circuit is shown in Figure 8.

The main source of sound in the Tandy 1000 SX is the 76496 complex sound generator. This device has 3 tone generators and 1 white noise generator. Each tone generator may be programmed for frequency and attenuation. Also, this device has an audio input pin which is connected to the gated output of timer channel 2. This audio input signal is mixed with the sound generator signal and supplied to the audio output pin.

From the output of the 76496, the sound signal is connected to a dual analog multiplexer. The multiplexer is switched by port 61, bits 5 and 6. One section of the multiplexer is used for the internal speaker, and the other section is used for the external audio signal. The section controlling the internal speaker may be disabled by port 61, bit 4.

Figure 7. DMA/Memory Controller Chip Block Diagram

Figure 8. Sound Functional Block Diagram

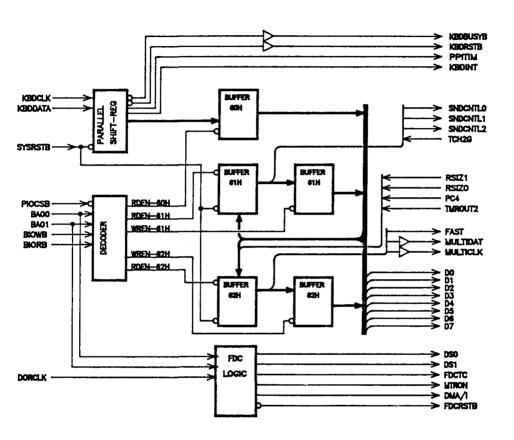

The next I/O function of the Tandy 1000 SX is the Keyboard interface custom circuit. A block diagram of this part is shown in Figure 9. The heart of this custom part is several read-write registers that are used to control the keyboard interface logic, sound circuitry, and FDC circuitry. For the interface to the keyboard connector, a 164 type shift register is used to load the serial data and allow the CPU to read it as 8 parallel bits. The FDC circuitry consists of a write-only latch for the FDC control signal plus additional circuitry to allow the 2 drive select signals to be switched.

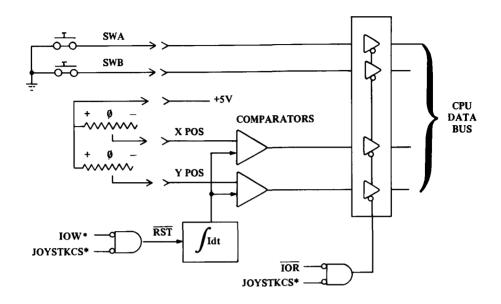

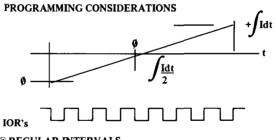

#### Joystick Interface

The joystick interface converts positional information from hand-held joysticks (1 or 2) into CPU data. Each joystick provides 1 or 2 push-buttons and X,Y position for a total of 4 bits each. You can use 2 joysticks. The joystick handle is connected to two potentiometers mounted perpendicular to each other; one for X position, one for Y position. Through the cable, the main logic board applies +5 VDC to one side and ground to the other of the pots. The pot wiper is the position signal: a voltage between 0 and +5 VDC. This signal is applied to one input of a comparator Ul7. The other comparator input is the reference signal ( a ramp between 0.0 to +5.0 volts.) When the position signal is equal or less than the reference signal, the comparator output goes true. This comparator output is the X or Y position data bit. The ramp is reset to 0.0 VDC whenever a "write" is made at Port 200/201 Hex. The IOW\* signal turns on Q2, which drains Cl18 to 0.0 volts. When Q2 is turned off, Q1, R12, R13, R14, and CR1 create a constant-current source that linearly charges Cl18 to +5.0 VDC in 1.12 milliseconds. The joystick information is "read" by the CPU at Port 200/201 Hex through U21. See Figure 10.

One of the most important I/O functions of the Tandy 1000 SX is the floppy disk interface. This I/O function consists of the 765 controller and support circuitry. In the Tandy 1000 SX, the support circuitry is broken up and located in several of the other custom circuits. The clock and chip select signals for the rest of the FDC circuit are generated by Light Blue. The motor on and drive select signals are supplied from the keyboard interface custom circuit. Also, the logic to switch between the DMA terminal count and the CPU terminal count is located in the printer interface custom chip.

Figure 9. Keyboard Interface Block Diagram

@ REGULAR INTERVALS

ONCE TRIGGERED BY SOFTWARE THE INTERGRATOR CIRCUIT PRODUCES A PULSE THE DURATION OF WHICH IS DEPENDENT ON JOYSK POSITION.

Figure 10. Joystick Interface Block Diagram

#### ----- TANDY COMPUTER PRODUCTS --

The bulk of the FDC interface is handled by the 765 controller chip and the 9216 digital data separator. The 765 generates write data which has pre-compensation added by U50. Read data from the floppy drive is separated into data and clock for the 765 by the 9216 data separator.

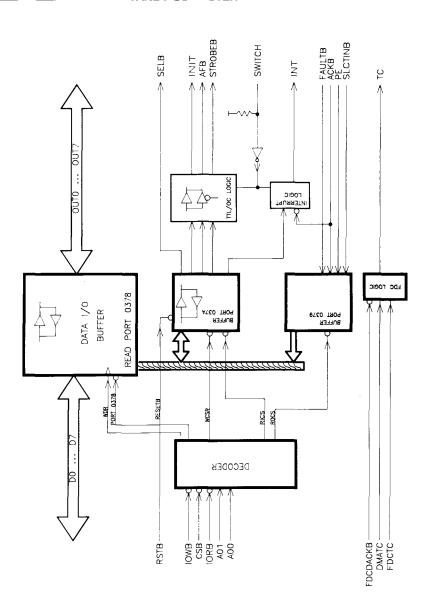

The final I/O interface of the Tandy 1000 SX is the Printer Interface, shown in block diagram form in Figure 11. This part supplies all of the signals required to interface to a typical parallel printer. These signals are 8 data out lines, plus various handshake control signals. Also, the printer interface will generate an interrupt to the CPU if enabled.

Figure 11. Printer Interface Block Diagram

\_\_\_\_ TANDY COMPUTER PRODUCTS —

## 1/O MAP SUMMARY

| Block                                                                                                                          | Usage                                                                              | Function                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000-001F<br>0020-003F<br>0040-005F<br>0060-007F<br>0080-009F<br>00A0-00BF<br>00C0-00DF<br>00E0-01FF<br>0200-020F<br>0210-031F | 0000-000F<br>0020-0021<br>0040-0043<br>0060-0063<br>0080-0083<br>00A0<br>00C0-00C1 | DMA Function Interrupt Controller Timer PIO Function DMA Page Register NMI Mask Register Sound Generator Reserved Joystick Interface Reserved                            |

| 0320-032F<br>0330-036F<br>0370-037F<br>0380-03CF<br>03D0-03DF                                                                  | 0378-037B<br>All                                                                   | Reserved Hard Disk<br>Not Assigned<br>Printer<br>Not Used<br>System Video                                                                                                |

| 03E0-03EF<br>03F0-03FF<br>0400-FFFF                                                                                            | 03F2,F4,F5                                                                         | Reserved<br>Floppy Disk Controller<br>Not Usable                                                                                                                         |

| Address<br>0000                                                                                                                | Internal<br>Internal<br>IOR* = 0: Chan<br>Internal                                 | nnel 0 Base and Current Address Flip/Flop = 0: Write A0-A7 Flip/Flop = 1: Write A8-A15 nnel 0 Current Address Flip/Flop = 0: Read A0-A7 Flip/Flop = 1: Read A8-A15       |

| 0001                                                                                                                           | Internal<br>Internal<br>IOR* = 0: Chan<br>Internal                                 | nnel 0 Base and Current Word Count Flip/Flop = 0: Write W0-W7 Flip/Flop = 1: Write W8-W15 nnel 0 Current Word Count Flip/Flop = 0: Read W0-W7 Flip/Flop = 1: Read W8-W15 |

| 0002                                                                                                                           | Internal<br>Internal<br>IOR* = 0: Chan<br>Internal                                 | nel l Base and Current Address Flip/Flop = 0: Write A0-A7 Flip/Flop = 1: Write A8-A15 nel l Current Address Flip/Flop = 0: Read A0-A7 Flip/Flop = 1: Read A8-A15         |

| Address | Description                                                               |

|---------|---------------------------------------------------------------------------|

| 0003    | <pre>DMA Controller IOW* = 0: Channel l Base and Current Word Count</pre> |

| 0004    | <pre>DMA Controller IOW* = 0: Channel 2 Base and Current Address</pre>    |

| 0005    | <pre>DMA Controller IOW* = 0: Channel 2 Base and Current Word Count</pre> |

| 0006    | <pre>DMA Controller IOW* = 0: Channel 3 Base and Current Address</pre>    |

| 0007    | <pre>DMA Controller IOW* = 0: Channel 3 Base and Current Word Count</pre> |

| 0008                                   | DMA Controller IOW* = 0, Write Command Register                                                                                                                                                                                 |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit                                    | Description                                                                                                                                                                                                                     |

| 0                                      | 0 = Memory to Memory Disable                                                                                                                                                                                                    |

| 1                                      | <pre>1 = Memory to Memory Enable 0 = Channel 0 Address Hold Disable 1 = Channel 0 Address Hold Enable X</pre>                                                                                                                   |

| 2                                      | 0 = Controller enable 1 = Controller disable                                                                                                                                                                                    |

| 3                                      | 0 = Normal timing<br>1 = Compressed timing<br>X If bit 0 = 1                                                                                                                                                                    |

| 4                                      | 0 = Fixed priority<br>1 = Rotating priority                                                                                                                                                                                     |

| 5                                      | 0 = Late write selection<br>1 = Extended write selection<br>X = If bit 3 = 1                                                                                                                                                    |

| 6                                      | <pre>0 = DREQ sense active high 1 = DREQ sense active low</pre>                                                                                                                                                                 |

| 7                                      | 0 = DACK sense active low<br>1 = DACK sense active high                                                                                                                                                                         |

|                                        | IOR* = 0, Read Status Register                                                                                                                                                                                                  |

| Bit<br>0<br>1<br>2<br>3<br>4<br>5<br>6 | Description  1 = Channel 0 has reached TC  1 = Channel 1 has reached TC  1 = Channel 2 has reached TC  1 = Channel 3 has reached TC  1 = Channel 0 Request  1 = Channel 1 Request  1 = Channel 2 Request  1 = Channel 3 Request |

| 0009                                   | DMA Controller IOW* = 0, Write Request Register                                                                                                                                                                                 |

| Bit<br>0-1                             | Description Bitl Bit0 0 0 Select channel 0 0 1 Select channel 1 1 0 Select channel 2 1 1 Select channel 3                                                                                                                       |

| 2                                      | 0 Reset request bit                                                                                                                                                                                                             |

| 3-7                                    | <pre>1 Set request bit Don't Care IOR* = 0, Illegal</pre>                                                                                                                                                                       |

| 000A                   | DMA Controller IOW* = 0, Write Single Mask Register                                                                                                                                                                                            |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit<br>0-1<br>2<br>3-7 | Description Bitl Bit0 0 0 Select channel 0 mask bit 0 1 Select channel 1 mask bit 1 0 Select channel 2 mask bit 1 1 Select channel 3 mask bit 0 Clear mask bit (Disable Channel) 1 Set mask bit (Disable Channel) Don't care IOR* = 0, Illegal |

| 000в                   | DMA Controller IOW* = 0, Write Mode Register                                                                                                                                                                                                   |

| Bit<br>0-1             | Description Bitl Bit0 0 0 Channel 0 select 0 1 Channel 1 select 1 0 Channel 2 select 1 1 Channel 3 select                                                                                                                                      |

| 2-3                    | Bit3 Bit2 0 0 Verify transfer 0 1 Write transfer to memory 1 0 Read transfer to memory 1 1 Illegal                                                                                                                                             |

| 4                      | 0 Autoinitialization disable                                                                                                                                                                                                                   |

| 5                      | 1 Autoinitialization enable<br>0 Address increment select                                                                                                                                                                                      |

| _                      | 1 Address decrement select                                                                                                                                                                                                                     |

| 6-7                    | Bit7 Bit6 0 0 Demand mode select 0 1 Single mode select 1 0 Block mode select 1 1 Cascade mode select IOR* = 0, Illegal                                                                                                                        |

| 000C                   | DMA Controller IOW* = 0, Clear Byte Pointer Flip/Flop IOR* = 0, Illegal                                                                                                                                                                        |

| 000D        | <pre>DMA Controller IOW* = 0, Master Clear IOR* = 0, Read Temporary Register</pre> |

|-------------|------------------------------------------------------------------------------------|

| 000E        | <pre>DMA Controller IOW* = 0, Clear Mask Register IOR* = 0, Illegal</pre>          |

| 000F        | DMA Controller IOW* = 0, Write all Mask Register Bits                              |

| Bit         | Description                                                                        |

| 0           | 0 = Clear channel 0 mask bit (Enable)                                              |

| ŭ           | l = Set channel 0 mask bit (Disable)                                               |

| 1           | 0 = Clear channel 1 mask bit (Enable)                                              |

| -           | 1 = Set channel 1 mask bit (Disable)                                               |

| 2           | 0 = Clear channel 2 mask bit (Enable)                                              |

| -           | 1 = Set channel 2 mask bit (Disable)                                               |

| 3           | 0 = Clear channel 3 mask bit (Enable)                                              |

| •           | <pre>1 = Set channel 3 mask bit (Disable)</pre>                                    |

| 4-7         | Don't care                                                                         |

|             | IOR* = Illegal                                                                     |

| 0010 - 001F | Not Used                                                                           |

| Address     | Description                                                                        |

| 0020        | 8259A Interrupt Controller                                                         |

|             |                                                                                    |

Note: Initialization Words are setup by the operating system and are generally not to be changed.

Writing an initialization word may cancel pending interrupts.

Bit4 = 1: INITIALIZATION COMMAND WORD 1

Bit0 = 0: ICW4 needed

= 1: ICW4 not needed

Bit1 = 0: Cascade Mode

= 1: Single

Bit2 = Not used

Bit3 = 0: Edge Triggered Mode

= 1: Level Triggered Mode

when the SL bit is active

Bit5 - 7: Not Used

```

Bit 4 = 0 &

OPERATION CONTROL WORD 2

Bit0 - 2: Determine the interrupt level acted on

Bit3 = 0

when the SL bit is active

Interrupt Level = 0 1 2 3 4 5 6 7

Bit0 (L0): 0 1 0 1 0 1 0 1

Bitl (Ll):

0 0 1 1 0 0 1 1

Bit2 (L2):

0 0 0 0 1 1 1 1

Control Rotate and End of Interrupt

Bit5 - 7

modes

B7 B6 B5

End of Interrupt

Non-specific EOI command

0

End of Interest

0

1

Specific EOI command

Rotate on non-specific EOI command

Automatic Rotation

1

0

Rotate in Automatic EOI Mode (set)

Automatic Rotation

1

0

0

Automatic Rotation

0

Rotate in Automatic EOI Mode (clear)

0

0

*Rotate on Specific EOI command

1

Specific Rotation

1

1.

Specific Rotation

1

1

*Set priority command

0

1

0

No operation

*LO - L2 are used

Bit4 = 0 &

OPERATION CONTROL WORD 3

Bit3 = 1

Bit0 - 1:

Bitl Bit0- Read Register Command

0 - No Action

1 - No Action

O

0 - Read IR Register on next IOR* Pulse

1

1 - Read IS Register on next IOR* Pulse

Bit2 = 0: No Poll Command

= 1: Poll Command

Bit5 - 6:

Bit6 Bit5- Special Mask Mode

0 - No Action

0

1 - No Action

0 - Reset Special Mask

1 - Set Special Mask

Bit7 = 0

```

OPERATION CONTROL WORD 1 (IOR\*/IOW\*)

Bit0 - 7: Interrupt Mask for IRQ0 - IRQ7

=0 Mask Reset (Enable)

=l Mask Set (Disable)

NOTE: Peripherals Requesting an interrupt service must generate a low to high edge and then remain at a logic high level service, must generate a low to high edge and then remain at a high until service is acknowledged. Failure to do so will result in a Default Service for IRQ7

```

0022-003F

Not Used

Address

Description

0040/0044

8253-5 Timer

IOW* = 0: Load Counter No. 0

IOR* = 0:

Read Counter No. 0

8253-5 Timer

0041/0045

IOW* = 0: Load Counter No. 1

IOR* = 0:

Read Counter No. 1

Address

Description

0040/0044

8253-5 Timer

IOW* = 0: Load Counter No. 0

IOR* = 0:

Read Counter No. 0

8253-5 Timer

0041/0045

IOW* = 0: Load Counter No. 1

IOR* = 0:

Read Counter No. 1

8253-5 Timer

0042/0046

IOW* = 0: Load Counter No. 2

IOR* = 0: Read Counter No. 2

8253-5 Timer

0043/0047

IOW* = 0: Write Mode Word

Control Word Format

Bit0: BCD

= 0: BCD Counter (4 Decades)

= 1: Binary Counter 16 bits

BIT1 - 3: Mode Selection

Bit3 Bit2 Bit1

Mode 0

0

0

0

0

0

0

Mode 1

X

1

O

Mode 2

1

Mode 3

Х

1

0

0

Mode 4

1

1

0

1

Mode 5

BIT4 - 5:

Read/Load

Bit5 Bit4

Counter Latching Operation

0

n

O

1

Read/Load LSB only

1

Read/Load MSB only

n

1

1

Read/Load LSB first, then MSB

BIT6 - 7:

Select Counter

Bit7 Bit6

0

0

Select Counter 0

0

1

Select Counter 1

Select Counter 2

1

0

1

1

Illegal

IOR* = 0:

No-Operation 3-State

0048-005F

Not Used

```

| 0060      | PORT A / KEYBOARD INTERFACE CONTROL PORTS                 |

|-----------|-----------------------------------------------------------|

| ВІТ       | (READ ONLY) Description                                   |

| 0         | Keyboard Bit 0-LSB                                        |

| ì         | Keyboard Bit 1                                            |

| 2         | Keyboard Bit 2                                            |

| 3         | Keyboard Bit 3                                            |

| 4         | Keyboard Bit 4                                            |

| 5         | Keyboard Bit 5                                            |

| 6         | Keyboard Bit 6                                            |

| 7         | Keyboard Bit 7-MSB                                        |

| 0061      | PORT B - READ or WRITE                                    |

| BIT       | Description                                               |

| 0         | 1 = 8253 Gate #2 Enable                                   |

| 1 2       | 1 = Speaker Data Out Enable                               |

| 3         | Not Used<br>Not Used                                      |

| 4         | l = Disable Internal Speaker                              |

| •         | (Sound Control 2)                                         |

| 5         | 0 = Sound Control 0                                       |

| 6         | <pre>0 = Sound Control l</pre>                            |

| 7         | <pre>l = Keyboard Clear</pre>                             |

| 0062      | PORT C - READ/WRITE: Bits 0-3; READ ONLY:                 |

|           | BITS 4-7                                                  |

| BIT       | Description                                               |

| 0         | (Output) Not Used                                         |

| 1         | (Output) Multi-Data                                       |

| 2 3       | (Output) Multi-Clock                                      |

| 3         | (Output) CPU Clock Rate 0 = 4.77 MHz (PC Compatible Rate) |

|           | 1 = 7.16 MHz (Default by Boot ROM)                        |

| 4         | Video Ram Size                                            |

| -         | 0 = 128K Video                                            |

|           | 1 = 256K  Video                                           |

| 5         | 8253 Out #2                                               |

| 6         | Monochrome Mode                                           |

|           | 0 = Color Monitor                                         |

| 7         | 1 = 350 Line Monitor, Mono                                |

| 7         | 0 = Reserved                                              |

| 0063-007F | Not Used                                                  |

| Address   | Description                                               |

| 0800      | DMA Page Reg. (Not Used)                                  |

|           | DMA rage keg. (Not osed)                                  |

| O081 Address Bit 0 Bit 1 Bit 2 Bit 3 Bit 4 Bit 5 Bit 6 Bit 7 | WRITE ONLY Description DMA Ch 2 Address A16 DMA Ch 2 Address A17 DMA Ch 2 Address A18 DMA Ch 2 Address A19 Not Used Not Used Not Used Not Used                                                                                                          |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| O082 Address Bit 0 Bit 1 Bit 2 Bit 3 Bit 4 Bit 5 Bit 6 Bit 7 | WRITE ONLY  Description  DMA Ch 3 Address Al6  DMA Ch 3 Address Al7  DMA Ch 3 Address Al8  DMA Ch 3 Address Al9  Not Used  Not Used  Not Used  Not Used                                                                                                 |

| O083 Address Bit 0 Bit 1 Bit 2 Bit 3 Bit 4 Bit 5 Bit 6 Bit 7 | WRITE ONLY  Description  DMA Ch 0 - 1 Address Al6  DMA Ch 0 - 1 Address Al7  DMA Ch 0 - 1 Address Al8  DMA Ch 0 - 1 Address Al8  DMA Ch 0 - 1 Address Al9  Not Used  Not Used  Not Used  Not Used                                                       |

| 0084-008F                                                    | Not Used                                                                                                                                                                                                                                                |

| 00A0-00A7                                                    | NMI Mask Register, Write only                                                                                                                                                                                                                           |

| Bit<br>0<br>1<br>2<br>3<br>4<br>5<br>6<br>7                  | Description External Video 0 = Normal Operation 1 = All Video Addresses and Ports are Disabled MEMCONFIG 1 - Al7 128K SW MEMCONFIG 2 - Al8 256K SW MEMCONFIG 3 - Al9 512K SW "I" Enable 256K of Video RAM Not Used Not Used 1 = Enable NMI 0 = Disabled |

| BIT<br>4 | <b>BIT</b><br>3 | <b>BIT</b> 2 | BIT<br>1 | <b>MEMORY</b><br>START | MRMORY<br>LENGTH | MEMORY<br>RANGE |

|----------|-----------------|--------------|----------|------------------------|------------------|-----------------|

| 256K     | 3.10            | .10          | 217      |                        |                  |                 |

| Enable   | A19<br>0        | A18<br>0     | A17<br>0 | 0 0000                 | 128K             | 0 0000-1 FFFF   |

| 0        | 0               | 0            | i        | 2 0000                 | 128K             | 2 0000-3 FFFF   |

| ŏ        | Ŏ               | ĭ            | ō        | 4 0000                 | 128K             | 4 0000-5 FFFF   |

| Ō        | 0               | 1            | 1        | 6 0000                 | 128K             | 6 0000-7 FFFF   |

| 0        | 1               | 0            | 0        | 8 0000                 | 128K             | 8 0000-9 FFFF   |

| 1        | 0               | 0            | 1        | 0 0000                 | 256K             | 0 0000-3 FFFF   |

| 1        | 0               | 1            | 0        | 2 0000                 | 256K             | 2 0000-5 FFFF   |

| 1        | 0               | 1            | 0        | 4 0000                 | 256K             | 4 0000-7 FFFF   |

| 1        | 1               | 0            | 0        | 6 0000                 | 256K             | 6 0000-9 FFFF   |

NOTE: To turn off on-board video, be sure Port AOH, Data Bit 0 is a "1" AND Video Array Register 3 (Selected by writing 03 into 3DAH) Data Bit 0 (Write to Port 3DEH) must be = "0" to disable 3B8H and 3BAH.

00A8 - 00AF Not Used

Description Address Sound SN76496 00C0-00C7

| Bit7 | Bit6 | Bit5          | Bit4 | Bit3 | Bit2       | Bitl | Bit0       |                           |

|------|------|---------------|------|------|------------|------|------------|---------------------------|

| = 1  | 0    | 0             | 0    | F6   | F7         | F8   | F9         | Update Tone Frequency 1   |

| = 0  | Х    | $\mathbf{F0}$ | Fl   | F2   | F3         | F4   | F5         | Additional Frequency Data |

| = 1  | 0    | 0             | 1    | A0   | Al         | A2   | A3         | Update Tone Attenuation 1 |

| = 1  | 0    | 1             | 0    | F6   | F7         | F8   | F9         | Update Tone Frequency 2   |

| = 0  | X    | F0            | Fl   | F2   | <b>F</b> 3 | F4   | F5         | Additional Frequency Data |

| = 1  | 0    | 1             | 1    | A0   | Al         | A2   | <b>A</b> 3 | Update Tone Attenuation 2 |

| = 1  | 1    | 0             | 0    | F6   | F7         | F8   | F9         | Update Tone Frequency 3   |

| = 0  | X    | F0            | Fl   | F2   | F3         | F4   | F5         | Additional Frequency Data |

| = 1  | 1    | 0             | 1    | A0   | Al         | A2   | <b>A</b> 3 | Update Tone Attenuation 3 |

| = 1  | 1    | 1             | 0    | Х    | FB         | NFO  | NFI        | Update Noise Control      |

| = 1  | 1    | 1             | 1    | AO   | Al         | A2   | A3         | Update Noise Attenuation  |

| 00C8-00DF    | Not Used      |            |    |       |

|--------------|---------------|------------|----|-------|

| 00E0-01FF    | Reserved      |            |    |       |

| WRITE (IOW*) |               |            |    |       |

| 0200 - 0207  | Joystick      |            |    |       |

|              | Clear (Resets | Integrator | to | Zero) |

| 0208 - 020F  | Not Used      | _          |    |       |

7

```

0201 READ

R = Right Joystick, L = Left Joystick

Bit

Description

R - X Horizontal Position

0

1

R - Y Vertical Position

2

L - X Horizontal Position

3

L - Y Vertical Position

4

R Button #1 (Logic 0 = Button Depressed)

R Button #2 (Logic 0 = Button Depressed)

5

6

L Button #1 (Logic 0 = Button Depressed)

7

L Button #2 (Logic 0 = Button Depressed)

Addresses

0370 - 0377

Not Used

0378

Printer - Data Latch

Bit

Description

Data Bit 0 - LSB

0

1

Data Bit 1 -

2

Data Bit 2 -

3

Data Bit 3 -

4

Data Bit 4 -

5

Data Bit 5 -

6

Data Bit 6 -

7

Data Bit 7 - MSB

0379

Printer - Read Status

Bit

Description

Not Used

0

1

Not Used

2

Not Used

3

0 = Error

4

l = Printer Select

5

0 = \text{End of Form}

0 = Acknowledge

6

7

0 = Busy

037A (037E)

Printer - Control Latch

Bit

Description

0

0 = Strobe

1

0 = Auto FD XT

0 = Initialize

2

3

0 = Select Printer

4

l = Enable Interrupt

5

0 = Enable Output Data

6

Not Used

```

Not Used

| 037B<br>037C<br>037D<br>037F - 03D3      | Not Used<br>Printer - Data Latch<br>Printer - Read Status<br>Not Used                                                        |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 03D4<br>03D5<br>03D6<br>03D7             | 6845 Address Register<br>6845 Data Register<br>Not Used<br>Not Used                                                          |

| 03D8<br>Bit 0                            | Mode Select Register High Resolution Clock =0: Selects 40 by 25 Alphanumeric Mode =1: Selects 80 by 25 Alphanumeric Mode     |

| Bit 1                                    | Graphics Select<br>=0: Selects Alphanumeric Mode                                                                             |

| Bit 2                                    | =1: Selects 320 by 200 Graphics Mode Black and White =0: Selects Color Mode                                                  |

| Bit 3                                    | =1: Selects Black and White Mode Video Enable =0: Disables Video Signal                                                      |

| Bit 4                                    | =1: Enables Video Signal 640 Dot Graphics =0: Disables 640 by 200 B&W Graphics Mode                                          |

| Bit 5                                    | <pre>=1: Enables 640 by 200 B&amp;W Graphics Mode Blink Enable =0: Disables Blinking =1: Enables Blinking</pre>              |

| 03D9 Bit 0 Bit 1 Bit 2 Bit 3 Bit 4 Bit 5 | Color Select Register Background Blue Background Green Background Red Background Intensity Foreground Intensity Color Select |

| 03DA, 03DE                               | Write Video Array Address & Read Status (3DA) Write Video Array Data (3DE)                                                   |

| READ (3DA)<br>00 Bit 0<br>00 Bit 1<br>00 Bit 2<br>00 Bit 3<br>00 Bit 4 | Display Inactive<br>Light Pen Set<br>Light Switch Status<br>Vertical Retrace<br>Not Used                                                                                                   | WRITE (3DE) Not Used Not Used Not Used Not Used Not Used Not Used                                   |

|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| 01 Bit 0<br>01 Bit 1<br>01 Bit 2<br>01 Bit 3                           |                                                                                                                                                                                            | Palette Mask 0<br>Palette Mask 1<br>Palette Mask 2<br>Palette Mask 3                                |

| 02 Bit 0<br>02 Bit 1<br>02 Bit 2<br>02 Bit 3<br>02 Bit 5               |                                                                                                                                                                                            | Border Blue<br>Border Green<br>Border Red<br>Border Intensity<br>Reserved = 0                       |

| 03 Bit 0<br>03 Bit 1<br>03 Bit 2<br>03 Bit 3<br>03 Bit 4<br>03 Bit 5   |                                                                                                                                                                                            | Mono Enable = "1" Reserved = 0 Border Enable 4-Color High Resolution 16 Color Mode Extra Video Mode |

| 10-1F Bit 0<br>10-1F Bit 1<br>10-1F Bit 2<br>10-1F Bit 3<br>Bits 4 - 7 |                                                                                                                                                                                            | Palette Blue<br>Palette Green<br>Palette Red<br>Palette Intensity<br>Not Used                       |

| 03DB<br>03DC                                                           | Clear Light Pen Latch<br>Preset Light Pen Latch                                                                                                                                            | (Not Used on Tandy 1000 EX)<br>(Not Used on Tandy 1000 EX)                                          |

| 03DD<br>Bit<br>0<br>1<br>2<br>3<br>4<br>5<br>6                         | Extended Ram Page Reginescription Extended Addressing Monot Used Not Used CRT Video Page Address CRT Video Page Address CPU Page Address "17" CPU Page Address "18" Select 64K or 256K Ram | des<br>: "17"<br>: "18"                                                                             |

```

03DF

CRT Processor Page Register - Video Mem Relative

Bit 0

A14

CRT Page 0

Bit 1

A15

CRT Page 1

Bit 2

A16

CRT Page 2

Bit 3

A14

Processor Page 0

Bit 4

A15

Processor Page 1

Bit 5

Al6

Processor Page 2

Video Address Mode 0

Bit 6

Bit 7

Video Address Mode 1

03F1

Drive Select Switch

"1" DSO = DSO

"0" DSO \Rightarrow DS1

03F2, 3F0, 3F3

DOR Register (Write Only)

Bit0 - 1: Drive Select

Bitl Bit0

0

Drive Select A*

0

n

1

Drive Select B*

Bit2: 0 = FDC Reset

Bit3: 1 = Enable DMA Req/Interrupt

Bit4: 1 = Drive A Motor On

Bit5: 1 = Drive B Motor On

Bit6: 1 = FDC Terminal Count

Bit7: Not Used

03F4, 3F6

FDC - Status (Read Only) - See FDC Specification

FDC - Data (R/W) - See FDC Specification

03F5, 3F7

03F8 - 03FF

Not Used

For Ports 3F0 - 3F7, the following general conditions apply:

Al = Don't Care

For DOR, A2 = 0

For FDC, A2 = 1

```

| Main Logic T1000 SX                                                                                                                              | Subassembly                                                                                                                                                                                                                     | 8859003A                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| Main Logic T1000 SX                                                                                                                              | PCB Rev. A                                                                                                                                                                                                                      | 8709699A                                                       |

| C1-16,18,19,21-23,<br>25,26,28-32,29A,<br>30A,34,35,37,37A,<br>39-45,47,48,50-<br>57,124,126,128,<br>134,143,144,146,<br>147,149,150,178,<br>180 | Capacitor 0.1 MFD 50V Axial                                                                                                                                                                                                     | 8374104                                                        |

| C100,119,120,145,<br>148,151,157,<br>181                                                                                                         | Capacitor 22 MFD 16V Elec Axial                                                                                                                                                                                                 | 8316221                                                        |

| C101,117,125,137-<br>C102-109<br>C110<br>C111-116,152-154,<br>159-161,168                                                                        | Capacitor 1000 PFD C. Disk<br>Capacitor 68 PFD 50V C. Disk<br>Capacitor .01 MFD 50V. C. Disc El.<br>Capacitor 20 PFD 50V +80-20% Disk                                                                                           | 8301474<br>8300684<br>8303104<br>8300204                       |

| C118<br>C121,129,135,175,                                                                                                                        | Capacitor .022 MFD 63V 10% Poly<br>Capacitor 10 MFD 16V Elec Axial                                                                                                                                                              | 8393225<br>8316101                                             |

| C122,130<br>C123<br>C127<br>C131,132,136,176<br>C133<br>C155,156,162-167                                                                         | Capacitor 100 MFD 16V Elec Axial<br>Capacitor 330 PFD 50V C. Disk<br>Capacitor 100 PF 50V C. Disk<br>Capacitor .47 MFD 50V Mono. Rad.<br>Capacitor 180 PF 50V C. Disk<br>Capacitor 2200 PFD C. Disk<br>U51 Between Pins 15 & 26 | 8317101<br>8301332<br>8301104<br>8384475<br>8301184<br>8302224 |

| C157A<br>C169-174,177<br>C176                                                                                                                    | Capacitor .001 MFD C. Disk<br>Capacitor 470 PFD 50V C. Disk<br>Capacitor .47 MFD 50V Mono. Rad.                                                                                                                                 | 8382104<br>8301474<br>8384475                                  |

| CR1<br>CR2                                                                                                                                       | Diode 1N5235 6.8V<br>Diode 1N4148                                                                                                                                                                                               | 8150235<br>8150148                                             |

| E1-6                                                                                                                                             | Staking Pins                                                                                                                                                                                                                    | 8529014                                                        |

| FB1-4                                                                                                                                            | Ferrite Bead                                                                                                                                                                                                                    | 8419013                                                        |

| J1<br>J2,3<br>J4<br>J5<br>J6                                                                                                                     | Connector, 2-Pin Stra. Header Connector, 6-Pin Rt. Angle Connector, 8-Pin Rt. Angle Connector, Dual 17-Pin Str. Header Connector, 9-Pin St. Friction Lock                                                                       | 8519193<br>8519289<br>8519288<br>8519120<br>8519191            |

| Ј8                               | Connector, 9-Pin Rt. Angle Male                     | 8519235            |

|----------------------------------|-----------------------------------------------------|--------------------|

| J9                               | "D" Sub<br>Connector, 9-Pin Rt. Angle Female        | 8519245            |

| J10                              | Female "D" Sub<br>Connector, Dual RCA Pho. Jack Rt. | 8519213            |

| J11-15                           | Angle<br>Connector, Dual 31-Pin Str. Card Edge      | 8519236            |

| Ql                               | Transistor 2N3906                                   | 8100906            |

| Q2<br>Q3                         | Transistor VN0104N3<br>Transistor 2N3904            | 8190104<br>8110904 |

| R1-4,22-24,27-29,<br>34,35,38,53 | Resistor 10K Ohm 1/4 Watt 5%                        | 8207310            |