CUSTOM MANUFACTURED IN U.S.A. BY RADIO SHACK, A DIVISION OF TANDY CORPORATION

#### **TANDY® 1000 COMPUTER**

Copyright 1985 Tandy Corporation All Rights Reserved

Reproduction or use, without express written permission from Tandy Corporation, or any portion of this manual is prohibited. While reasonable efforts have been taken in the preparation of this manual to assure its accuracy, Tandy Corporation assumes no liability resulting from any errors or omissions in this manual, or from the use of the information contained herein.

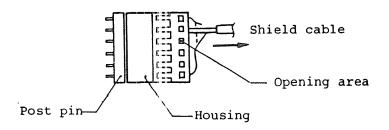

## CONTENTS

| 1/ |                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 2/ | Specifications                                                                                                                                                                                                                                                                                                                                                                                                           | 3                                                  |

| 3/ | Disassembly-Assembly                                                                                                                                                                                                                                                                                                                                                                                                     | 5                                                  |

| 4/ | Cabling Diagram and Pinout Designations                                                                                                                                                                                                                                                                                                                                                                                  | 9                                                  |

| 5/ | Bus Interface Specifications                                                                                                                                                                                                                                                                                                                                                                                             | 15                                                 |

| 6/ | Theory of Operation                                                                                                                                                                                                                                                                                                                                                                                                      | 19                                                 |

|    | Main Logic Board<br>IFL Equations<br>Introduction to the Video System Logic                                                                                                                                                                                                                                                                                                                                              | 23                                                 |

|    | Video System Modes<br>Display Modes<br>Operating Modes<br>Graphics Mode                                                                                                                                                                                                                                                                                                                                                  | 48<br>49                                           |

|    | System Logic Registers         Video Array Register         Palette Mask Register         Border Color Register         Border Color Register         Mode Control Register         Palette Register         Video Memory Map Register         Mode Register         Color Select Register         Status Register         CRT/Processor Page Register         General Memory Information         Mode Selection Summary | 53<br>53<br>54<br>55<br>56<br>58<br>58<br>59<br>60 |

|    | Mode Selection Summary<br>I/O Map<br>System Configuration Port<br>ROM<br>RAM<br>Memory Map                                                                                                                                                                                                                                                                                                                               | 61<br>62<br>62<br>62<br>47                         |

|    | Detailed Memory Map<br>Troubleshooting the Main Logic Board                                                                                                                                                                                                                                                                                                                                                              | 63<br>75                                           |

# **Contents continued**

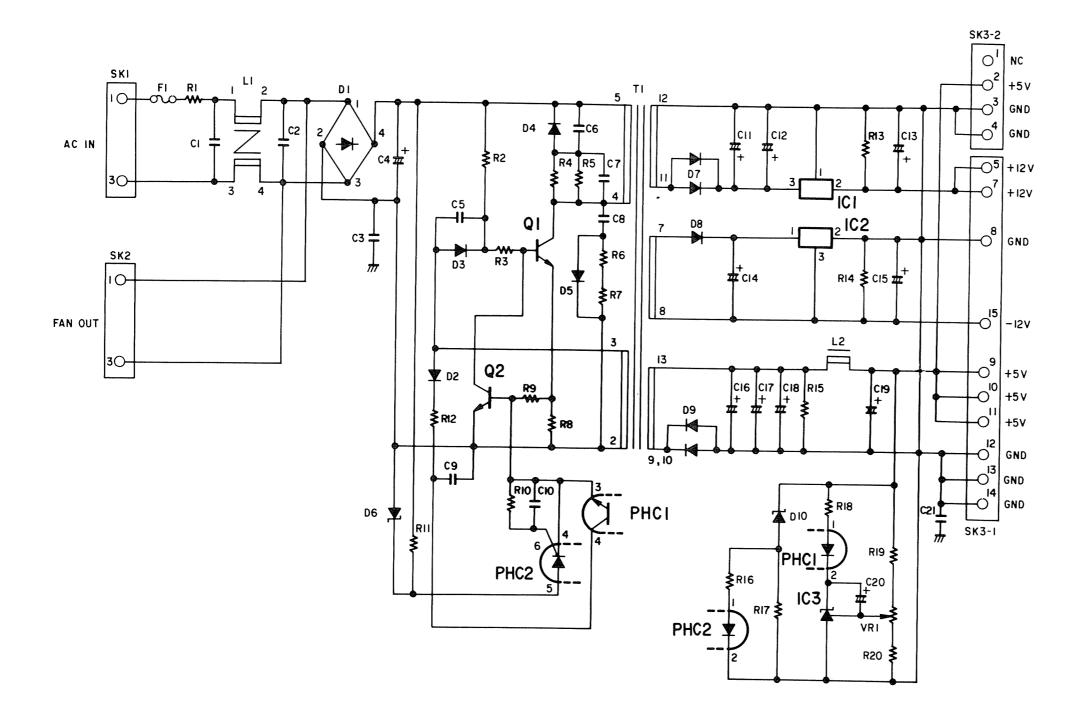

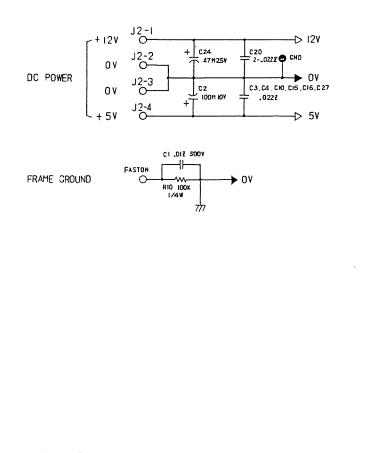

| 7/ | 54 Watt Power Supply                                                                                                                                                                        | 77                   |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|    | Theory of Operation<br>AC Input Circuit<br>Switching Driver and Control Circuit<br>5V Output Voltage Detecting Circuit<br>Over Voltage Protection<br>Power Supply Operating Characteristics | 77<br>77<br>78<br>78 |

|    | Troubleshooting the 54 Watt Power Supply                                                                                                                                                    | 80                   |

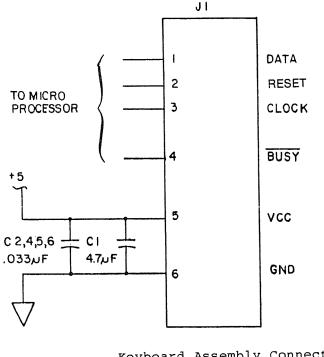

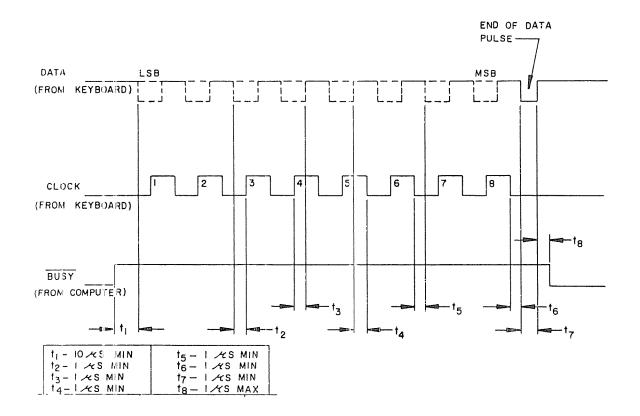

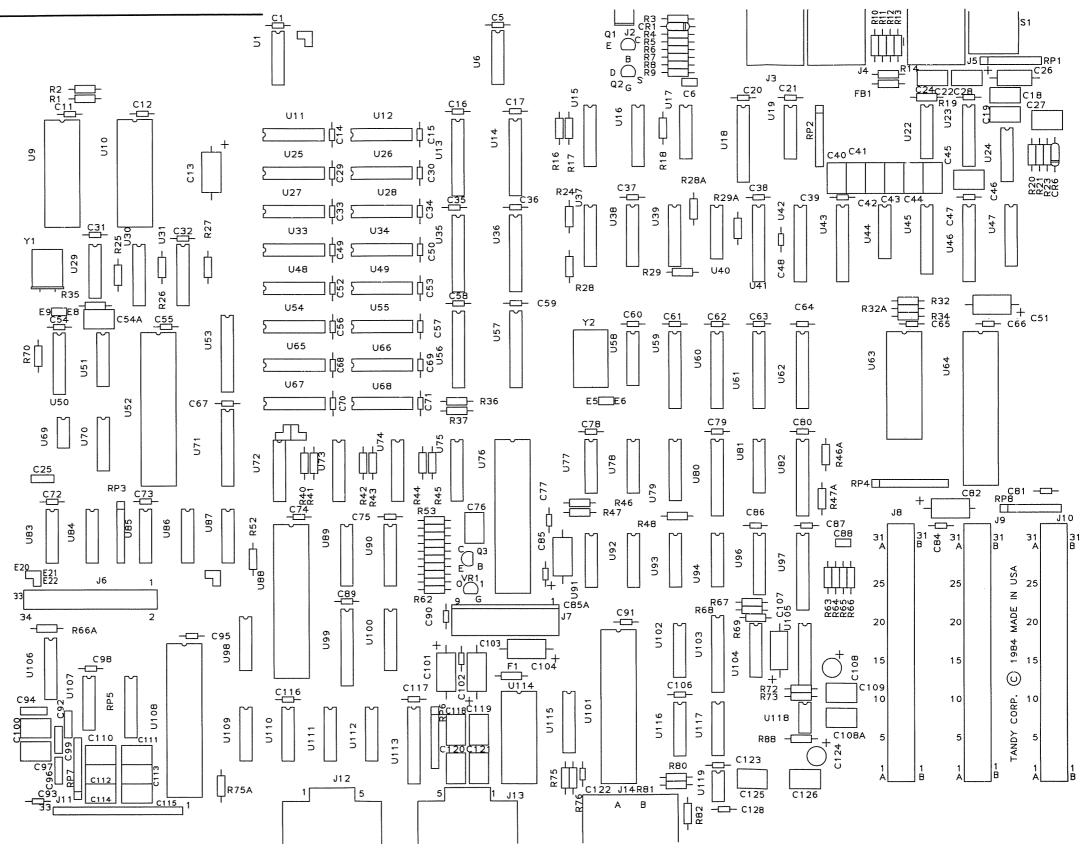

| 8/ | Keyboard Assembly                                                                                                                                                                           | 85                   |

|    | Keyboard Specifications<br>Key Code Chart<br>Keyboard Timing<br>Keyboard Layout                                                                                                             | 86<br>88             |

| 9/ | Parts List                                                                                                                                                                                  | 93                   |

|    | Main Logic Board                                                                                                                                                                            | 100                  |

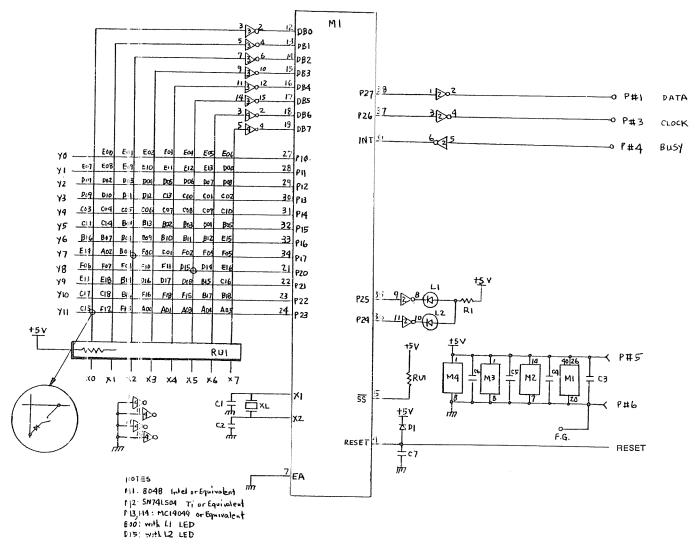

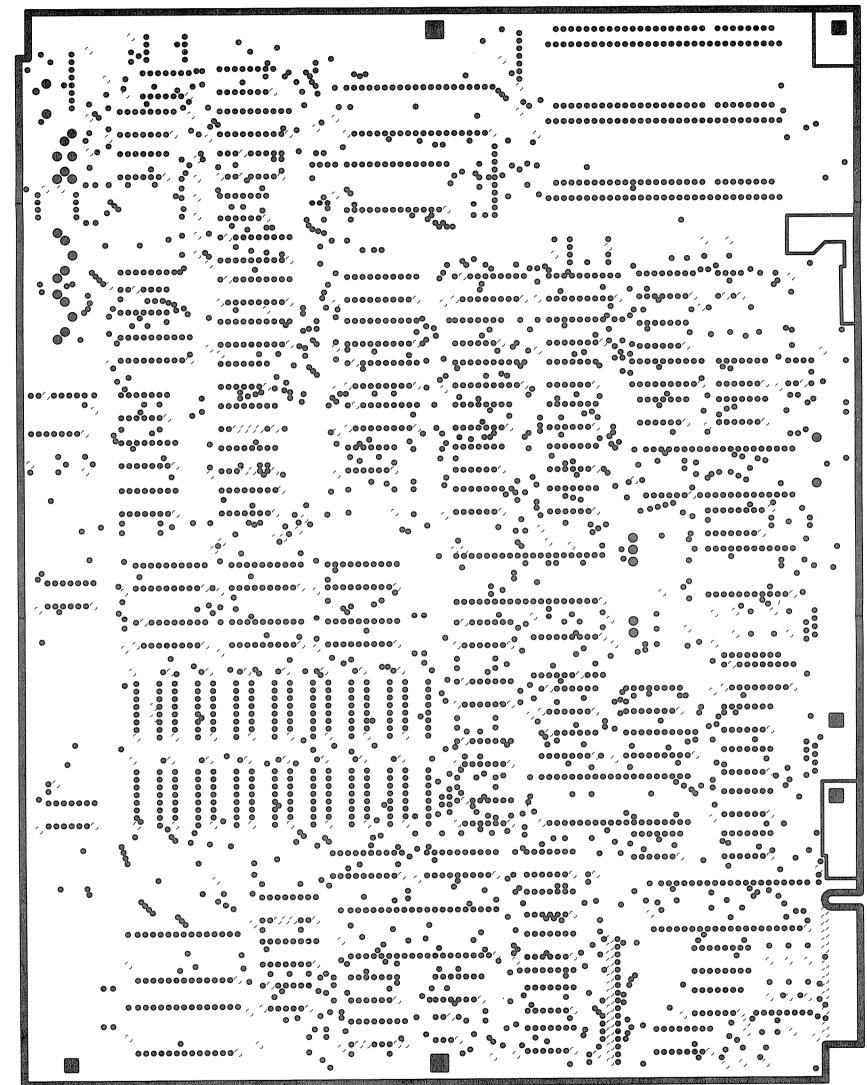

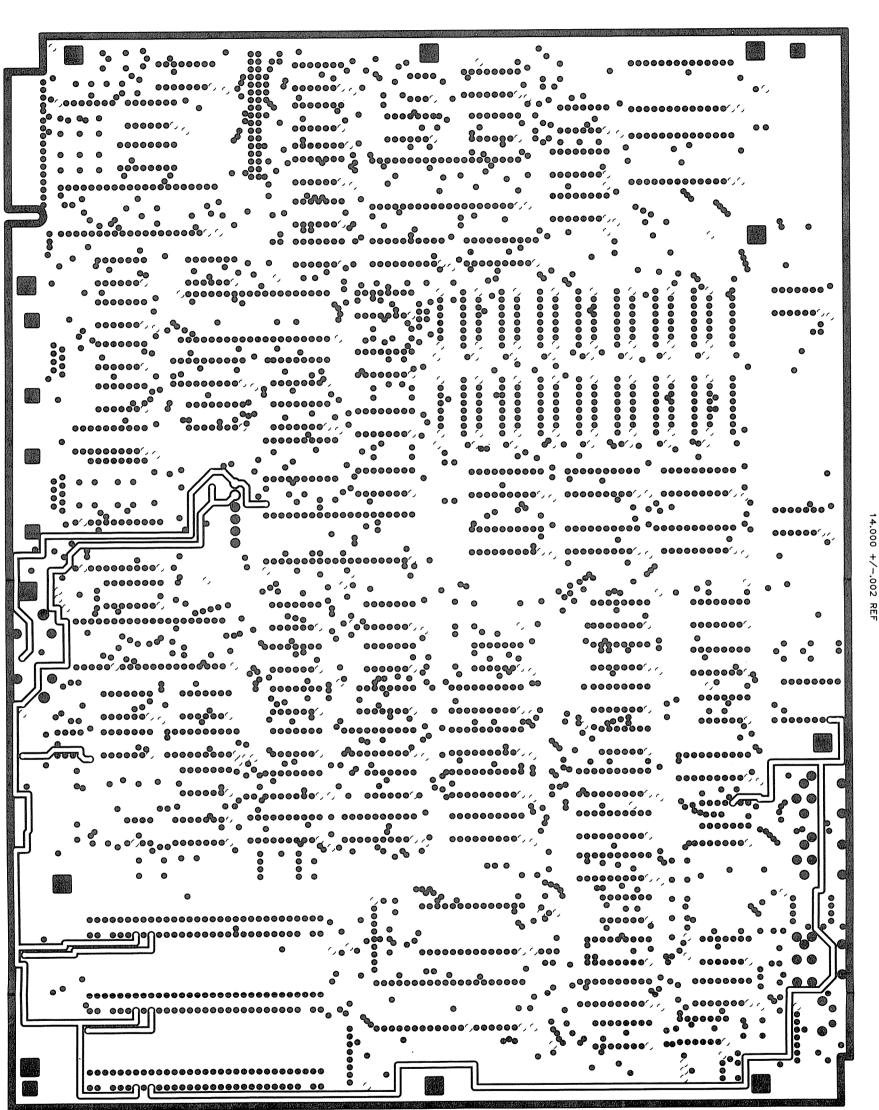

| 10 | / Component Layouts                                                                                                                                                                         | 103                  |

| 11 | / Schematics                                                                                                                                                                                | 115                  |

| 12 | / Connectors and Pin Designations                                                                                                                                                           | 141                  |

| Ap | pendices                                                                                                                                                                                    |                      |

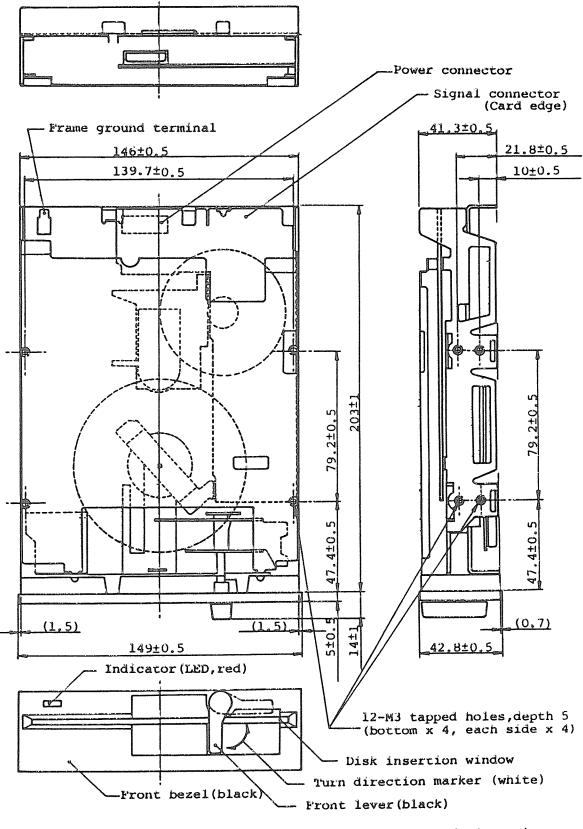

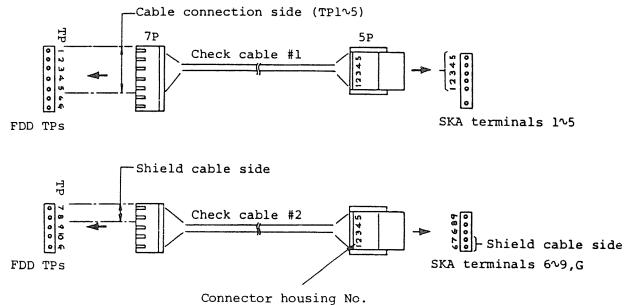

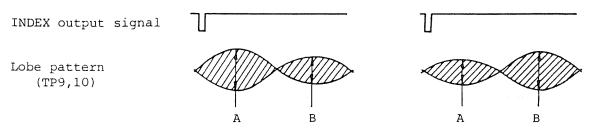

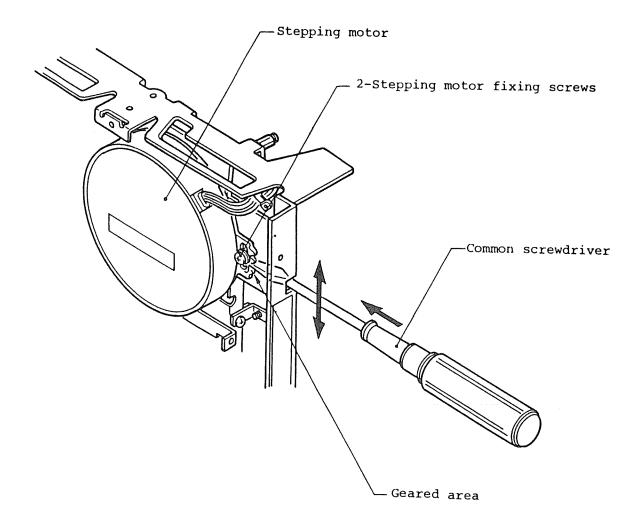

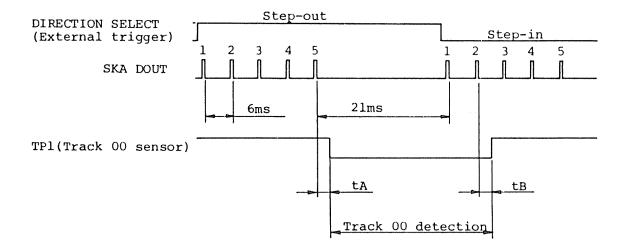

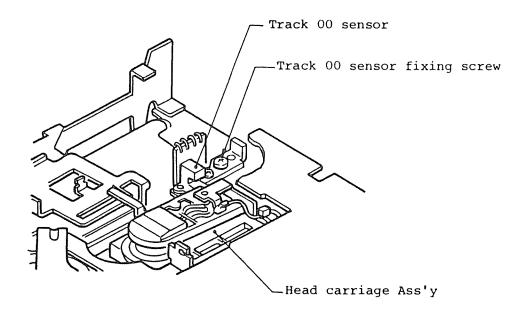

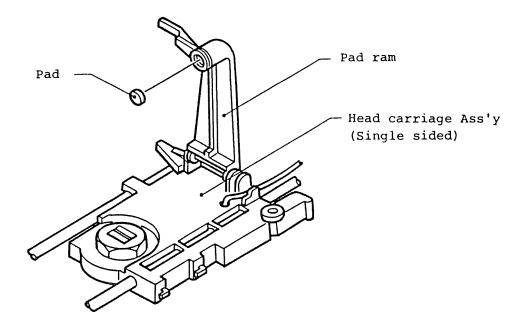

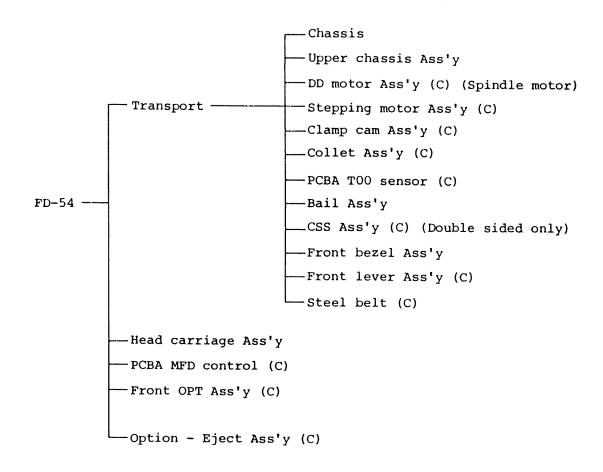

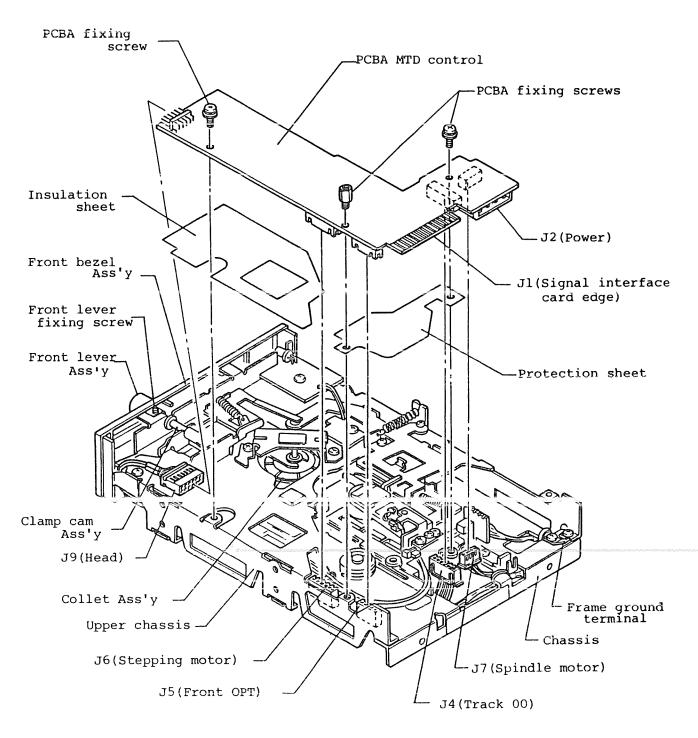

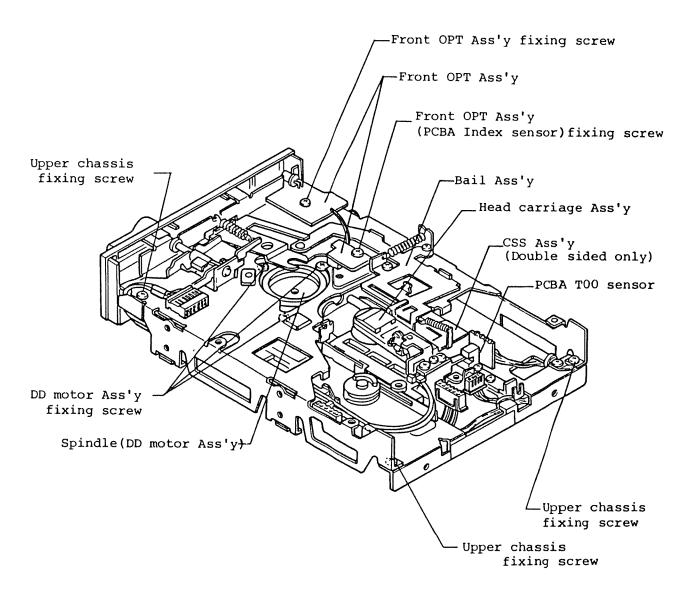

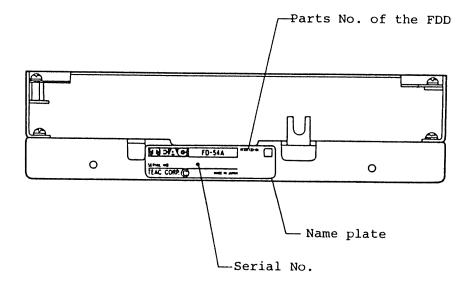

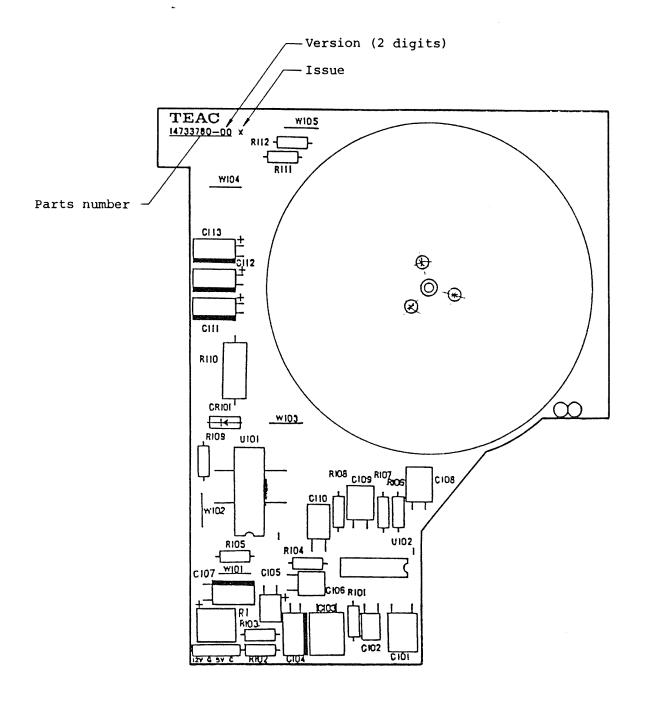

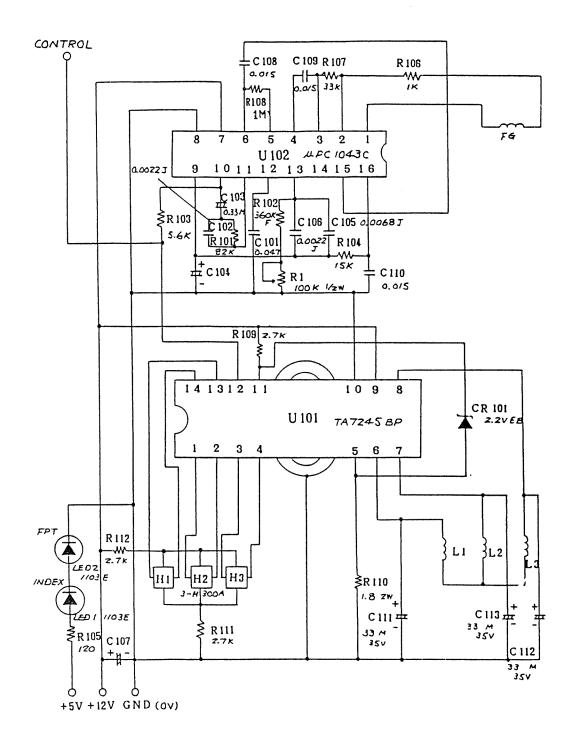

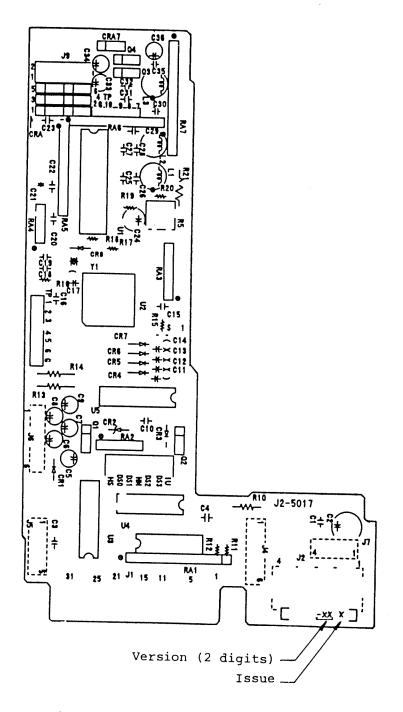

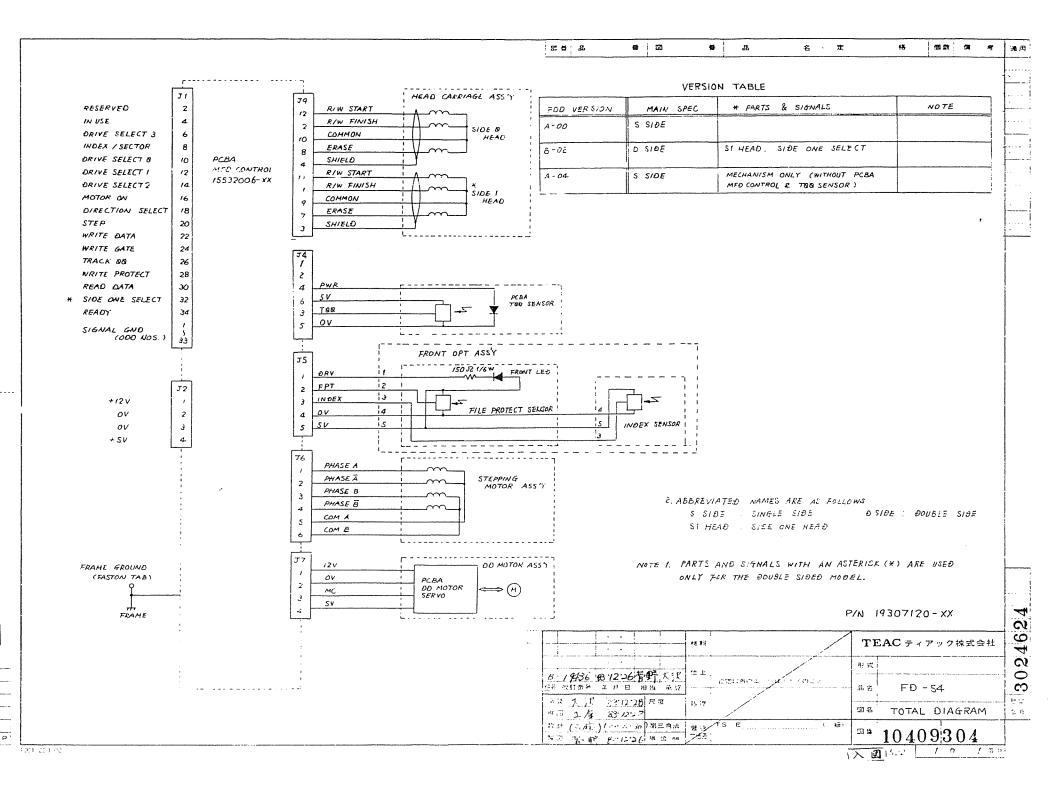

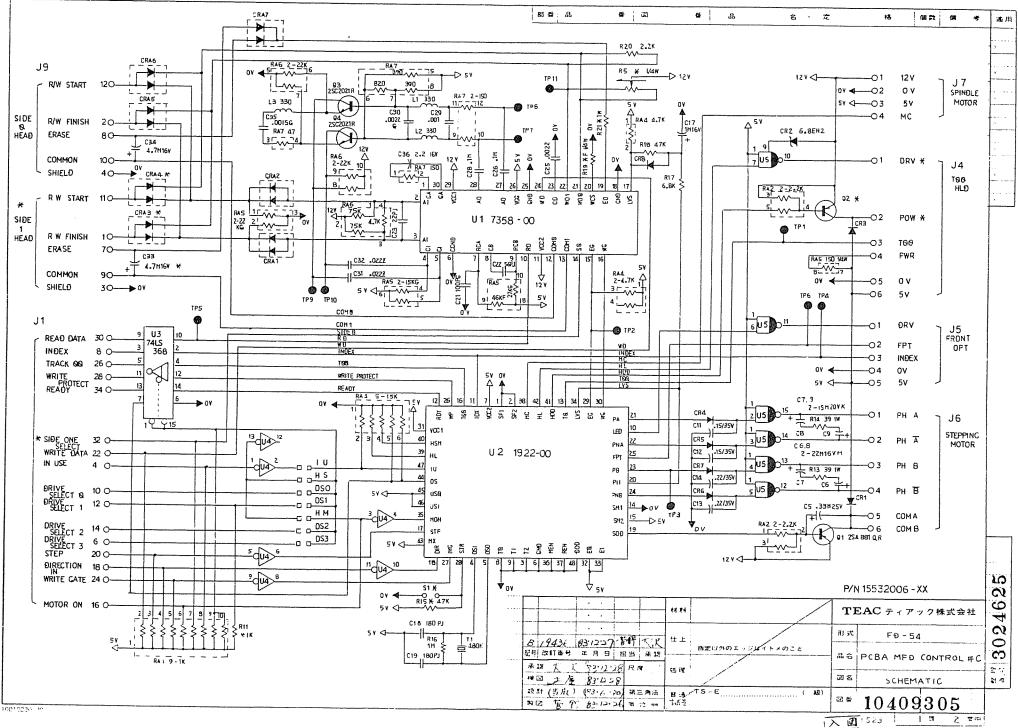

A/ Teac Disk Drive Manual

## 1 / INTRODUCTION TO THE TANDY 1000 COMPUTER

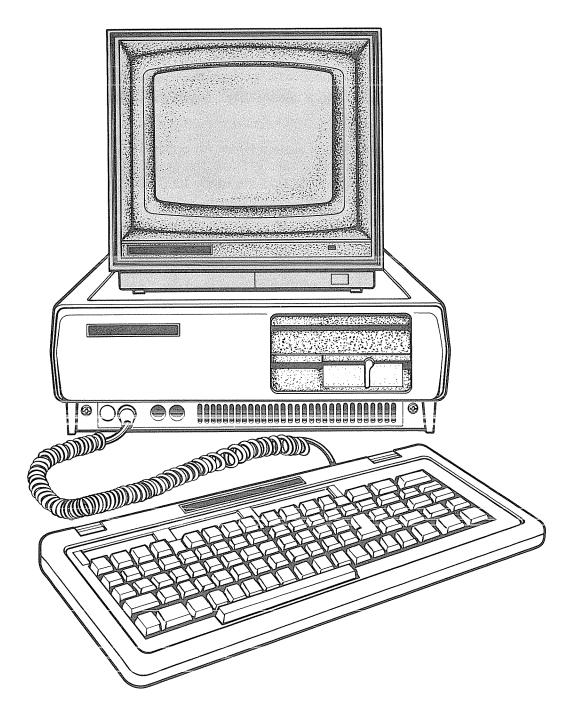

The Tandy 1000 Computer is modular in design to allow maximum flexibility in system configuration. The computer consists of a Main Unit, a detachable keyboard with coiled cable, and a monitor. The Main Unit is supplied with one internal floppy disk drive. (A second floppy disk drive is optional.) The standard types of monitors used with the Tandy 1000 are the monochrome composite and the color RGB monitor. Since these units are modular, they may be placed on top of the Main Unit or at any convenient location.

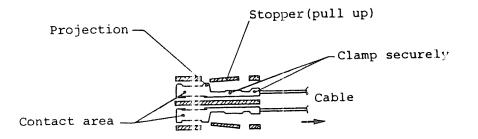

Internal storage is expanded by adding a second 51/4" floppy disk drive. Each disk drive has a capacity of 360K bytes formatted.

The Tandy 1000 has a standard 128K of system RAM. An optional DMA/RAM board allows the Tandy 1000 to be expanded in increments of 128K of RAM. This board will fit into one of the expansion slots. With two fully populated RAM boards installed, the Tandy 1000 will have 640K bytes of maximum RAM allowed by the system memory map.

Other features include a parallel printer port, two built-in joystick interfaces, a speaker for audio feedback, and a light pen interface.

The Main Unit is the heart of the Tandy 1000. It houses the Main Logic Assembly, system power supply, and floppy disk drives.

The Main Logic Assembly is a large board mounted to the bottom of the Main Unit and interconnected to the keyboard, power supply, and disk drives by a series of cables. The illustration in Figure 1 shows the major components of a Tandy 1000 system.

The Power Supply is a 54W switching regulator type, designed to provide adequate power capacity for a fully configured system using all the option slots.

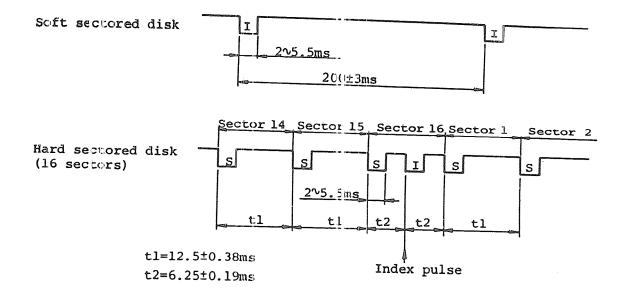

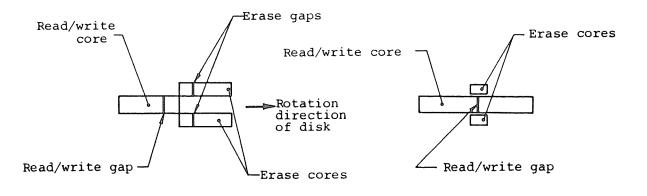

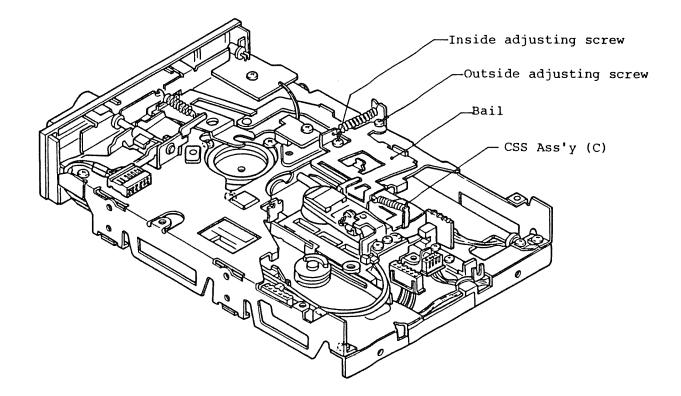

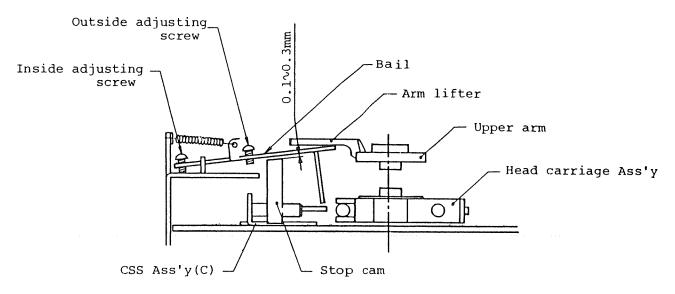

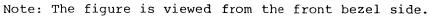

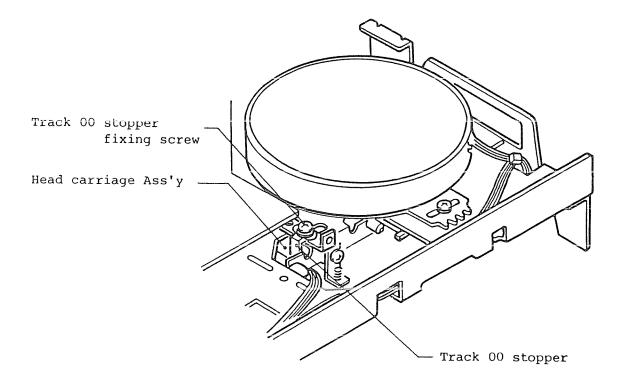

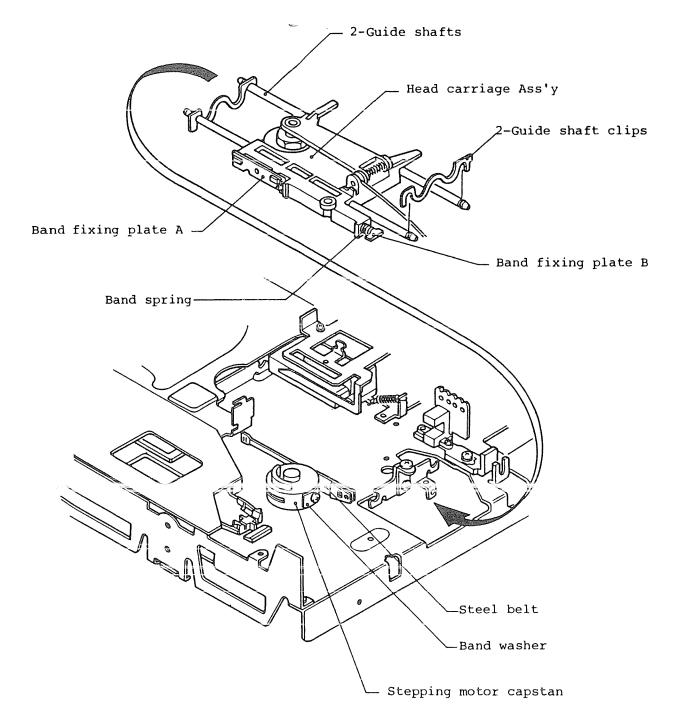

The Floppy Disk Drive uses 51/4" double-sided, double-density diskettes to read, write, or store data. These are soft sector diskettes. The Disk Drive assembly is installed in the standard unit. The floppy disk stores approximately 360K bytes (formatted) of data. All system programs, with the exception of the system startup sequence, are stored on disk.

Either a monochrome or a color display may be used with the Tandy 1000. The monochrome monitor is a high-resolution green phosphor display which provides excellent visual quality. It features a 12'' screen with an anti-glare surface. Each display is capable of 25 lines of 80 characters. The character matrix is 8 wide x 9 high.

Tandy 1000 System Figure 1

## 2 / SPECIFICATIONS

Processor: Intel 8088

#### **Dimensions:**

$6 \times 17 \times 13$  % inches (HWD)

#### Weight:

17 lbs. 4 oz. with 1 Disk Drive

#### **Power Requirements:**

120 VAC, 60 Hz, 1 Amp maximum

#### With 2 Floppy Disk Drives, 2 Memory Cards, and RS-232:

AC Current: 0.7 - 0.8 Amps with Floppy doing R/W tests. Leakage Current: 0.5 mA Disk Drive: Idle +5 VDC 0.23 Amps +12 VDC 0.106 Amps R/W 0.286 Amps 0.295 Amps R/W 0.2 Minimum 0.550 Max. Main Logic Board: +5 VDC 4.07 Amps +12 VDC 0.056 Amps Main Logic Board Option Cards: -12 VDC 0.032 Amps

#### **Environment:**

Air Temperature

System ON: 60 to 90 degrees F (15.6 to 32.2 degrees C) System OFF: 50 to 110 degrees F (10 to 43 degrees C)

Humidity

System ON-OFF: 8% to 80%

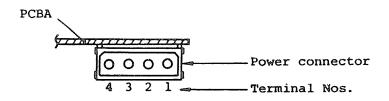

#### **Disk Drive Specifications**

#### Power:

| Supply                                         |                                         |                   |

|------------------------------------------------|-----------------------------------------|-------------------|

| Voltage                                        | +5 VDC Input                            | +12 VDC Input     |

| Ripple                                         |                                         |                   |

| 0 to 50 kHz                                    | 100 mV                                  | 100 mV            |

| Tolerance<br>Including Ripple                  | +/-5%                                   | +/-5%             |

| Standby Current                                |                                         |                   |

| Nominal                                        | 600 mA                                  | 400 mA            |

| Worst Case                                     | 700 mA                                  | 500 mA            |

| Operating Current<br>Nominal<br>Worst Case     | 600 mA<br>700 mA                        | 900 mA<br>2400 mA |

| Environment:                                   |                                         |                   |

| Temperature<br>Operating<br>Nonoperating       | 50 to 122 degrees<br>- 40 to 140 degree |                   |

| Relative Humidity<br>Operating<br>Nonoperating | Operating 20% to 80% (noncondensing)    |                   |

)

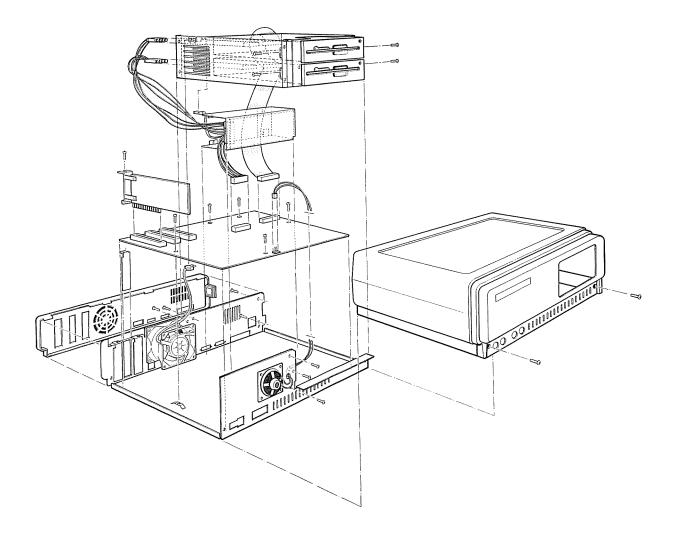

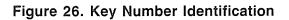

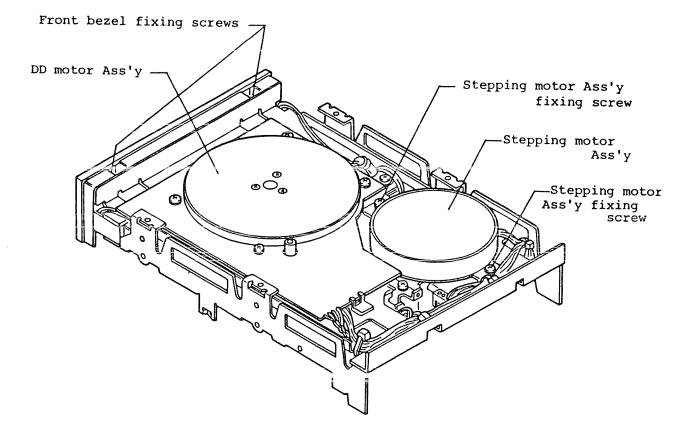

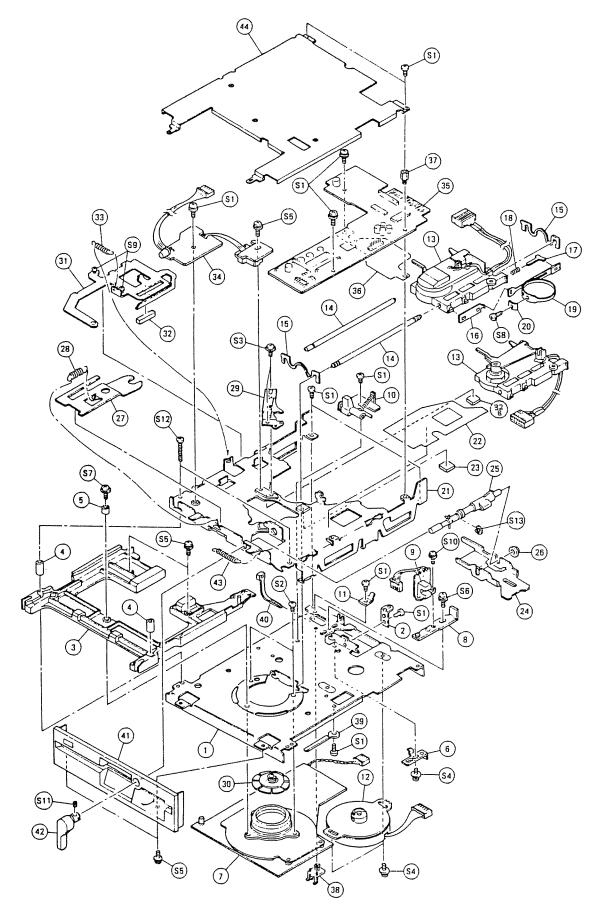

## 3 / Disassembly-Assembly

Since the Tandy 1000 is modular in its construction, disassembly/assembly procedures are simplified. The modules which make up the Tandy 1000 are the Main Unit, the keyboard, and the display monitor. These three units may be supplemented by various I/O devices such as printers, modems, memory devices or additional monitors. Disassembly of each module will be described in the following praragraphs. Exercise caution when handling the modules to prevent damage to internal components or exterior surfaces. See Figure 2.

#### Disassembly of the Main Unit

- 1. To remove the case, remove the 2 screws from the lower front of the case, slide the case forward until it clears the rear panel and remove.

- 2. To remove the rear panel, remove the 3 screws in the back of the unit and lift up slightly.

- 3. To remove the disk drive assembly, remove the 2 screws nearest the cooling fan on the rear of the chassis, the 1 screw on the right side of the drive structure which attaches it to the base of the chassis and the 3 screws on the front of the chassis. Disconnect the DC power and signal cables from the rear of the drive(s). Lift the drive upward to remove.

- 4. To remove the power supply, disconnect the DC power cable from the main board. Disconnect the fan cable on the left side of the drive structure. Remove the 4 screws on the rear of the chassis.

- 5. To remove an option board, locate the screw on the top of the option board panel. Remove the screw and pull up to separate it from the main logic circuit board.

- 6. To remove the main logic circuit board, disconnect the speaker cable and remove the 11 screws holding the board to the chassis.

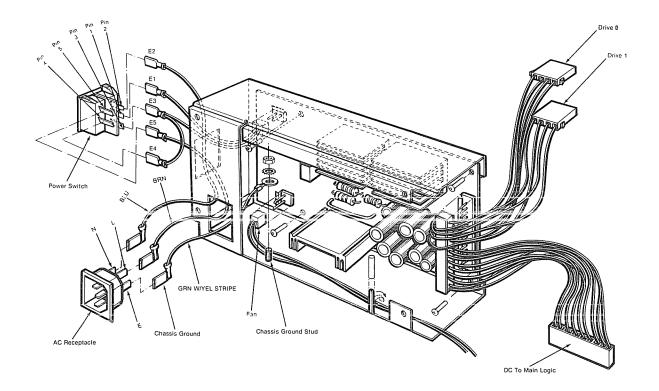

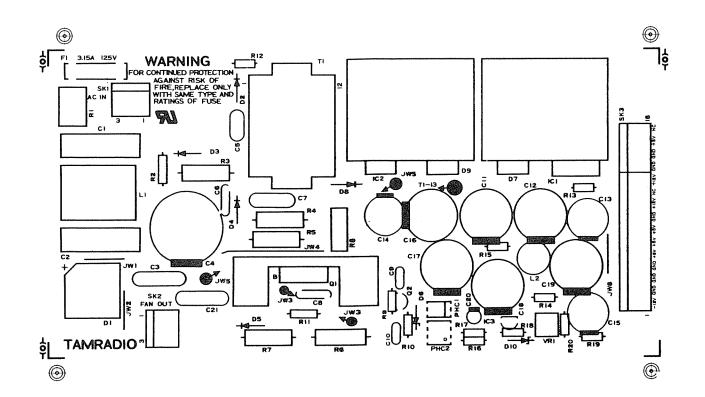

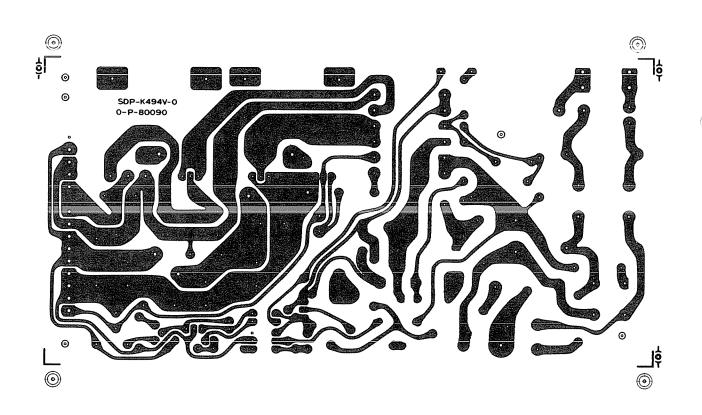

## **Power Supply**

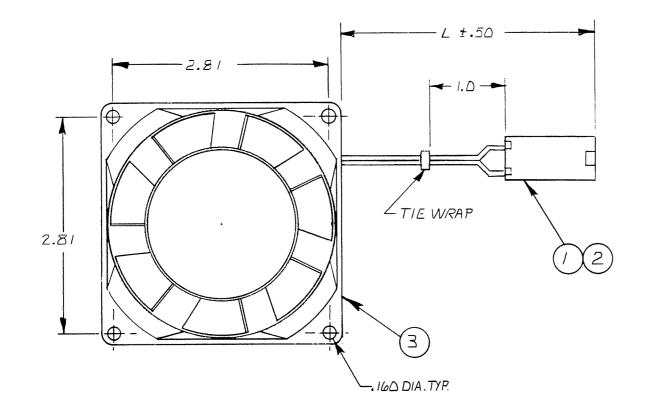

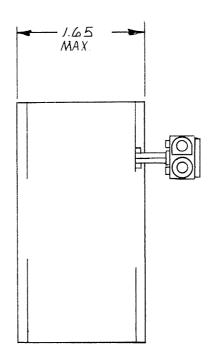

The 54W main power supply is located at the right side of the Main Unit and is accessible when you remove the cover and rear panel from the Main Unit as noted above. See Figure 3.

- 1. Unplug the AC power cable from the power supply and lay it aside.

- 2. Disconnect the power cable and floppy drive cable from the circuit board.

- 3. Remove the 4 mounting screws on the power supply circuit board.

- 4. Disconnect the AC fan cable on the power supply circuit board and remove the power supply through the open end of the enclosure.

Assemble the power supply in the reverse order of disassembly. Ensure that all cables and wires are connected correctly.

#### Keyboard

The keyboard assembly is connected by a coiled cable attached to the left side of the front plate of the Main Unit. Disassemble the keyboard as noted below. See Figure 28 in the Keyboard Section.

#### Disassembly

- 1. After removing the connector from the Main Unit, turn the keyboard assembly upside down on a soft surface to prevent scratching the surface of keys. Be sure the cable is extended away from you.

- 2. Remove the 3 screws nearest the front of the keyboard. Keep these separate so that you can replace them in their correct locations.

- 3. Remove the remaining 6 screws from the sides and back of the keyboard assembly.

- 4. Hold the top and bottom of the keyboard assembly together and turn the assembly right side up.

- 5. Lift the top cover off the assembly, exposing the keyboard printed circuit board.

- 6. The keyboard cable is restrained by a labyrinth-shapped form. Carefully lift the cable from each bend, and when the cable is free of the restraint, disconnect the cable connector from the right rear of the keyboard assembly and remove the keyboard circuit board.

#### Assembly

Assemble the keyboard in the reverse order of disassembly. Be sure that the keyboard supports are properly positioned on the support springs before installing the top cover. Also be sure that the shorter mounting screws are used at the front positions of the keyboard assembly (to prevent damage to the keyboard plastic).

#### **Display Unit**

For more information on the display units, refer to the manual(s) available for the model you have.

Figure 2 Tandy 1000 Exploded View

1

Figure 3 54 Watt Power Supply Exploded View

8

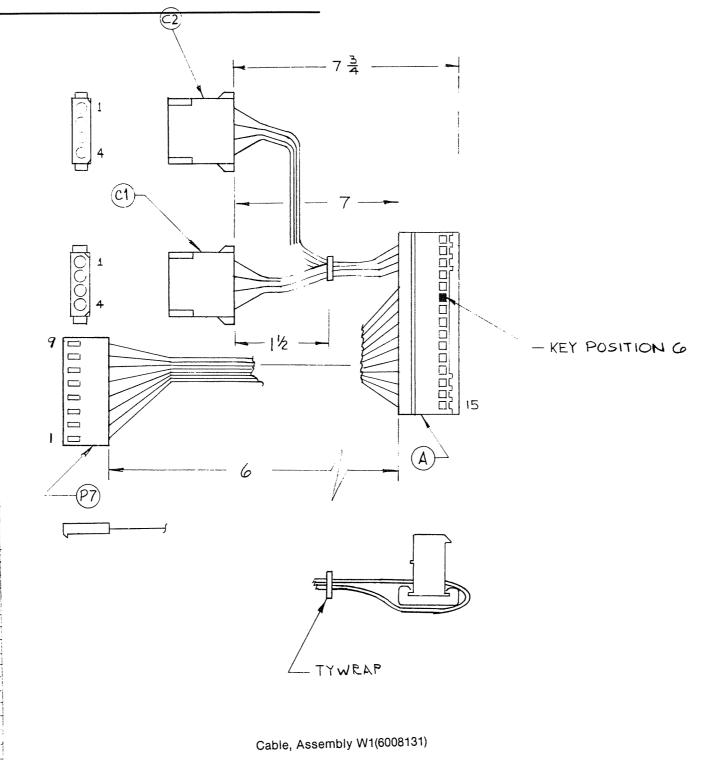

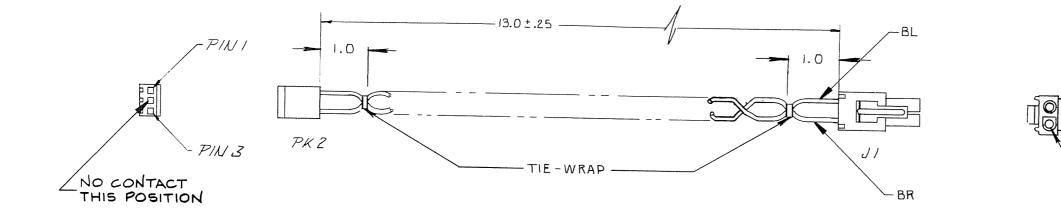

## **4 / CABLING DIAGRAMS AND PINOUT CONNECTIONS**

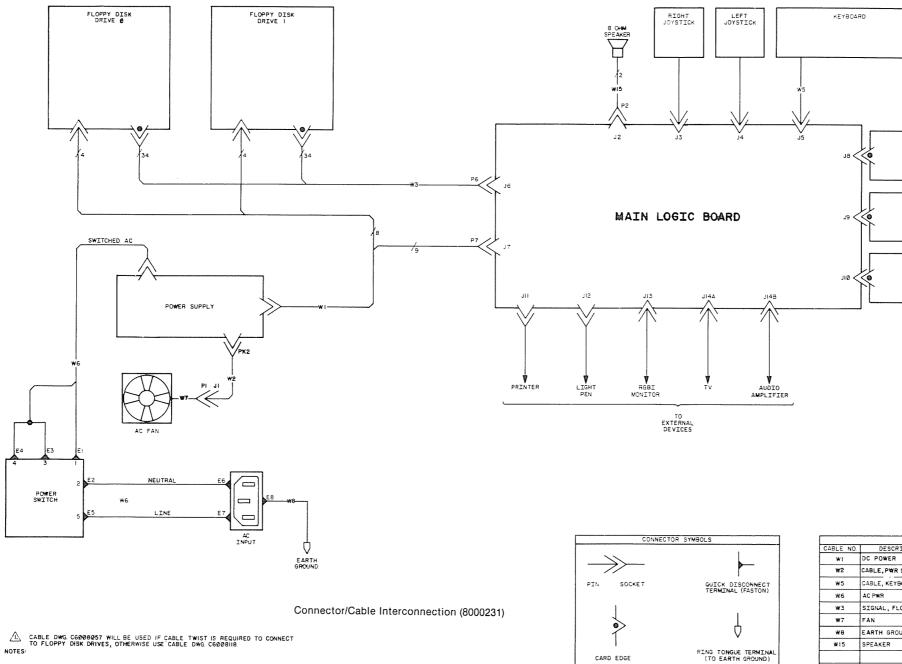

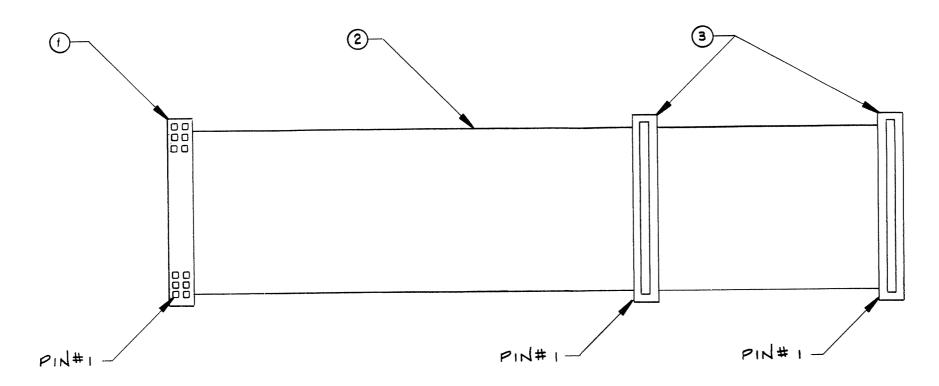

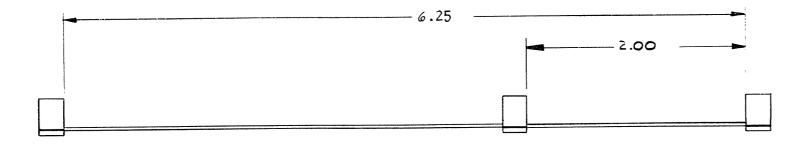

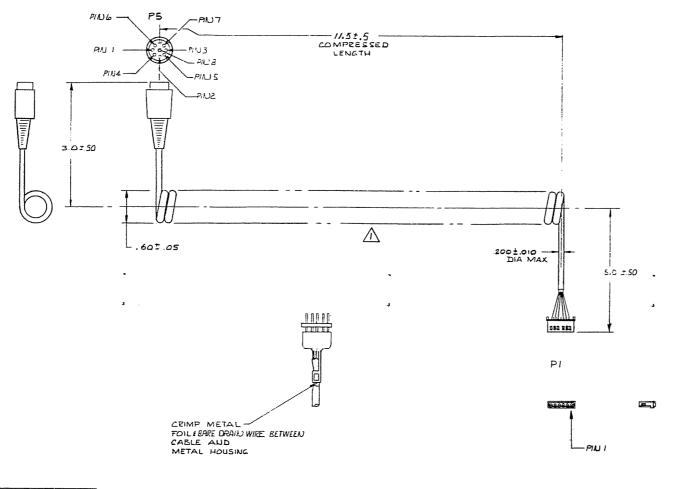

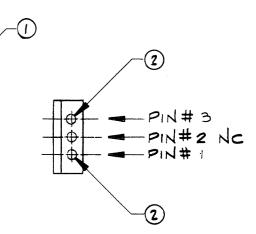

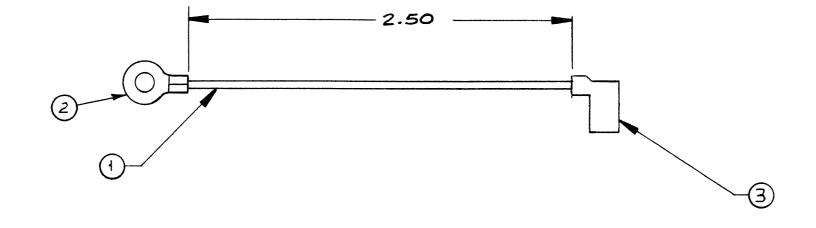

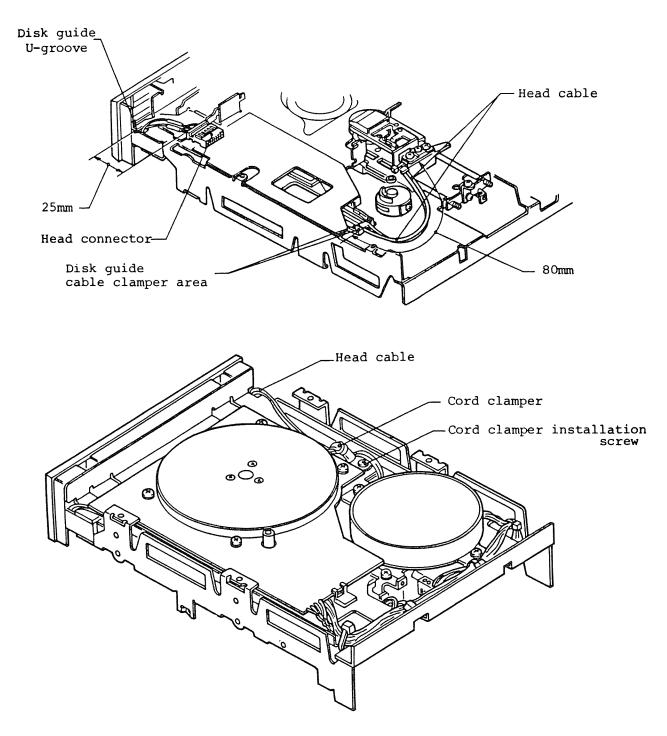

This section of the manual provides connector diagrams and pin descriptions of the connectors used in the Tandy 1000. Figure 4 shows an interconnecting wiring diagram and identifies the connectors by symbol number and/or cable number. The drawings of each connector with their pin designations are in Section 12.

10

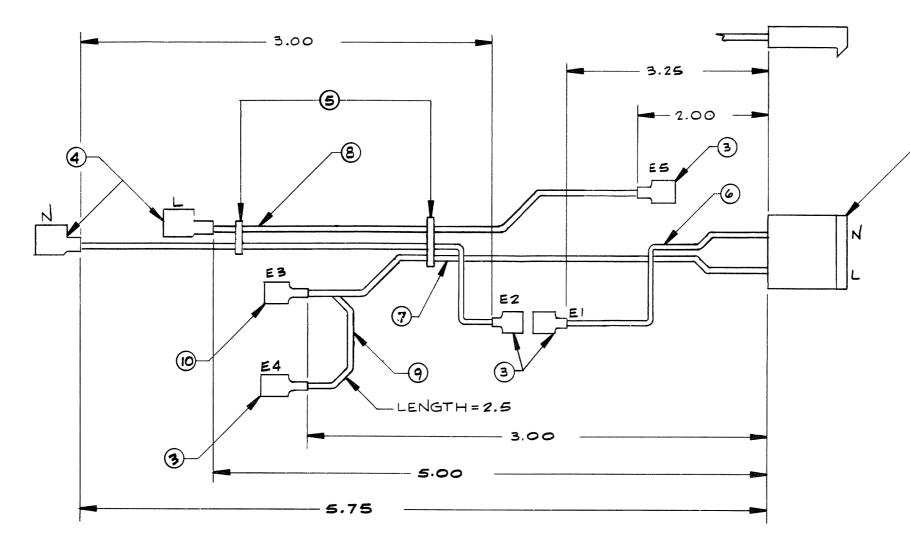

# Figure 4 Interconnecting Wiring Diagram

| REFER         | ENCE             |                 |

|---------------|------------------|-----------------|

| RIPTION       | DRAWING NO.      | CABLE ASS'Y P/N |

| 1             | C6Ø08131         | 870-9558        |

| R SPLY TO FAN | C6996141         | 870-9575        |

| YBOARD        | A6008129         | 870-9567        |

|               | C6ØØ8121         | 870-9553        |

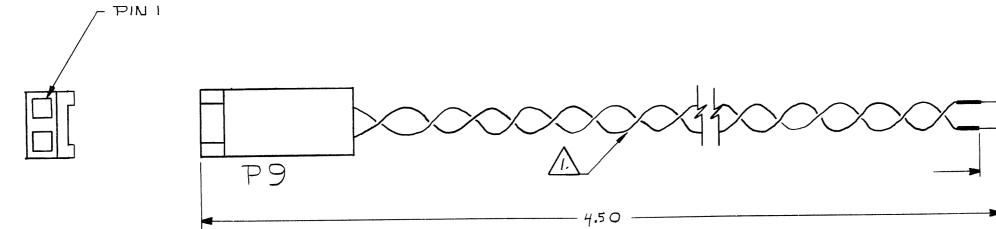

| LOPPY DISK    | C6008057 🛆       | 870-9447        |

|               | C26 <b>06069</b> |                 |

| OUND          | A6008125         | 870-9552        |

|               | C6ØØ8Ø7Ø         | 872-9470        |

|               |                  |                 |

|               |                  |                 |

OPTION CARD 3

OPTION CARD 2

OPTION CARD |

Service Manual

# **Connector Pin Assignments**

| J2 — | Speaker Interface<br>(2-Pin Vertical Header)                                                                                                |                                                                                                                                                                                                   |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 1 — Sound                                                                                                                                   | 2 — Ground                                                                                                                                                                                        |

| J3 — | Right Joystick<br>(6-Pin Rt. Angle Circular Din)                                                                                            |                                                                                                                                                                                                   |

|      | 1 — Y Axis<br>3 — Ground<br>5 — +5 VDC                                                                                                      | 2 — X Axis<br>4 — Switch 1<br>6 — Switch 2                                                                                                                                                        |

| J4 — | Left Joystick<br>(6-Pin Rt. Angle Circular Din)                                                                                             |                                                                                                                                                                                                   |

|      | 1 — Y Axis<br>3 — Ground<br>5 — +5 VDC                                                                                                      | 2 — X Axis<br>4 — Switch 1<br>6 — Switch 2                                                                                                                                                        |

| J5 — | Keyboard Interface<br>(8-Pin Rt. Angle Circular Din)                                                                                        |                                                                                                                                                                                                   |

|      | 1 — KBDDATA<br>3 — Ground<br>5 — +5 VDC<br>7 — MULTIDATA                                                                                    | 2 — KBDBUSY*<br>4 — KBDCLK<br>6 — KBDRST<br>8 — MULTICLK                                                                                                                                          |

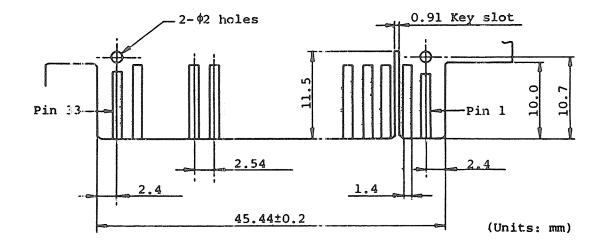

| J6 — | Floppy Disk Interface<br>(Dual 17-Pin Vertical Header)                                                                                      |                                                                                                                                                                                                   |

|      | 1—Ground3—Ground5—Ground7—Ground9—Ground11—Ground13—Ground15—Ground17—Ground21—Ground23—Ground25—Ground27—Ground29—Ground31—Ground33—Ground | 2 NC<br>4 NC<br>6 NC<br>8 INDEX*<br>10 DS0*<br>12 DS1<br>14 NC<br>16 MTRON*<br>18 DIR*<br>20 STEP*<br>22 WRDATA*<br>24 WEN*<br>26 TRK0*<br>28 WRPRT*<br>30 RDDATA*<br>32 SIDESELECT<br>34 DRVRDY* |

\*

| J7 — DC POWER<br>(9-PIN VERTICAL HEADER)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 — +5 VDC<br>3 — +5 VDC<br>5 — Ground<br>7 — Ground<br>9 — +12 VDC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2 — +5 VDC<br>4 — Ground<br>6 — Ground<br>8 — -12 VDC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

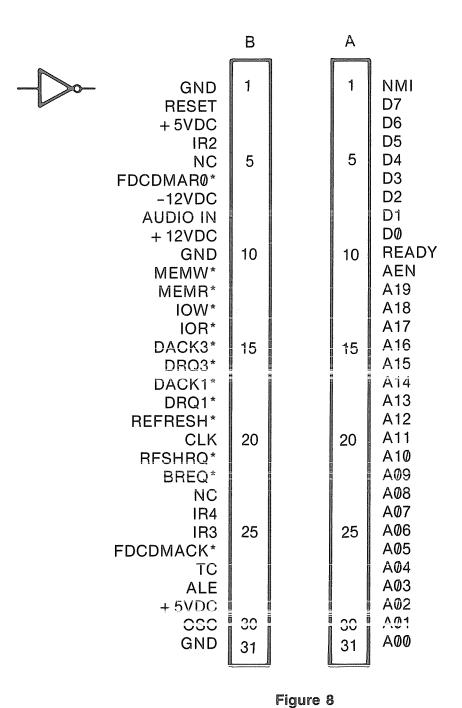

| J8,J9,J10 — Expansion Interface Conne<br>(Dual 31-Pin Card Edge)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| $\begin{array}{l} \text{A01} & - \text{ NMI} \\ \text{A02} & - \text{D7} \\ \text{A03} & - \text{D6} \\ \text{A04} & - \text{D5} \\ \text{A05} & - \text{D4} \\ \text{A06} & - \text{D3} \\ \text{A07} & - \text{D2} \\ \text{A08} & - \text{D1} \\ \text{A09} & - \text{D1} \\ \text{A10} & - \text{READY} \\ \text{A11} & - \text{AEN} \\ \text{A12} & - \text{A19} \\ \text{A13} & - \text{A18} \\ \text{A14} & - \text{A17} \\ \text{A15} & - \text{A16} \\ \text{A16} & - \text{A15} \\ \text{A17} & - \text{A14} \\ \text{A18} & - \text{A13} \\ \text{A19} & - \text{A12} \\ \text{A20} & - \text{A11} \\ \text{A21} & - \text{A10} \\ \text{A22} & - \text{A09} \\ \text{A23} & - \text{A08} \\ \text{A24} & - \text{A07} \\ \text{A25} & - \text{A06} \\ \text{A26} & - \text{A05} \\ \text{A27} & - \text{A04} \\ \text{A28} & - \text{A03} \\ \text{A29} & - \text{A02} \\ \text{A30} & - \text{A01} \\ \text{A31} & - \text{A00} \\ \end{array}$ | $\begin{array}{l} \text{B01} & \text{ Ground} \\ \text{B02} & \text{ RESET} \\ \text{B03} & +5 \text{ VDC} \\ \text{B04} & \text{IR2} \\ \text{B05} & (-5 \text{ VDC}) \\ \text{B06} & \text{FCDMARQ}^* \\ \text{B07} & 12 \text{ VDC} \\ \text{B08} & \text{AUDIOIN} \\ \text{B09} & +12 \text{ VDC} \\ \text{B10} & \text{ Ground} \\ \text{B11} & \text{ MEMW}^* \\ \text{B12} & \text{ MEMR}^* \\ \text{B13} & \text{ IOW}^* \\ \text{B14} & \text{ IOR}^* \\ \text{B15} & (\text{DACK3}^*) \\ \text{B16} & (\text{DRQ3}^*) \\ \text{B17} & (\text{DACK1}^*) \\ \text{B18} & (\text{DRQ1}^*) \\ \text{B19} & \text{ REFRESH}^* \\ \text{B20} & \text{CLK} \\ \text{B21} & \text{ RFSHRQ} \\ \text{B22} & \text{ BREQ}^* \\ \text{B23} & \text{ IR3} \\ \text{B24} & \text{ IR4} \\ \text{B25} & \text{ IR3} \\ \text{B26} & (\text{FDCDACK}^*) \\ \text{B27} & (\text{DMATC}) \\ \text{B28} & \text{ALE} \\ \text{B29} & +5 \text{ VDC} \\ \text{B30} & \text{ OSC} \\ \text{B31} & \text{ Ground} \\ \end{array}$ |

**Note:** Signals in parentheses on J8, J9, and J10 are shown for PC Compatible Reference only and are not used on the main logic board of the Tandy 1000.

J11— Parallel Interface (34-Pin Card Edge)

#### J12- Light Pen

(9-Pin Connector Male Rt. Angle D-Subminiature)

| 1 |   | +5 VDC | 2 | <br>Ground |

|---|---|--------|---|------------|

| 3 |   | LPIN   | 4 | <br>LPSW*  |

| 5 |   | NC     | 6 | <br>NC     |

| 7 |   | NC     | 8 | <br>NC     |

| 9 | _ | NC     |   |            |

#### J13- RGBI Video

(9-Pin Socket Rt. Angle D-Subminiature)

| 1 |   | Ground  | 2 |   | Ground    |

|---|---|---------|---|---|-----------|

| 3 |   | Red     | 4 |   | Green     |

| 5 |   | Blue    | 6 | _ | Intensity |

| 7 | _ | +12 VDC | 8 |   | HSYNC     |

| 9 |   | VSYNC   |   |   |           |

J14— Composite Output (Dual Rt. Angle RCA-Type Phone Jack)

A — Video

B — Audio

## **5 / BUS INTERFACE SPECIFICATIONS**

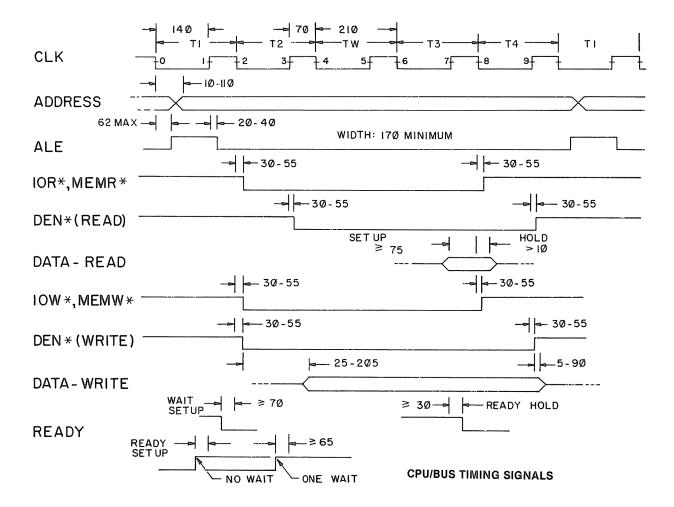

This specification is for the primary bus on the Tandy 1000 main logic board, which also is available to the option board connectors. The specification describes the signals in the following manner. See Figures 5 and 5.1.

- The following signal nomenclature is used in the schematic and literature. Signals designated with the suffix "\*" are logically "true low" (normal inactive state is high); if they are not so designated, the signal is logically "true high."

- Direction-input or output-is referenced to the CPU.

- Brief functional description of the signal.

- Description of the "drive" or "load" characteristics of the signal. This includes the specific source by IC type and reference designator, drive capability for "output" signals, and actual load for "input" signals. The drive/load is defined in "unit loads" and specified as "high/low." This specification is for the main logic board only. Some signals have an alternate source, an external bus master such as the DMA.

| • | 1 Unit Load (UL) is defined as: | loh = .04mA @ 2.4V |

|---|---------------------------------|--------------------|

|   |                                 | lol = 1.6mA @ 0.5V |

| A00 - A19                             | 0                | ADDRESS                                                                                                  | SOURCE: U41, U42, U61<br>Drive - 65/15 UL<br>Latch Strobe - ALE<br>Output Enable - AEN<br>Alternate external source |

|---------------------------------------|------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| D0-D7                                 | I/O              | DATA                                                                                                     | SOURCE: U62<br>Drive - 37/15 UL<br>Direction Control - RD*<br>(CPU read signal)<br>Enable - DEN*                    |

| ALE<br>IOW*<br>IOR*<br>MEMW*<br>MEMR* | 0<br>0<br>0<br>0 | ADDRÉSS LATCH STROBE<br>I/O WRITE STROBE<br>I/O READ STROBE<br>MEMORY WRITE STROBE<br>MEMORY READ STROBE | SOURCE: U46<br>Drive - 50/7.5 UL<br>Output Enable - AEN<br>Pull-Up - 4.7K ohms<br>Alternate external source         |

| CLK                                   | 0                | CPU CLOCK                                                                                                | 4.77MHz, 33% duty cycle<br>SOURCE: U82<br>Drive - 75/7.5 UL                                                         |

| OSC                                   | 0                | OSCILLATOR                                                                                               | 14.32MHz, 50% duty cycle<br>SOURCE: U82<br>Drive - 75/7.5 UL                                                        |

| NMI                                   | ******           | NON-MASKABLE<br>INTERRUPT                                                                                | To System NMI<br>Load: 1/1 UL, U117                                                                                 |

#### Signal Listing

| READY             | I SYSTEM WAIT                                                           | SOURCE: OPEN-COLLECTOR OR<br>3-STATE BUFFERS<br>Load: 1 UL and 1.0K ohm pull-up.<br>10/0.9 UL<br>Set LOW by Peripherals (I/O or<br>Memory) to extend READ or WRITE<br>cycles. |

|-------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET             | O SYSTEM RESET                                                          | Power On or Manual<br>SOURCE: U82<br>Drive: 75/7.5 UL                                                                                                                         |

| BREQ*             | I BUS REQUEST                                                           | From external masters<br>Load: 1 UL and 10K ohm<br>pull-up. 10/0.9 UL                                                                                                         |

| AEN               | O BUS GRANT                                                             | To external masters<br>SOURCE: U82<br>Drive - 75/7.5 UL                                                                                                                       |

| IR2<br>IR3<br>IR4 | I INTERRUPT REQUEST#2<br>I INTERRUPT REQUEST#3<br>I INTERRUPT REQUEST#4 | To system interrupt controller<br>Load: 1 UL and 2.2K pull-down                                                                                                               |

| AUDIO IN          | Ι                                                                       | From External Sound Source<br>Load: 10k ohms.                                                                                                                                 |

| AUDIO OUT         | O                                                                       | To External Source<br>Drive: 1.25 Volts P-P into 10K                                                                                                                          |

The following are not sourced by the CPU but are to be SOURCED (O) Output or LOADED (I) Input by an external DMA source:

| RFSHRQ<br>DRQ1<br>FDCDMARQ<br>DRQ3       | <ul> <li>REQUEST DMA CHANNEL#0</li> <li>REQUEST DMA CHANNEL#1</li> <li>REQUEST DMA CHANNEL#2</li> <li>REQUEST DMA CHANNEL#3</li> </ul>                    | Dedicated input requests to DMA<br>Load: 8237A-5/9517A<br>1 MOS load 40/160 UL |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| REFRESH*<br>DACK1*<br>FDCDACK*<br>DACK3* | <ul> <li>O ACKNOWLEDGE DRQ0*</li> <li>O ACKNOWLEDGE DRQ1*</li> <li>O ACKNOWLEDGE DRQ2*</li> <li>O ACKNOWLEDGE DRQ3*</li> </ul>                            | Dedicated output<br>acknowledges from DMA.<br>Drive: 8237A-5/9517A<br>2/2 UL   |

| DMATC                                    | O TERMINAL COUNT                                                                                                                                          | Used by DMA Controller to indicate<br>Terminal Count reached.<br>Drive: 2/2 UL |

| + 5VDC<br>+ 12VDC<br>- 12VDC<br>GROUND   | +5VDC $\pm$ 4% 3.0 Amps available on th<br>+12VDC $\pm$ 5% 0.5 Amps available on<br>-12VDC + 8.3% - 25% 0.06 Amps a<br>Power Return for +5, +12, -12 VDC. | the bus.                                                                       |

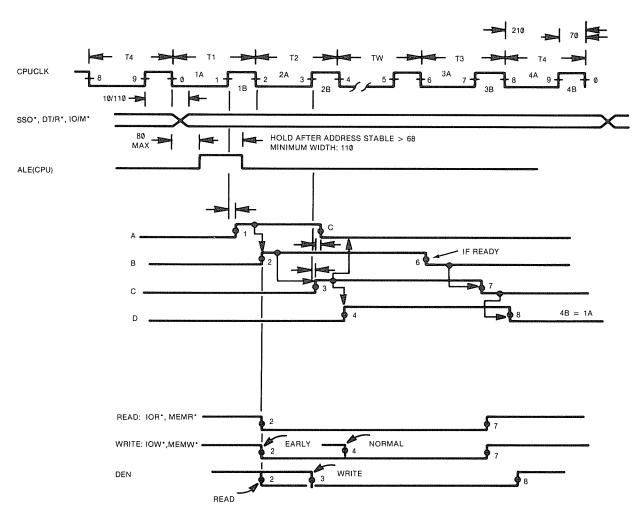

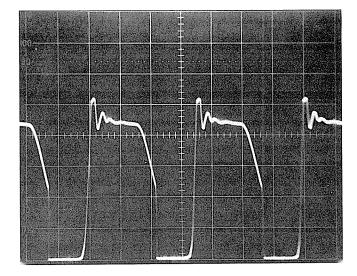

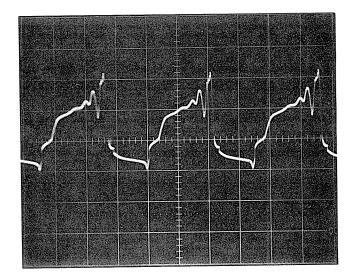

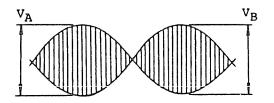

Figure 5 CPU/BUS Timing Signal

)

Figure 5.1 CPU/BUS Timing Signal

## 6 / THEORY OF OPERATION

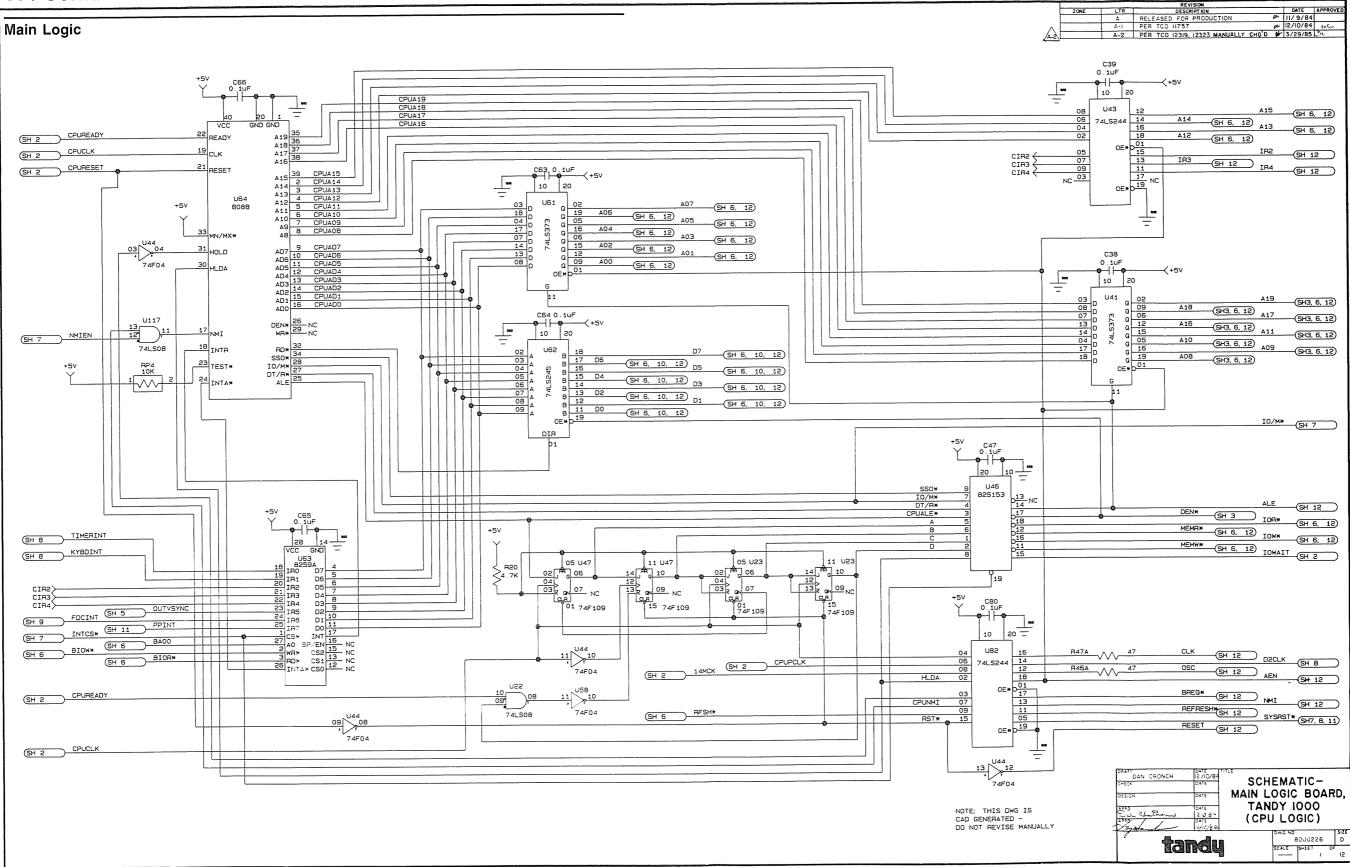

#### Main Logic Board

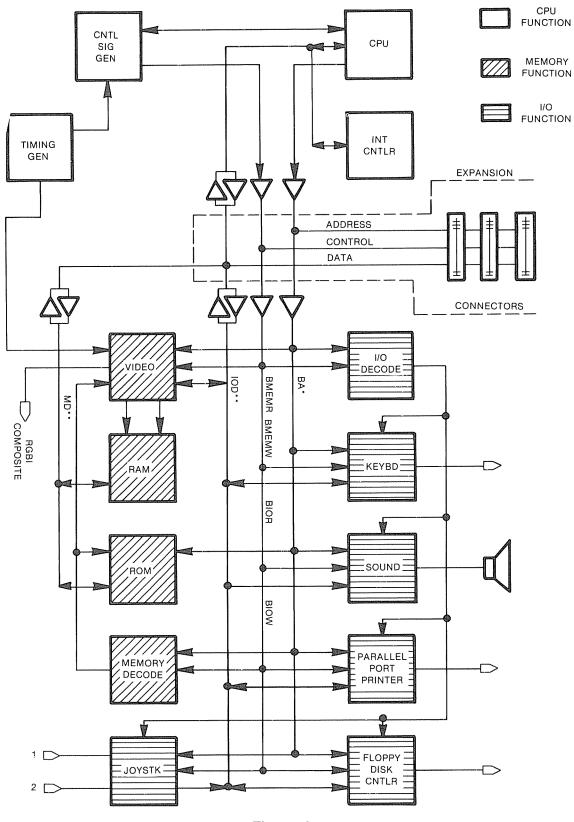

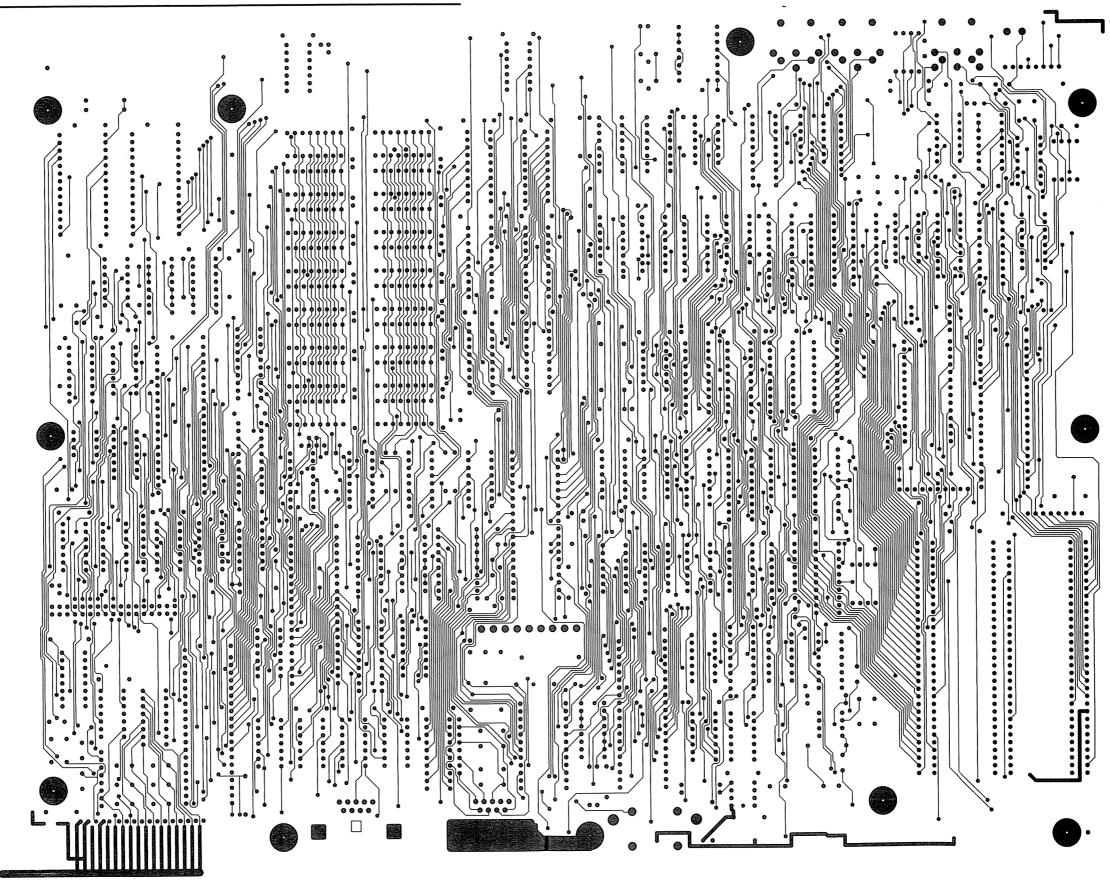

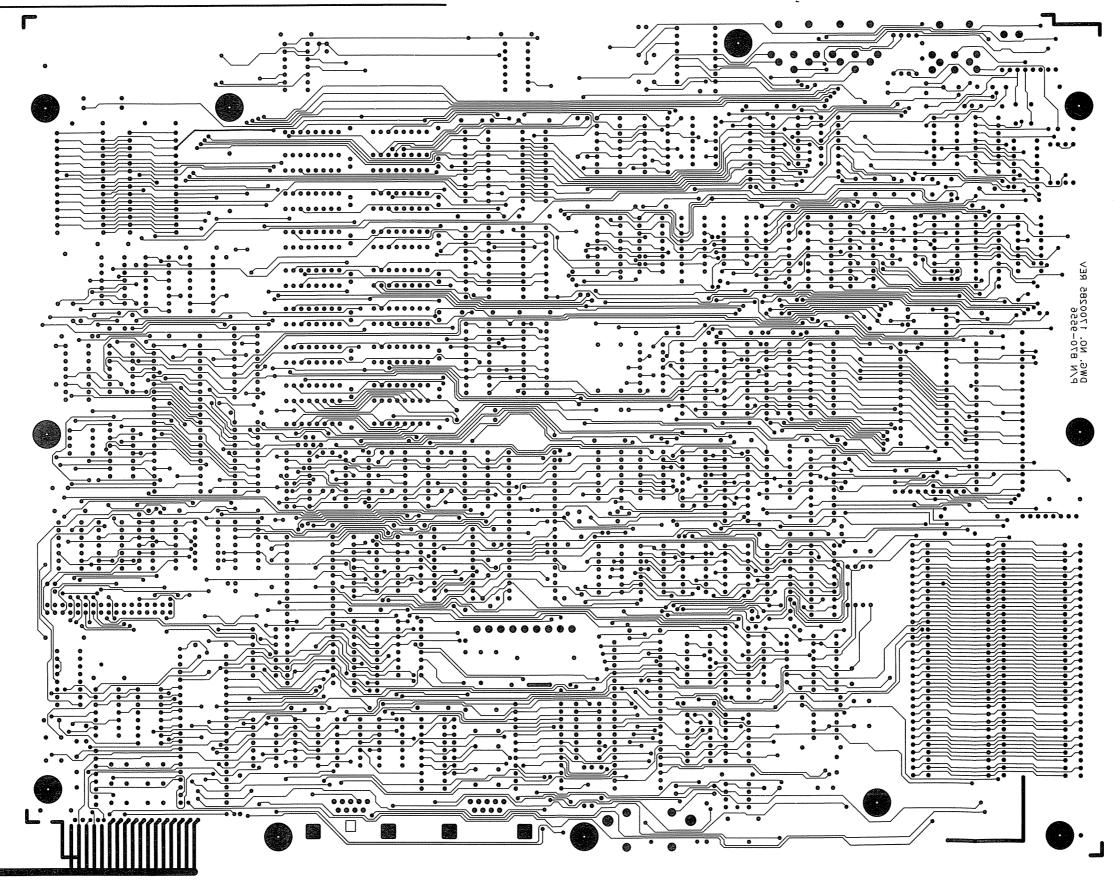

The Block Diagram of the main logic board (Figure 6) shows the basic functional divisions.

## **CPU Function**

The CPU function consists of the CPU (Intel 8088), the address, data interface, the CPU control signal generator, the bus control signal generator and the interrupt controller (Intel 8259A). It is located in the upper right hand corner of the board above the external bus connectors.

## Non-CPU Function, Main Logic Board

The non-CPU functions can be divided into two main parts: memory and I/O. Memory consists of RAM and ROM. RAM or Video/System Memory serves as storage for both the video data and program data. ROM memory contains the BIOS and diagnostics. I/O consists of all the peripheral functions; keyboard, floppy disk controller, printer, joystick, light pen and sound.

#### **Processor Address/Data Interface**

The 8088 has three groups of Address/Data lines; AD0 - AD7, A8 - A15 and A16 - A19. AD0 - AD7 are multiplexed address and data lines. To separate and save the address that comes out first, the signals are applied to U61 (74LS373) and latched by ALE. Additionally, the signals are applied to data transceiver U62 (74LS245): U62 is enabled only during the data portion of the CPU cycle. (The exception is during an Interrupt Acknowledge cycle.) Direction of transmission is controlled by the RD\* (READ) signal from the CPU. Address lines A8 - A15 are present during the entire CPU cycle and need only to be buffered. Address lines A16 - A19 are multiplexed with status signals S4 - S7 and need to be latched. The results are: A8 - A11, A16 - A19 are latched into U41 (74LS373) by ALE and A12 - A15 are buffered by half of U43 (74LS244). The outputs from these latches/buffers/transceivers are the BUS Signals A00 - A19, D0 - D7.

## **CPU Control Signal Generation**

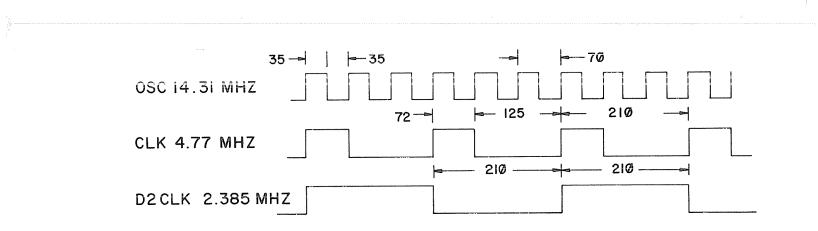

The 8088 CPU uses a 4.77 MHz clock with a special duty cycle (33% high, 67% low.) This clock is produced by the 8284 clock generator/driver U45. The 8284 receives a 14 MHz input clock and divides it by 3 to produce CPUCLK (4.77 MHz) and by 6 to produce D2CLK (2.385 MHz). In addition to being used by the control signal logic the clocks are buffered by U82 (74LS244) for the bus signals OSC (14 MHz), (4.77 MHz) and main logic signal D2CLK (2.385 MHz). (See the Bus Interface Specification)

The RESET signals (CPURESET, SYSRST\*, RST\*) originate at U45 (8284) which synchronizes the input RES\*. RES\* originates from C26 which is shorted to 0 volts by either the manual reset switch or by diode CR6 when the power is off.

The READY circuit synchronizes the system ''ready'' signals with the CPU clock and generates the CPU input CPUREADY. If a function needs one or more ''wait'' states added to its access, it must set the READY line low. From the main logic board, READY is set low by the sound IC for 32 extra ''wait states'' and the video/system memory sets READY low for typically one or two ''wait'' cycles. The READY circuit of the 8284 (U45) is operated in the non-asynchronous mode; i.e. two sequential edges of clock (a rising edge first) are required to set the CPUREADY signal true. Of the four inputs provided, two are used, RDY2 and AEN2. Inputs to RDY2 must be high and the input to AEN2 must be low to set CPUREADY high. Only one input is applied to AEN2: IOWAIT which is a positive pulse generating one ''wait'' state for every I/O cycle. The signal READY applied to the RDY2 input comes directly from the BUS and is the wired-or (logical OR) of any/all READY's from the subsystems which need ''wait state(s)'' inserted. READY is pulled-up by R34.

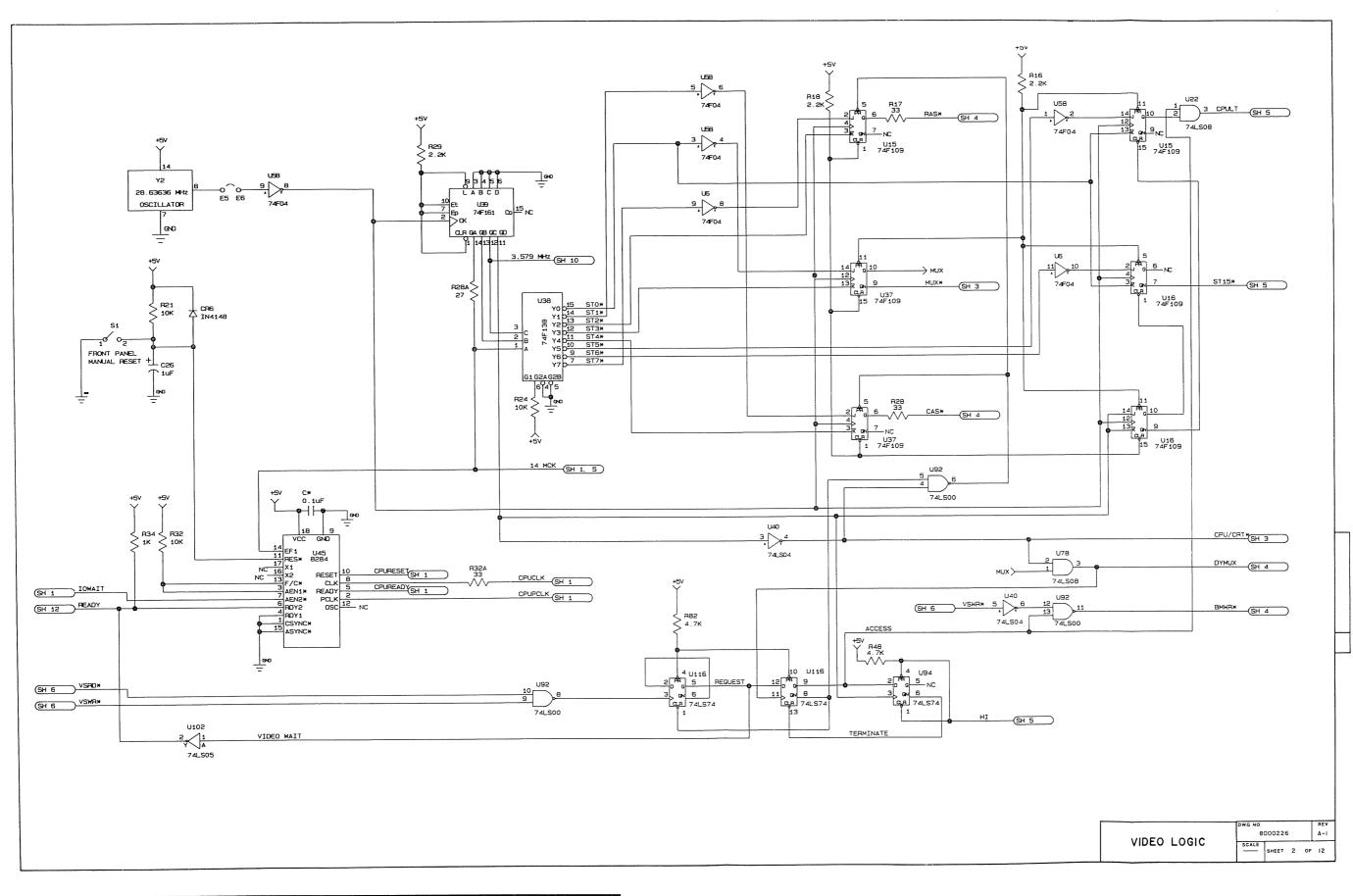

#### **Oscillator Timing and Dynamic RAM Control**

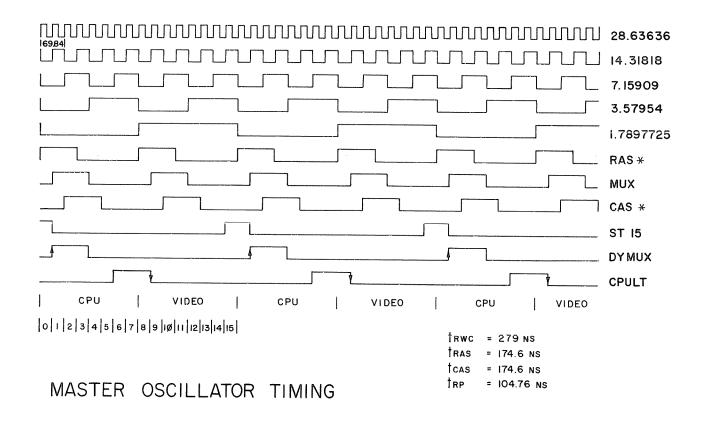

The main system timing starts with the 28.63636 MHz oscillator. This oscillator is a single package which produces a TTL output. From the oscillator, U39 divides the master frequency into 4 multiples. The timing diagram (Figure 6.1) shows this division. 14.31818 MHz is used to clock the video array chip, and also is used by the Intel 8284 to generate the CPU clock signal.

The first three outputs from the counter (U39) are used to derive 8 time states, (U38) and the last output is used to effectively double the number to 16. These 16 time states are shown at the bottom of Figure 6.1. These time states are then used as J-K inputs for F109 flip-flops, which generate the system timing signals RAS<sup>\*</sup>, CAS<sup>\*</sup> and MUX.

The timing diagram shows RAS\* and CAS\* as constantly occuring pulses which cycle every 279 ns. Only the RAS\* and CAS\* pulses for the video cycles are constant. During the CPU cycle, RAS\* and CAS\* pulse will occur only if the CPU is accessing memory. This function is controlled by U116 and ½ of U94. A CPU request for accesses is first latched by the first half of U116. As soon as the next CPU cycle time starts, the second half of U116 is clocked and the CPU access cycle starts. The CPU cycle lasts until the rising edge of RAS\* in the video cycle.

The other signals generated by the system timing are STIS, DYMU, and CPULT. ST15 is a syncronization signal for the Video Array chip, and references time state 0 from U39. DYMUX occurs on the rising edge of MUX in the CPU cycle and latches the video data. The final signal, CPULT occurs only during a CPU access and is used to latch read data for the CPU.

Figure 6 Main Logic Block Diagram

Figure 6.1 Master Oscillator Timing (All Times in Nanoseconds)

## **IFL Equations**

#### **U53 Memory Address Decode**

| Code: 5 | 3G |

|---------|----|

|---------|----|

Checksum: 50C9

#### **Equations:**

=  $RFSH^* \cdot \overline{MEMR}^* \cdot \overline{19} \cdot \overline{18} \cdot \overline{17} \cdot \overline{MC3} \cdot \overline{MC2} \cdot \overline{MC1}$ VSACC\* 19.18.17.MC3.MC2.MC1 +  $\overline{19} \cdot 18 \cdot \overline{17} \cdot \overline{MC3} \cdot MC2 \cdot \overline{MC1}$ + $\overline{19} \cdot 18 \cdot 17 \cdot \overline{\text{MC3}} \cdot \text{MC2} \cdot \text{MC1}$ + + RFSH\*·MEMR\*·19·18·17·MC3·MC2·MC1 + RFSH\* · MEMW \* · 19 · 18 · 17 · MC3 · MC2 · MC1 19.18.17.MC3.MC2.MC1 +  $\overline{19} \cdot 18 \cdot \overline{17} \cdot \overline{MC3} \cdot MC2 \cdot \overline{MC1}$ + + RFSH\*·MEMW\*·19·18·17·MC3·MC2·MC1 + HGMEMAC HGMEMAC<sup>\*</sup> = RFSH<sup>\*</sup>  $\cdot$  MEMR<sup>\*</sup>  $\cdot$  19  $\cdot$  18  $\cdot$  17  $\cdot$  16  $\cdot$  15 + RFSH\* · MEMW \* ·19 · 18 · 17 · 16 · 15 ROMSCO\*  $= \text{RFSH}^* \cdot \overline{\text{MEMR}}^* \cdot 19 \cdot 18 \cdot 17 \cdot 16 \cdot 15 \cdot 14 \cdot 13$  $= RFSH^* \cdot \overline{MEMR}^* \cdot 19 \cdot 18 \cdot 17 \cdot 16 \cdot 15 \cdot 14 \cdot \overline{13}$ ROMSC1\*

MEMSEL\* = VSACC\*· + HGMEMAC\* + ROMCSO\* + ROMCS1\*

#### U80 Main I/O Address Code

#### Code: 80B

Checksum: 58F9

$5 \cdot 4$

| Inputs:                                             | Addresses                                                                                                                                                                                    |  |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IO0SEL*<br>IO1SEL*<br>IO4SEL*<br>IO6SEL*<br>IO7SEL* | $ \begin{array}{rcrcrcrcrcrcrcrcl} 15 \cdot 14 \cdot 13 \cdot 12 \cdot 11 \cdot 10 \cdot 9 \cdot 8 \cdot 7 \\ = & 0 \cdot 0$ |  |

## Outputs:

| INTCS*    | $= 100SEL^* \cdot \overline{6} \cdot 5 \cdot \overline{4} \cdot \overline{3}$            |

|-----------|------------------------------------------------------------------------------------------|

| TMRCS*    | $= 100SEL^* \cdot 6 \cdot \overline{5 \cdot 4 \cdot 3}$                                  |

| PIOCS*    | $=  OOSEL^* \cdot 6 \cdot 5 \cdot \overline{4 \cdot 3}$                                  |

| NMICS*    | $= \text{IOISEL}^* \cdot \overline{6} \cdot 5 \cdot \overline{4} \cdot \overline{3}$     |

| SNDCS*    | $= \text{IO1SEL}^* \cdot 6 \cdot \overline{5 \cdot 4 \cdot 3}$                           |

| JOYSTKCS* | $= IO4SEL^* \cdot \overline{6} \cdot \overline{5} \cdot \overline{4} \cdot \overline{3}$ |

| PRINTCS*  | $= IO6SEL^* \cdot 6 \cdot 5 \cdot 4 \cdot 3$                                             |

| FDCCS*    | $= 107SEL^* \cdot 6 \cdot 5 \cdot 4 \cdot 3$                                             |

| IOSEL "   | = $TMRCS^{+}$ + $PIOCS^{+}$ + $NMICS^{+}$ + $SNDCS$                                      |

|           | + PRINTCS* + FDCCS* + IO7SEL*·6·5                                                        |

|           |                                                                                          |

## U46 System Timing Synthesizer

•

#### Code: 46DC

Checksum: 3E69

#### Equations:

| ALE    | = HLDA · CALE                                                                                                   |

|--------|-----------------------------------------------------------------------------------------------------------------|

| DEN*   | $= \overline{HLDA} \cdot IO/M \cdot \overline{DT/R} \cdot C \cdot INTCS^* \cdot SS0 (IOR) \cdot (during IOR^*)$ |

|        | + HLDA · IO/M · DT/R · C · INTCS* · (MEMR) · (during IOR*)                                                      |

|        | + HLDA · B · DT/R · · INTCS* · SS0 (MEMW) ·<br>(during IOR*)                                                    |

|        | + HLDA · · DT/R · C · INTCS* · SS0 (MEMW) ·<br>(during IOR*)                                                    |

| IOR*   | $= \overline{HLDA} \cdot IO/M \cdot B \cdot \overline{DT/R} \cdot SS0^*$                                        |

| MEMR*  | $= \overline{HLDA} \cdot \overline{IO/M} \cdot B \cdot \overline{DT/R} \cdot$                                   |

| IOW*   | $= \overline{HLDA} \cdot IO/M \cdot B \cdot DT/R \cdot \overline{SSO}$                                          |

| MEMW*  | $= \overline{HLDA} \cdot \overline{IO/M} \cdot B \cdot DT/R \cdot \overline{SSO}$                               |

| IOWAIT | $= \overline{HLDA} \cdot IO/M \cdot A \cdot \overline{DT/R} \cdot SSO$                                          |

|        | + $\overline{\text{HLDA}} \cdot \text{IO/M} \cdot \text{A} \cdot \text{DTR}$                                    |

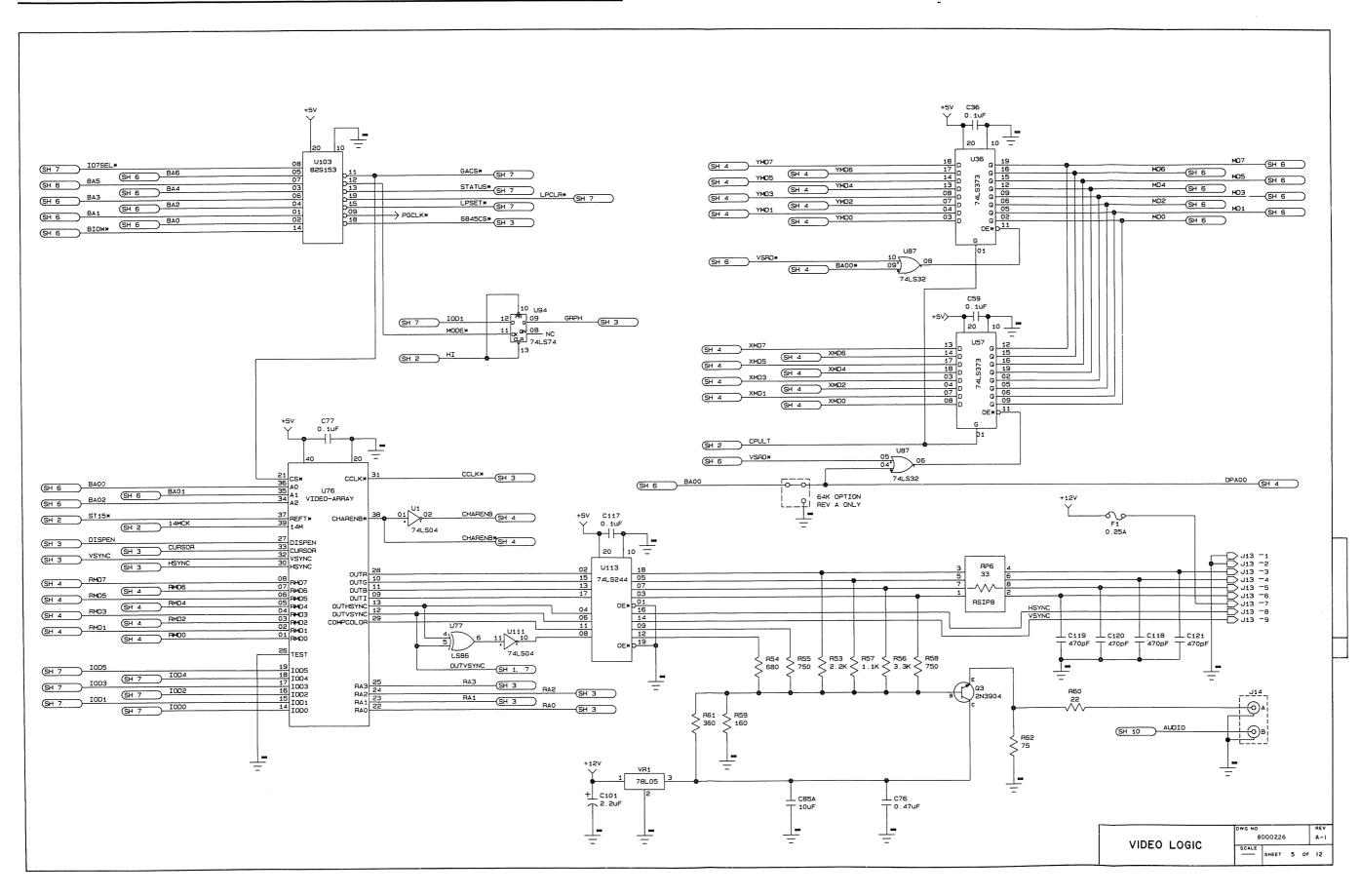

#### U103 Video Address Decode

Code: 103C

#### Checksum: 44B0

| GACS*   | $= \cdot \overline{10W} \cdot \overline{107SEL^*} \cdot 6 \cdot \overline{5} \cdot 4 \cdot 3 \cdot \overline{2} \cdot \overline{1} \cdot \overline{0} \cdot MODE^*$             |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | $+ \cdot \overline{IOW} \cdot \overline{IO7SEL^*} \cdot 6 \cdot \overline{5} \cdot 4 \cdot 3 \cdot \overline{2} \cdot \overline{1} \cdot 0$                                     |

|         | + $\cdot \overline{\text{IOW}} \cdot \overline{\text{IO7SEL}^*} \cdot 6 \cdot \overline{5} \cdot 4 \cdot 3 \cdot \overline{2} \cdot 1 \cdot \overline{0} \cdot \text{STATUS}^*$ |

|         | $+ \cdot \overline{IOW} \cdot \overline{IO7SEL^{\star}} \cdot 6 \cdot \overline{5} \cdot 4 \cdot 3 \cdot 2 \cdot 1 \cdot 0$                                                     |

| STATUS* | $= 107SEL^* \cdot 6 \cdot \overline{5} \cdot 4 \cdot 3 \cdot \overline{2} \cdot \overline{1} \cdot 0$                                                                           |

| MODE*   | $= \cdot IOW \cdot IO7SEL^* \cdot 6 \cdot \overline{5} \cdot 4 \cdot 3 \cdot \overline{2} \cdot \overline{1} \cdot \overline{0}$                                                |

| LPCLR*  | $= \overline{IO7SEL^*} \cdot 6 \cdot \overline{5} \cdot 4 \cdot 3 \cdot \overline{2} \cdot 1 \cdot 0 \cdot \overline{IOW}$                                                      |

| LPSET*  | $= \overline{IO7SEL^*} \cdot 6 \cdot \overline{5} \cdot 4 \cdot 3 \cdot 2 \cdot \overline{1} \cdot \overline{0} \cdot \overline{IOW}$                                           |

| PGCLK*  | $= \overline{IO7SEL^*} \cdot 6 \cdot \overline{5} \cdot 4 \cdot 3 \cdot 2 \cdot 1 \cdot 0 \cdot \overline{IOW}$                                                                 |

| 6845CS* | $= \overline{107SEL^*} \cdot 6 \cdot \overline{5} \cdot 4 \cdot \overline{3} \cdot$                                                                                             |

|         |                                                                                                                                                                                 |

## System Control Signal Generation

The System Control Signal Generator provides the timing strobes required by the system. These include IOW\*, IOR\*, MEMW\*, MEMR\*, ALE, DEN\* and IO/M\*. These signals are synthesized by U46 (IFL) from timing signals A,B,C,D, 8088 status signals SSO\*, DT/R\*, IO/M\* plus HLDA and INTCS\* (8259 chip select). Timing signals A, B, C, D come from flip-flops U23 and U47. The timing clock is CPUCLOCK. A CPU cycle is divided into five periods: T1, T2, T3, TWAIT, and T4. Each cycle has a clock rising edge and a clock falling edge. Thus T1 + denotes rising, and T1 – denotes falling. Signal "A" is started by ALE true (T1 +) and stopped by "C", (T2 +). Signal "B" is started by "A" and (T1 –) and stopped by CPUREADY, and "D". Signal "C" is started by "B'', (T2 +) and stopped by "BNOT", (T3 +). Signal "D" is started by "C", (T2 –) and stopped by "CNOT", (T3 –). Characteristically, "A" is always one clock long while "B", "C" and "D" are variable in length depending on the number of inserted "wait" states. Thus any half-clock period between T1 + and T3 – can be logically combined to create the output timing signals. See Figure 7.

All external devices, except the 8259A Interrupt Controller, are buffered by an LS244 that is controlled by the DEN\* signal. Since the 8259A is not buffered, the DEN\* signal must remain inactive during accesses to the 8259A.

## **Bus Specification**

Specifications for the bus will include the expansion connector pin/signal assignments and the signal characteristics. Refer to the Expansion I/F Connector diagram. See Figure 8.

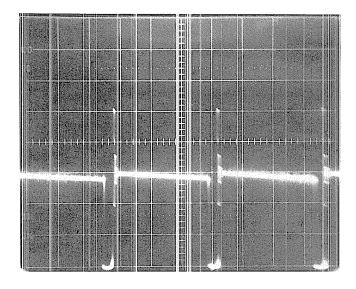

TIMING DIAGRAM

Figure 7 (All Times in Nanoseconds)

## **EXPANSION I/F CONNECTOR**

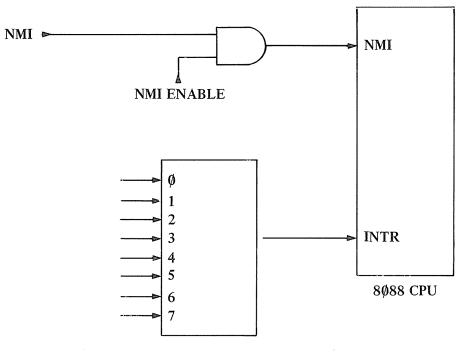

## **Interrupt Function**

The 8088 supports two types of interrupts: maskable (by the CPU, INT) and non-maskable (NMI). See Figure 9. The 8259A Interrupt Controller is the source of the INT for the 8088. The 8259A has eight interrupt inputs controlled through software commands. It can mask (disable) and prioritize (arrange priority) to generate INT. These eight interrupts are:

| #0 | Timer Channel 0         | Software Timer                      |

|----|-------------------------|-------------------------------------|

| #1 | Keyboard                | Keyboard Code Received              |

| #2 | Hard Disk Controller    | Optional Function, Interrupt on Bus |

| #3 | Modem                   | Optional Function, Interrupt on Bus |

| #4 | RS-232                  | Optional Function, Interrupt on Bus |

| #5 | Vertical Sync           | Software Timer for Video            |

| #6 | Disk Controller, Floppy | Ready to Receive/Transmit Data      |

| #7 | Printer                 | Data Transmission Complete          |

The NMI interrupt is not maskable by the CPU but it can be enabled/disabled by hardware. The enable is at Port 00A0 Bit 7. The enable is cleared by RESET. There is no specific function assigned to NMI and it is available on the bus.

)

## **INTERRUPT STRUCTURE**

8259A INTERRUPT CONTROLLER

| INTERRUPT | FUNCTION               |

|-----------|------------------------|

| NMI       | AVAILABLE ON BUS       |

| Ø         | 8253 TIMER CH Ø        |

| 1         | KEYBOARD               |

| 2         | HARD DISK              |

| 3         | SECONDARY COMM.        |

| 4         | PRIMARY COMM.          |

| 5         | VERTICAL SYNC.         |

| 6         | FLOPPY DISK CONTROLLER |

| 7         | PARALLEL PORT          |

Figure 9

## **Bus Interface**

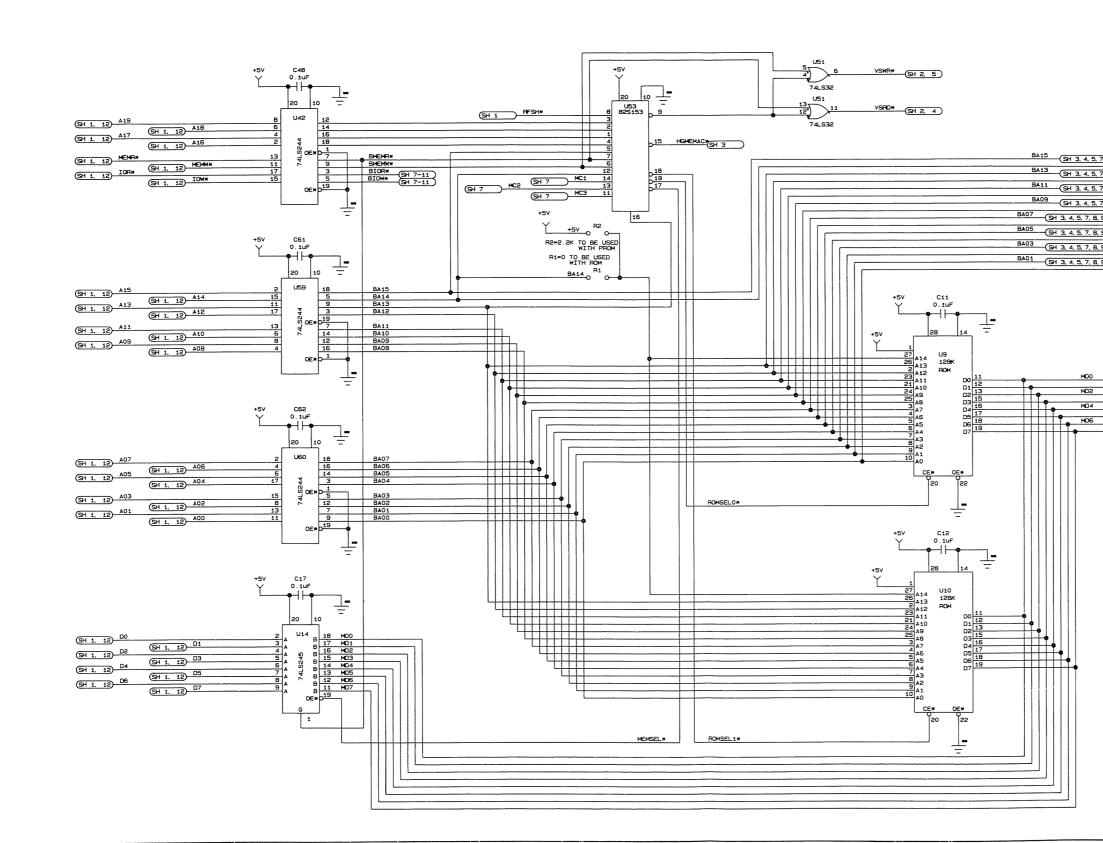

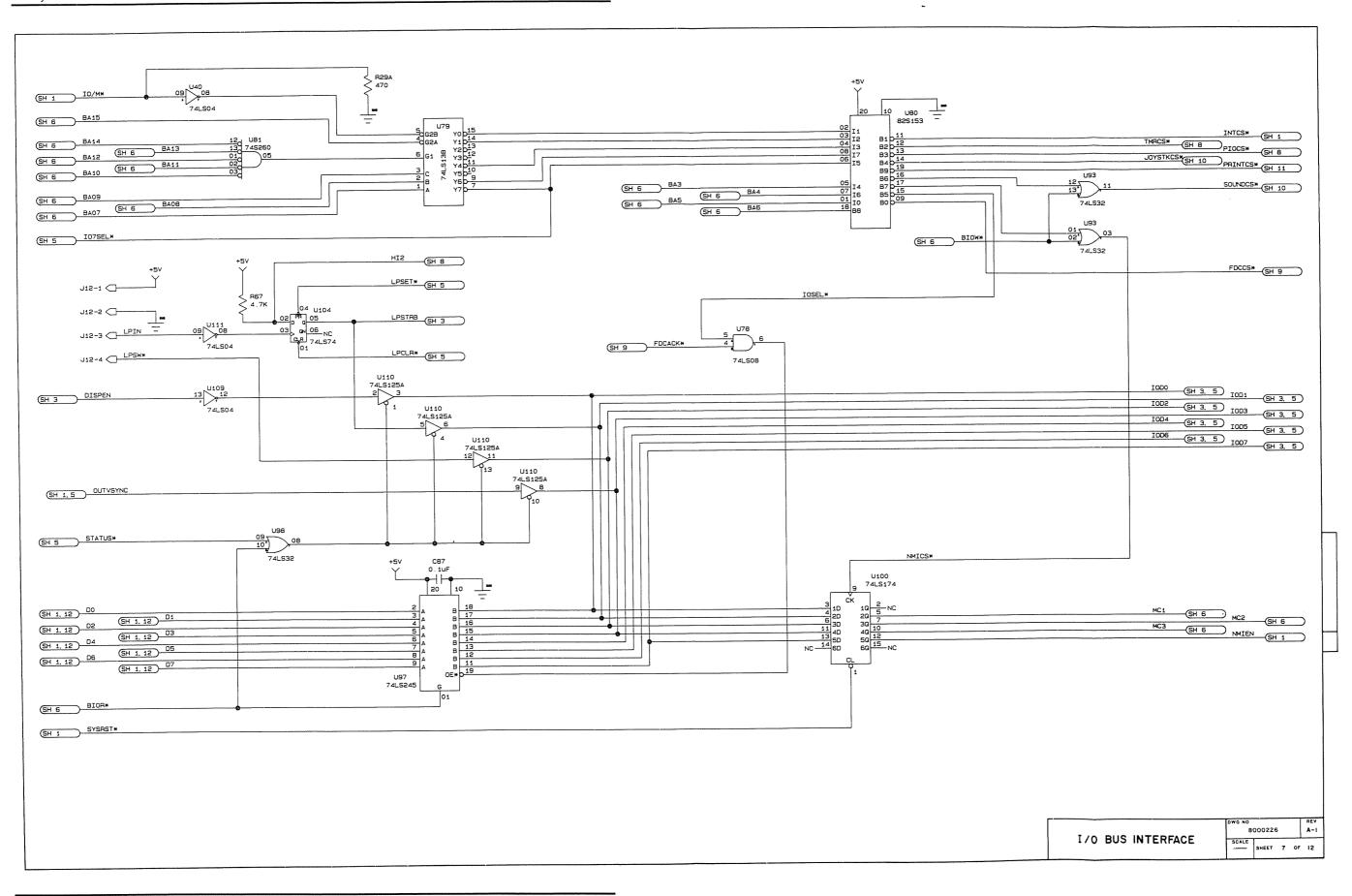

The interface to the main bus is divided into three parts: address/control strobes, memory data and I/O data. The address/control strobe part (BA0 - BA19, BMEMR\*, BMEMW\*, BIOR\*, BIOW\*) is shared by both the I/O and the memory sections. Input buffers are U59, U60 and U42. One function of the address bus is the select logic for each of the functions. U80 decodes all the I/O chip selects except those for the Video/System Memory I/O ports which are decoded by U103. The memory selects are decoded by U53. The I/O data transceiver is U97 with its output enable decoded by U80. The memory transceiver is U14 and its output enable is decoded by U53. The direction control for both data transceivers are the ''read'' strobes; IOR\* for U97 and MEMR– FOR U14.

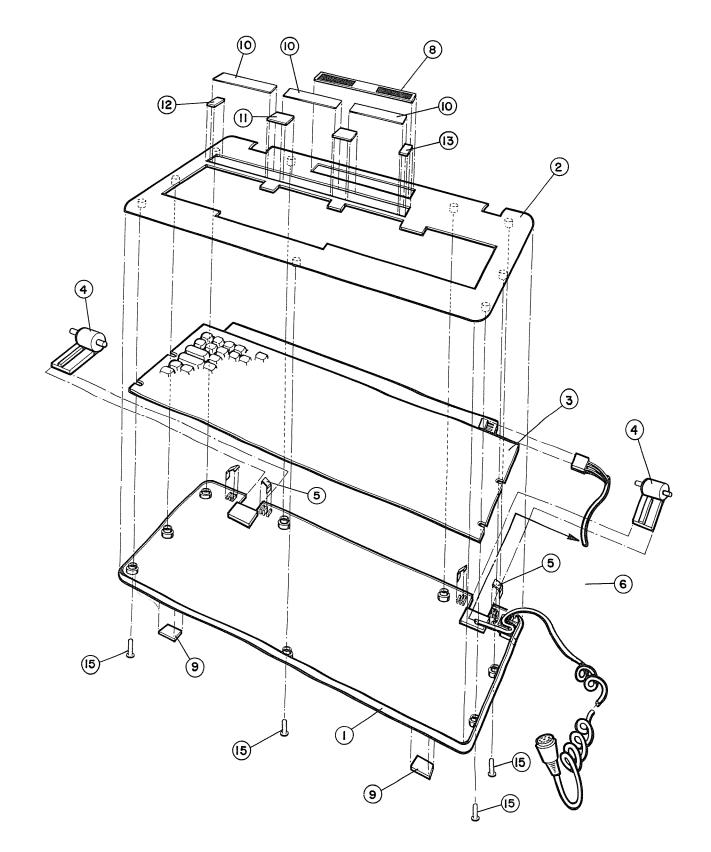

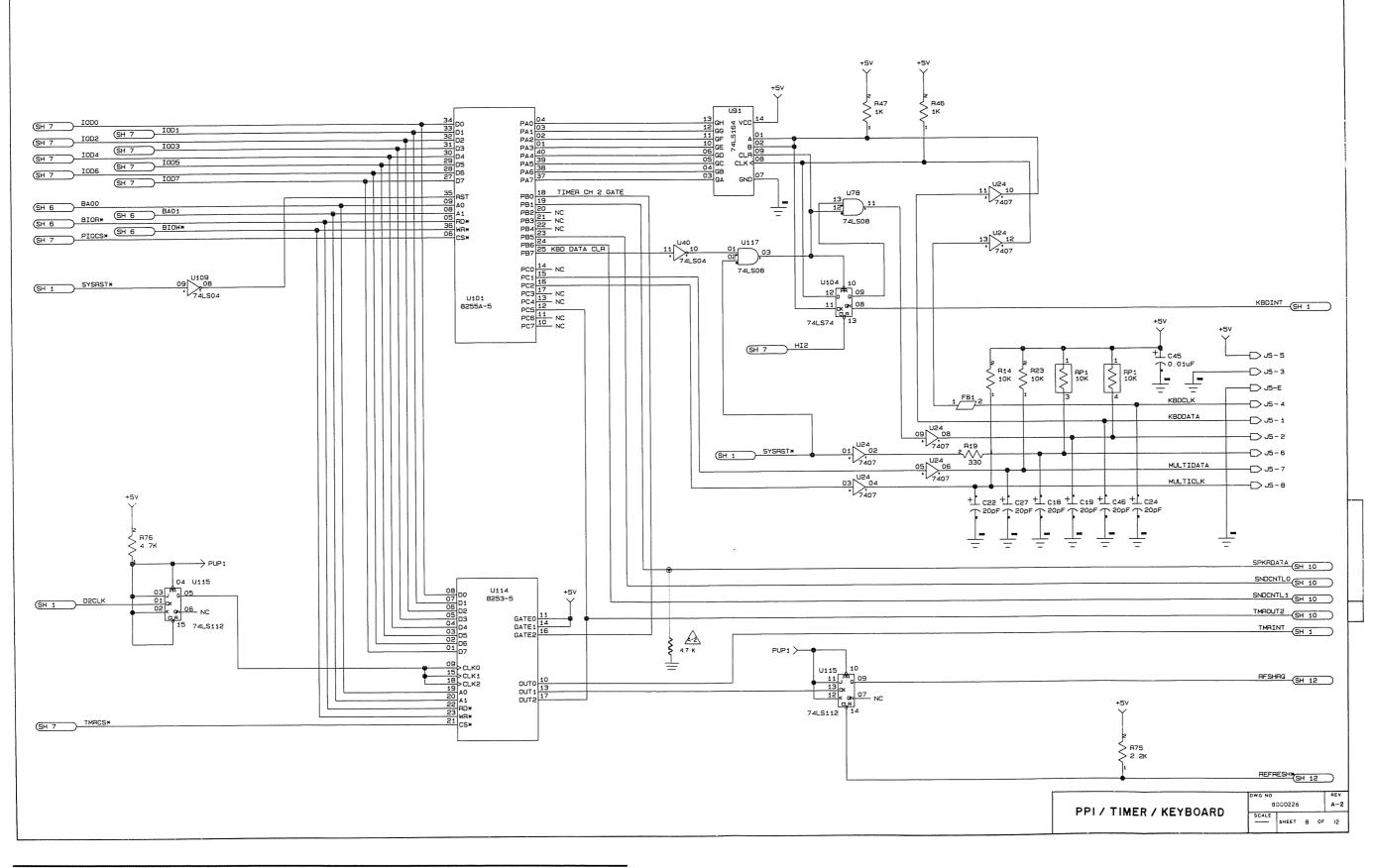

## Keyboard / Timer / Sound Circuits

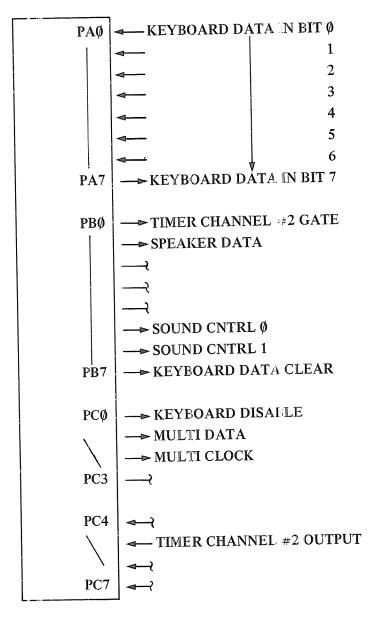

The focal point for this circuit is the 8255 Programmable Peripheral Interface (PPI). It has three 8 bit parallel ports, A, B and C. Port A is configured as an input port and is used for keyboard data. Port B is configured as an output port and is used for control signals for the sound, keyboard and timer functions. Port C is split into 4 inputs, including the timer channel and #2 monitor and 4 outputs including the keyboard/multifunction interface signals. See Figure 10.

## **Keyboard Data**

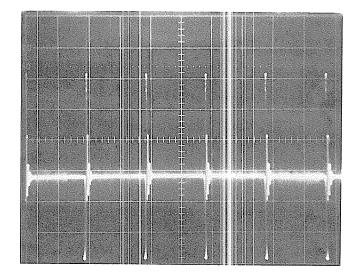

The computer receives data from the keyboard in an asynchronous serial format with one 8 bit word for each keystroke. This serial data is converted by the shift register, U91. This byte is then read by the CPU through the 8255 Port A. On receipt of a character an interrupt is set and the keyboard "BUSY" signal disables further transfers from the keyboard (1/2 of U104). To enable the keyboard again, the "keyboard clear" signal from 8255 Port B must be toggled. This signal when high clears the interrupt, the shift register and holds "BUSY" active (U78 pin 11.) Holding "BUSY" active prevents another character from being sent until the clear routine is complete. The serial data from the keyboard consists of a clock signal and a data signal. The clock consists of 8 consecutive positive pulses (signal normal state is logic low). The rising edge of each pulse is centered in the middle of each data period. The data signal consists of 8 data periods and a "end-of-character" bit. Normal state of the data signal is logic high which represents a logic 1. Thus the data signal will change only if the data bit is a 0. The ninth and last data bit is always a 0. In the absence of a ninth clock it will strobe a 1 into U104 and set the interrupt and busy signals. See the Keyboard Timing Chart in the Keyboard Chapter.

## PROGRAMMABLE PERIPHERAL I/F 8255A-5 (PPI)

PORT ASSIGNMENTS

32

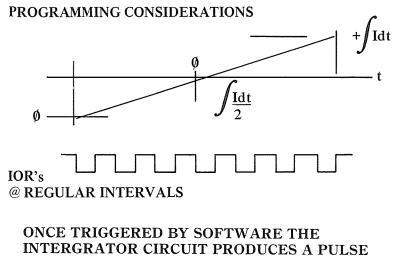

# **Timer Function**

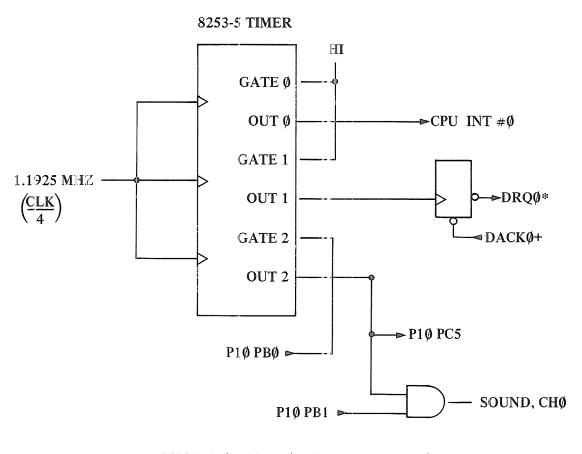

The Timer is an 8253 Timer/Counter consisting of three independent counters. The clock for all three counters is 1.1925 MHz. The gate for counter #0, #1 is permanently ''on''. The gate for counter #2 is controlled by a bit of the 8255 Port B. The output of counter #0 is dedicated to system interrupt #0 (8259 IR0) for software timing functions. The output of counter #1 is dedicated to the REFRESH function. When the optional DMA/Memory board is installed, DMA channel #0 is used for refreshing the RAM memory. Counter #1 sets RFSHRQ\* (DRQ0) every 15 microseconds to initiate a single ''dummy'' memory read. The output of counter #2 is routed to the sound circuit and into the 8255 Port C for monitoring by the CPU. See Figure 11.

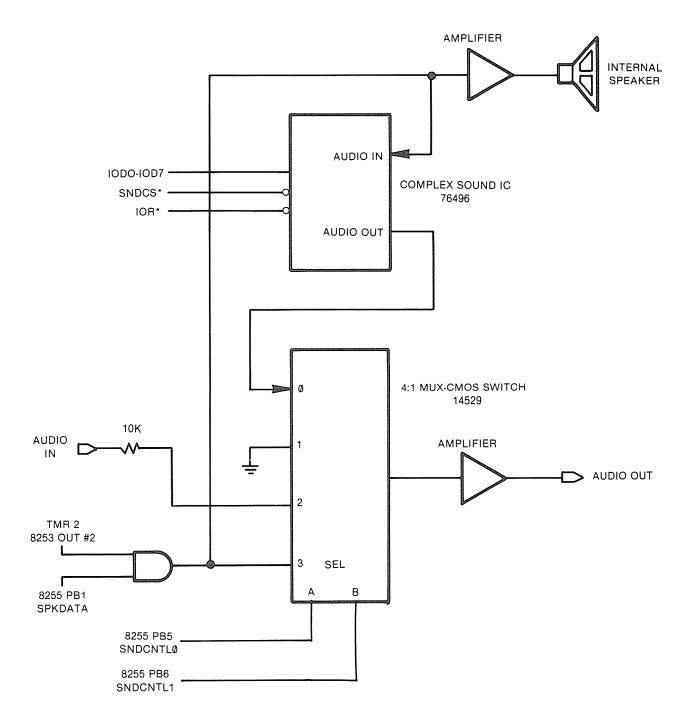

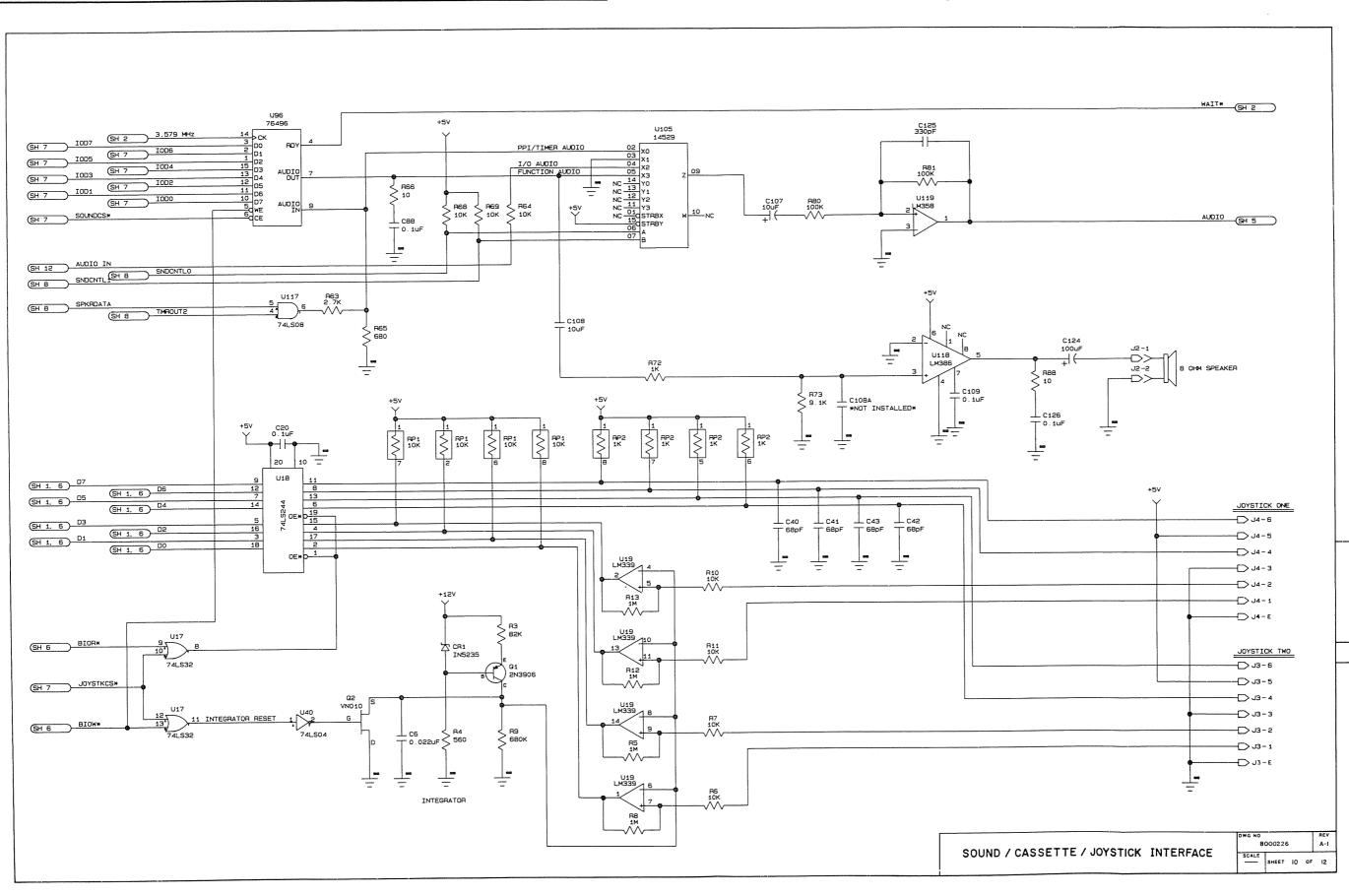

# Sound Function

The sound function consists of an internal and an external sound circuit. The internal sound circuit is directly connected to the speaker via U118. The source of the sound frequencies is U96 Complex Sound Generator. Internally, U96 has four programmable sound generators. The frequency and output level of each is controlled by software. The four internal generators are summed with an external input into a single output. The external source is from the 8253 counter #2 (programmable frequency and fixed amplitude). In addition to being the only source for the unit speaker, it is one of three selectable sources for the external audio out signal. This signal is intended as an input into a external amplifier such as a stereo. The three sound frequency sources are:

- 1. Complex sound generator U96.

- 2. The 8253 counter at channel 2.

- 3. Any external source applied to bus interface pin B08, Audio In.

These are selected by an analog multiplexer U105. Selection signals are SNDCNTL0, SNDCNTL1 from the 8255. The output driver for Audio Out is U119 which is designed to drive a load impedance of 1000 ohms. See Figure 12.

## SYSTEM TIMER 8253-5

CHANNEL Ø: MODE Ø, INTERRUPT ON T/C 1: MODE Ø, NEGATIVE PULSE ON T/C 2: MODE 3, SQUARE WAVE OUTPUT

# SOUND FUNCTIONAL BLOCK DIAGRAM

Figure 12

# Joystick Interface

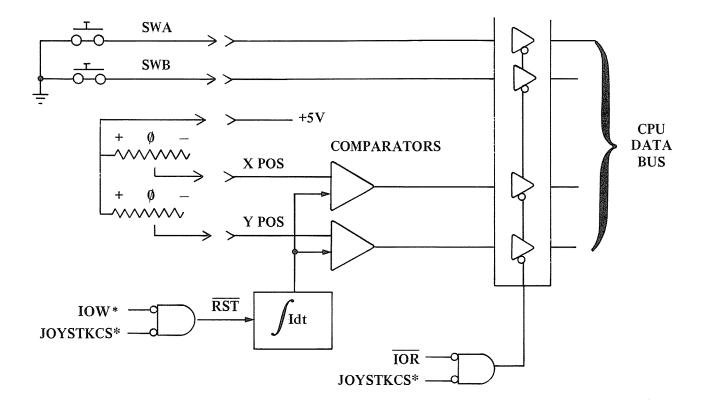

The joystick interface converts positional information from hand-held joysticks (1 or 2) into CPU data. Each joystick provides 1 or 2 push-buttons and X, Y position for a total of 4 bits each. You can use 2 joysticks. The joystick handle is connected to two potentiometers mounted perpendicular to each other; one for X position, one for Y position. Through the cable, the main logic board applies +5 VDC to one side and ground to the other of the pots. The pot wiper is the position signal: a voltage between 0 and +5 VDC. This signal is applied to one input of a comparator U119. The other comparator input is the reference signal (a ramp between 0.0 to +5.0 volts.) When the position signal is equal or less than the reference signal, the comparator output goes true. This comparator output is the X or Y position data bit. The ramp is reset to 0.0 VDC whenever a "write" is made at Port 200/201 Hex. The IOW\* signal turns on Q2, which drains C6 to 0.0 volts. When Q2 is turned off, Q1, R3, R4, R9, and CR1 create a constant-current source that linearly charges C6 to +5.0 VDC in 1.12 milliseconds. The joystick information is "read" by the CPU at Port 200/201 Hex through U18. See Figure 13.

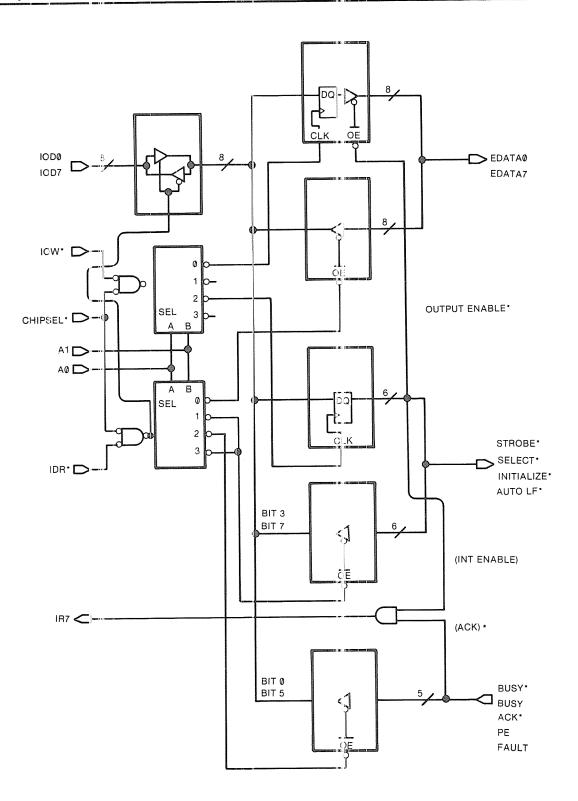

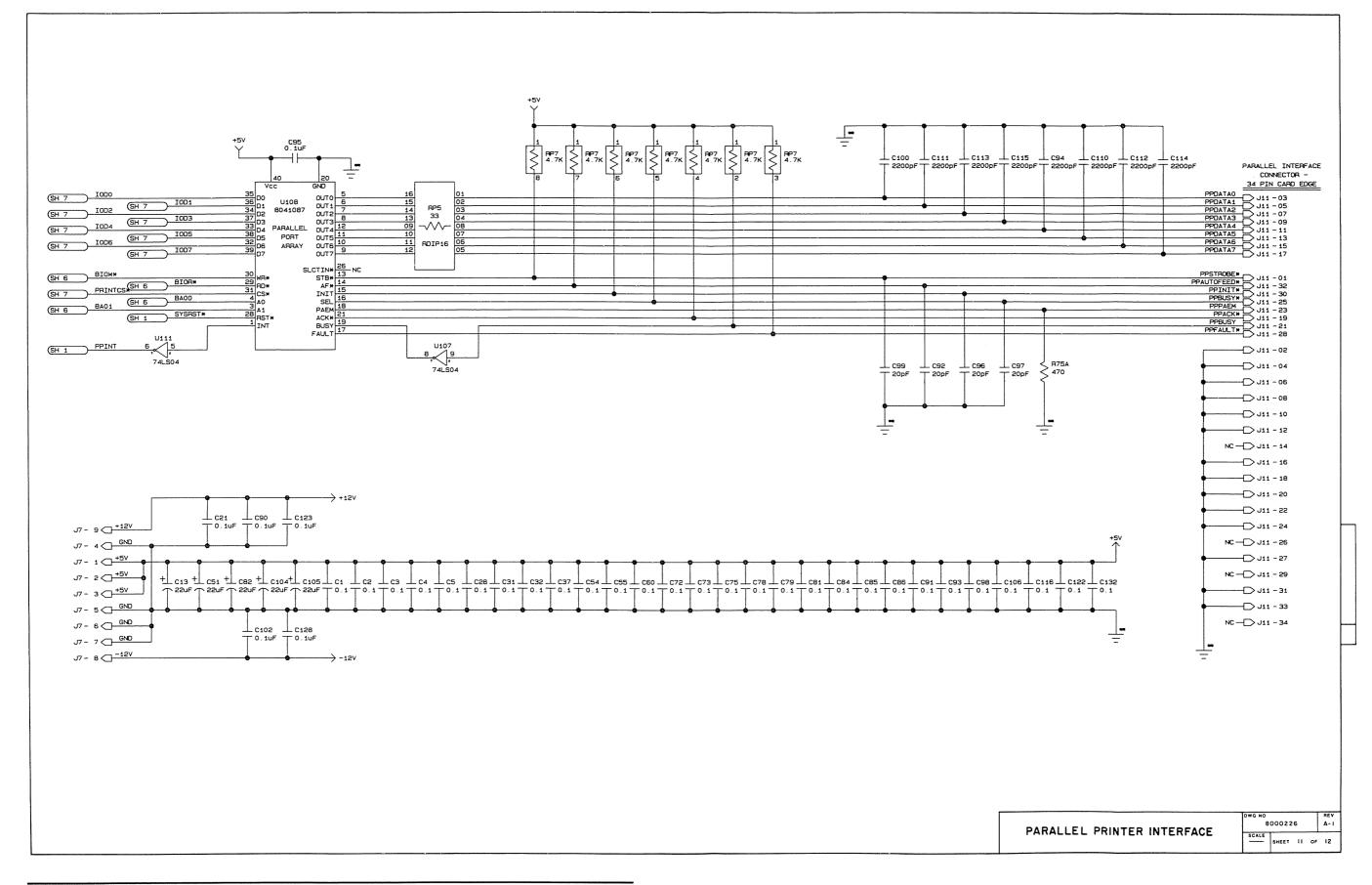

# Printer Interlace

The printer interface is totally contained in a custom Gate Array U108 and is shown in Figure 14. Functionally, the printer interface consists of an output data latch (write @ 378) and accompanying input data buffer. The latch and buffer reads back the output data (read @ 37A) with an accompanying input buffer for read-back (read @ 37A). The input buffer is for reading printer input signals (read @ 379), I/O address decoding, data transceiver, and interrupt logic. The interrupt is (logically) ACKNOWLEDGE\* if interrupts are enabled (37A Bit 4).

# JOYSTICK I/F

THE DURATION OF WHICH IS DEPENDENT ON JOYSK POSITION.

Figure 13

-

## PRINTER SCHEMATIC

Figure 14

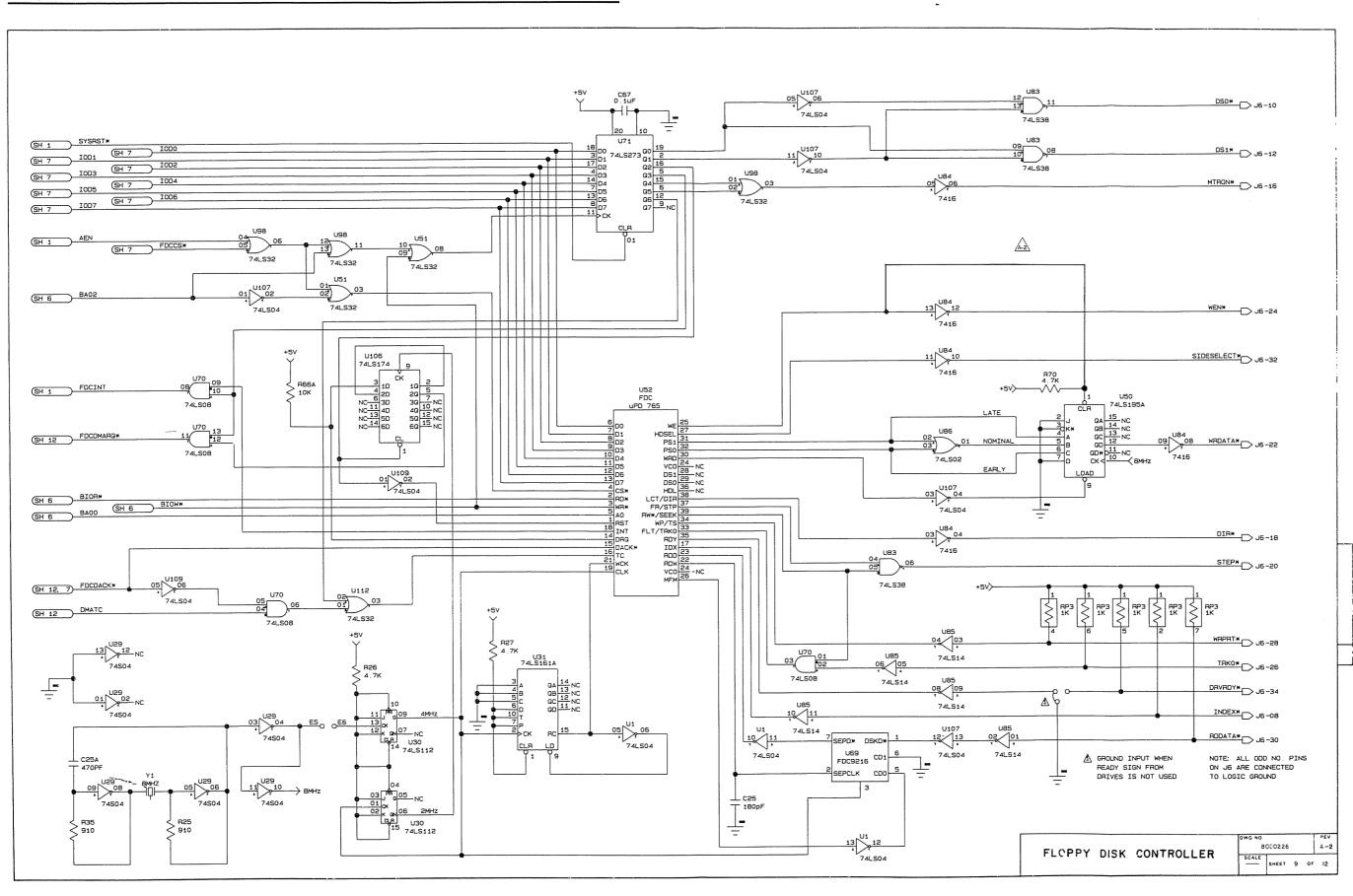

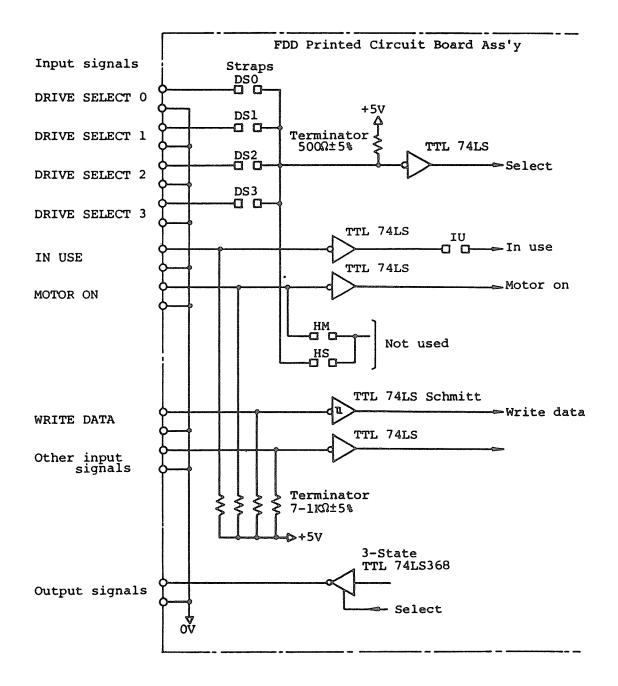

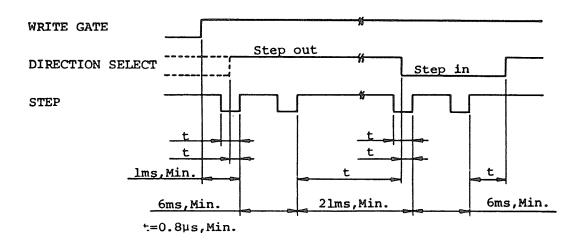

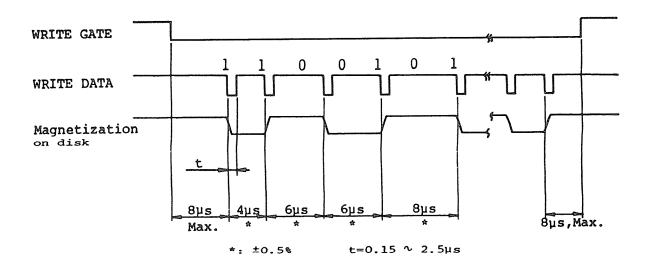

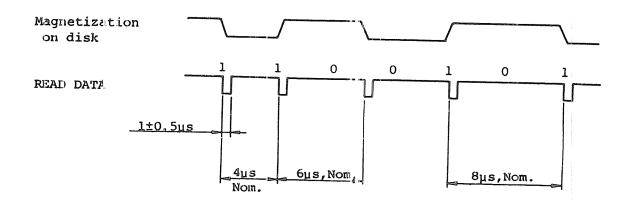

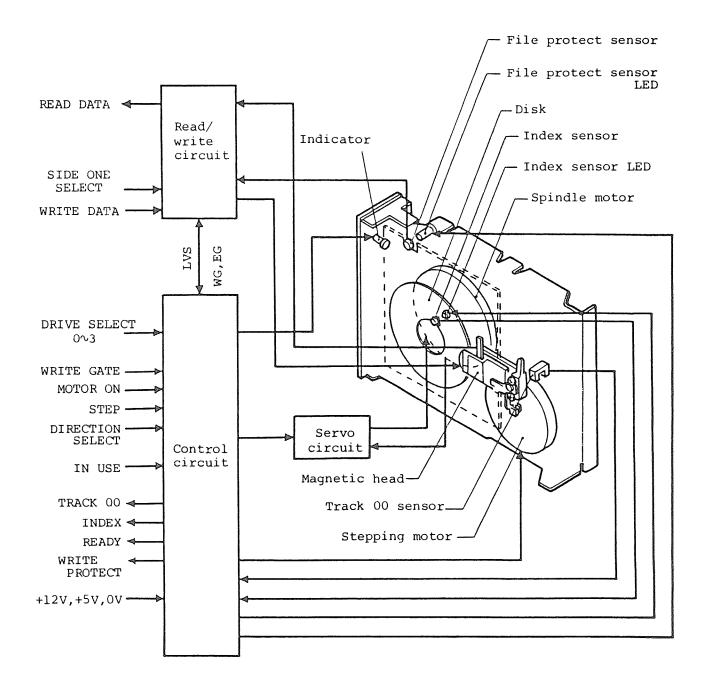

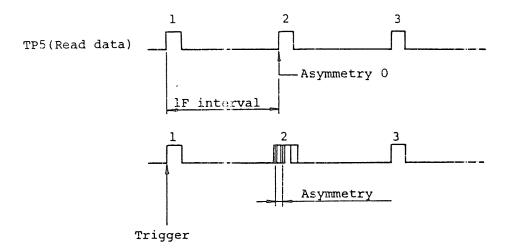

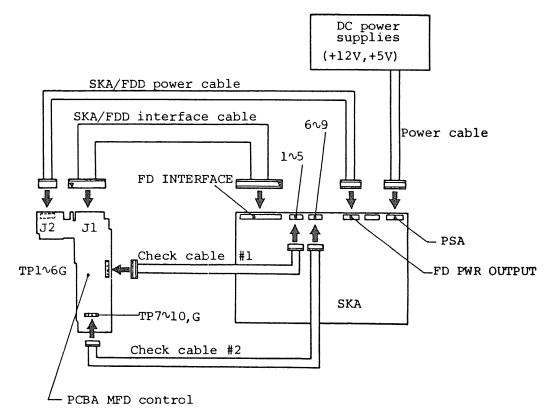

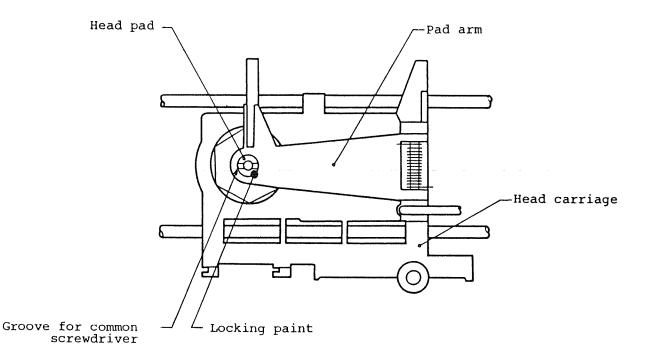

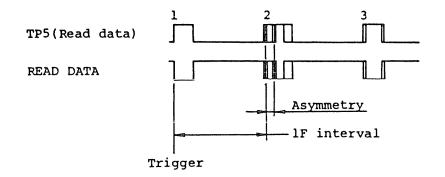

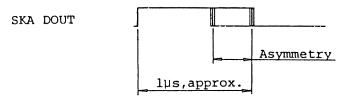

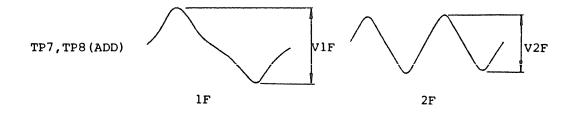

# Floppy Disk Controller Interface

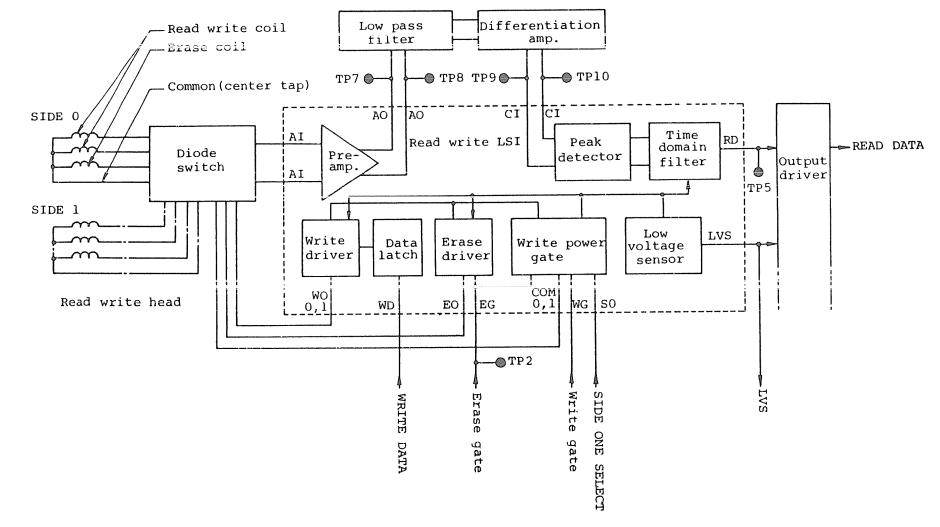

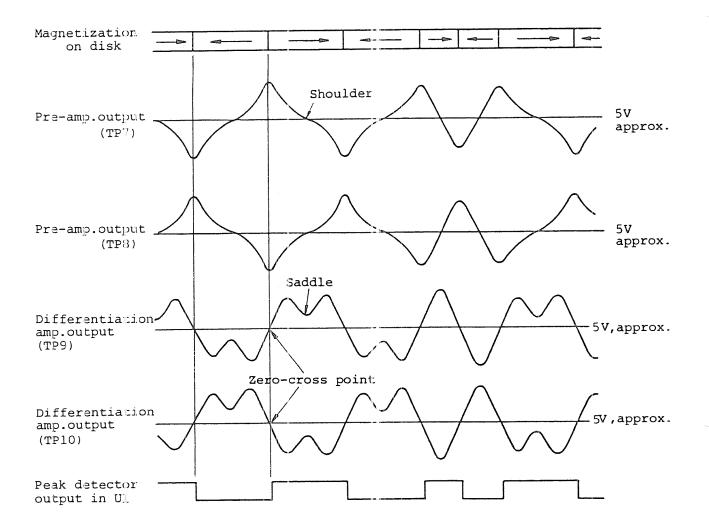

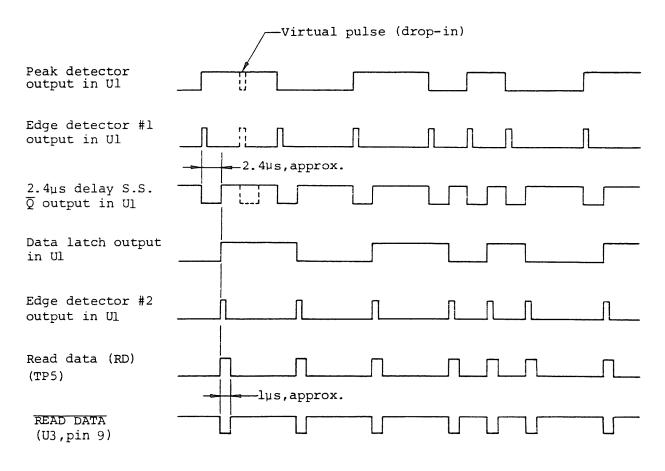

The Floppy Disk Controller interface consists of the 765 controller and support circuitry. The oscillator formed by U29, Y1 generates an 8.00 MHz clock that is divided down to 4.00 MHz and 2.00 MHz by U30. The 4.00 MHz signal is applied to the FDC for its internal processor clock (CLK pin 19) and to counter circuit U31 to generate the FDC write clock (WCK pin 21). U31 produces a pulse at count 15 that loads the next count of 8. Therefore, WCK is a 250 nanosecond pulse every 2.0 microseconds. The CPU interface consists of the chip select decode U98, U51 address A0, A1, function decode FDCCS\*, and IOR\*, IOW\*. The function decode FDCDS\* is separated into the lower four address range for the "DOR" register and into the upper four address range for the FDC; both are inhibited by AEN. The "DOR" latch U71 is for configuration control, drive select, reset, interrupt/DMA request enable, drive motor control, and software transfer terminal count. Latch U106 is used to delay the FDC DMA request (DRQ) as specified by the 765 specification. Counter U50 is used to add pre-compensation to the MFM coded write data (250 nanosecond pulse every 2.0 microseconds maximum). The 765 FDC signals ''early'' and ''late'' determine the number of 8 MHz clock periods (125 nanoseconds) the write data is delayed thru U69 - normal = 6, early = 4, late = 7. Data separator U69 converts "raw data" from the drive into read data (RDD) and read clock (RDW).

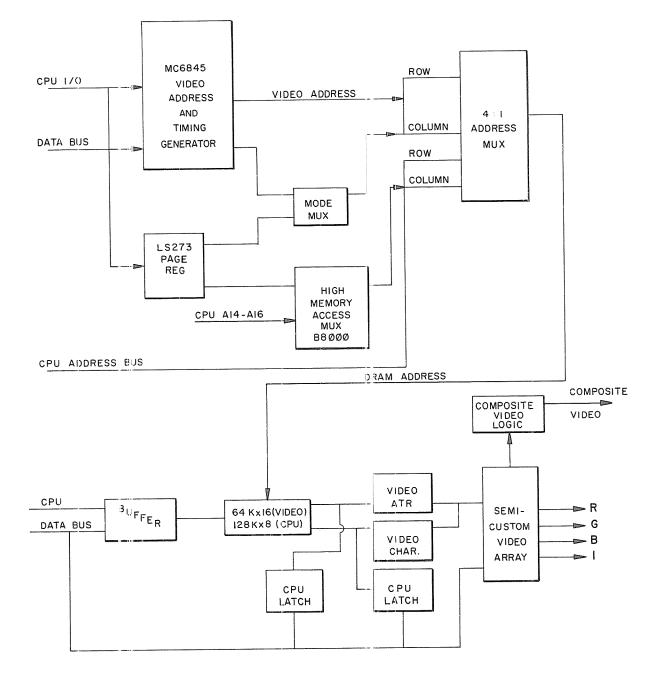

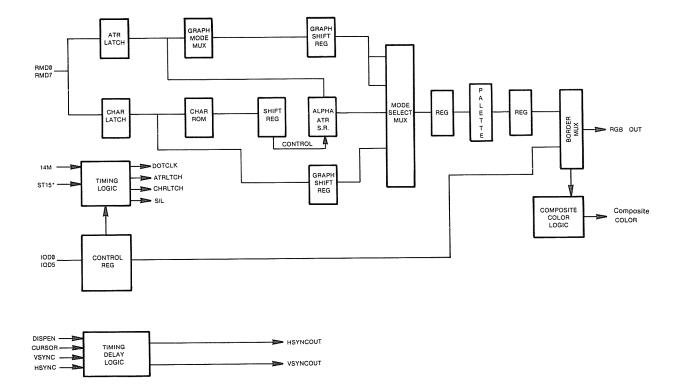

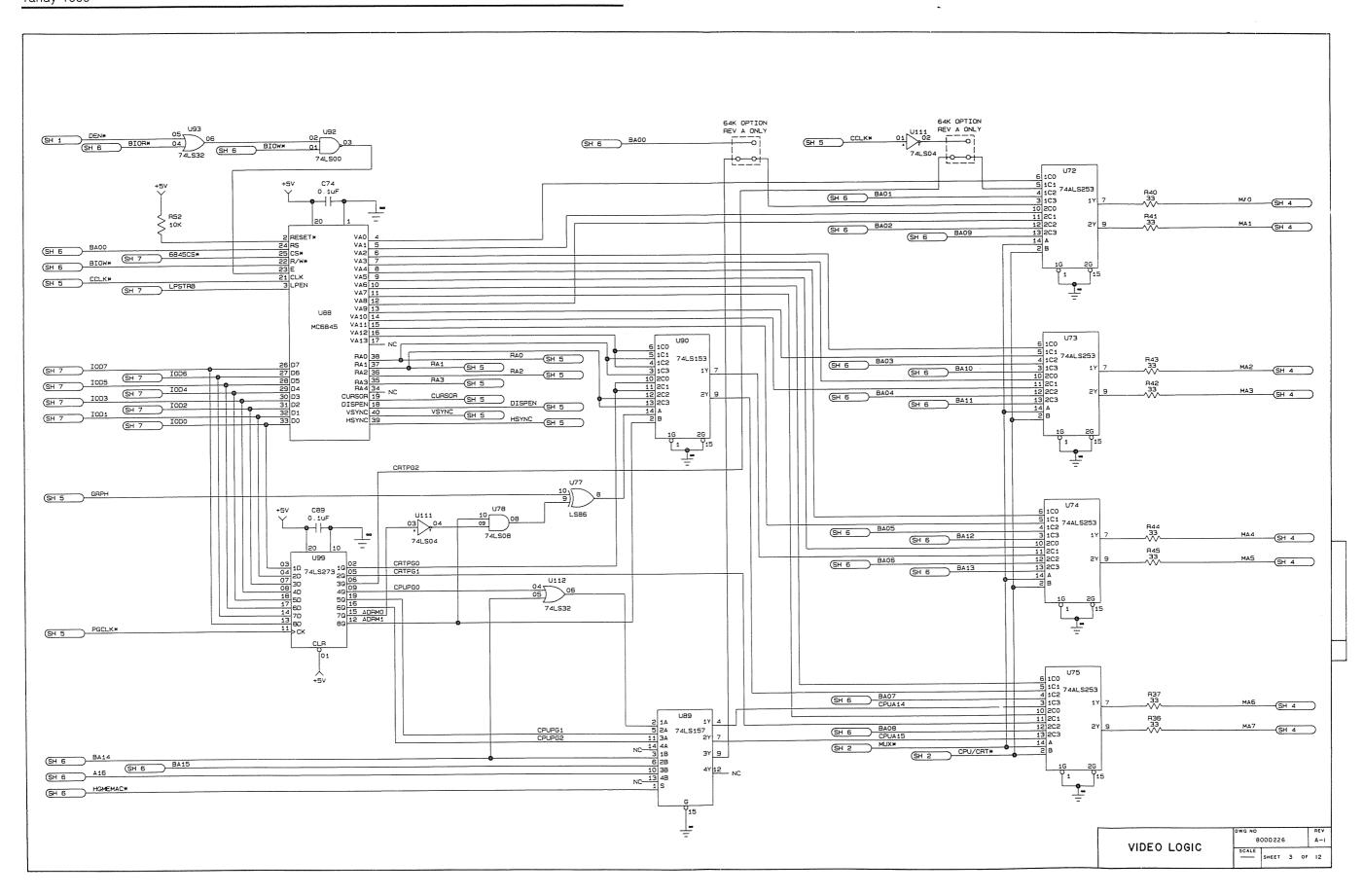

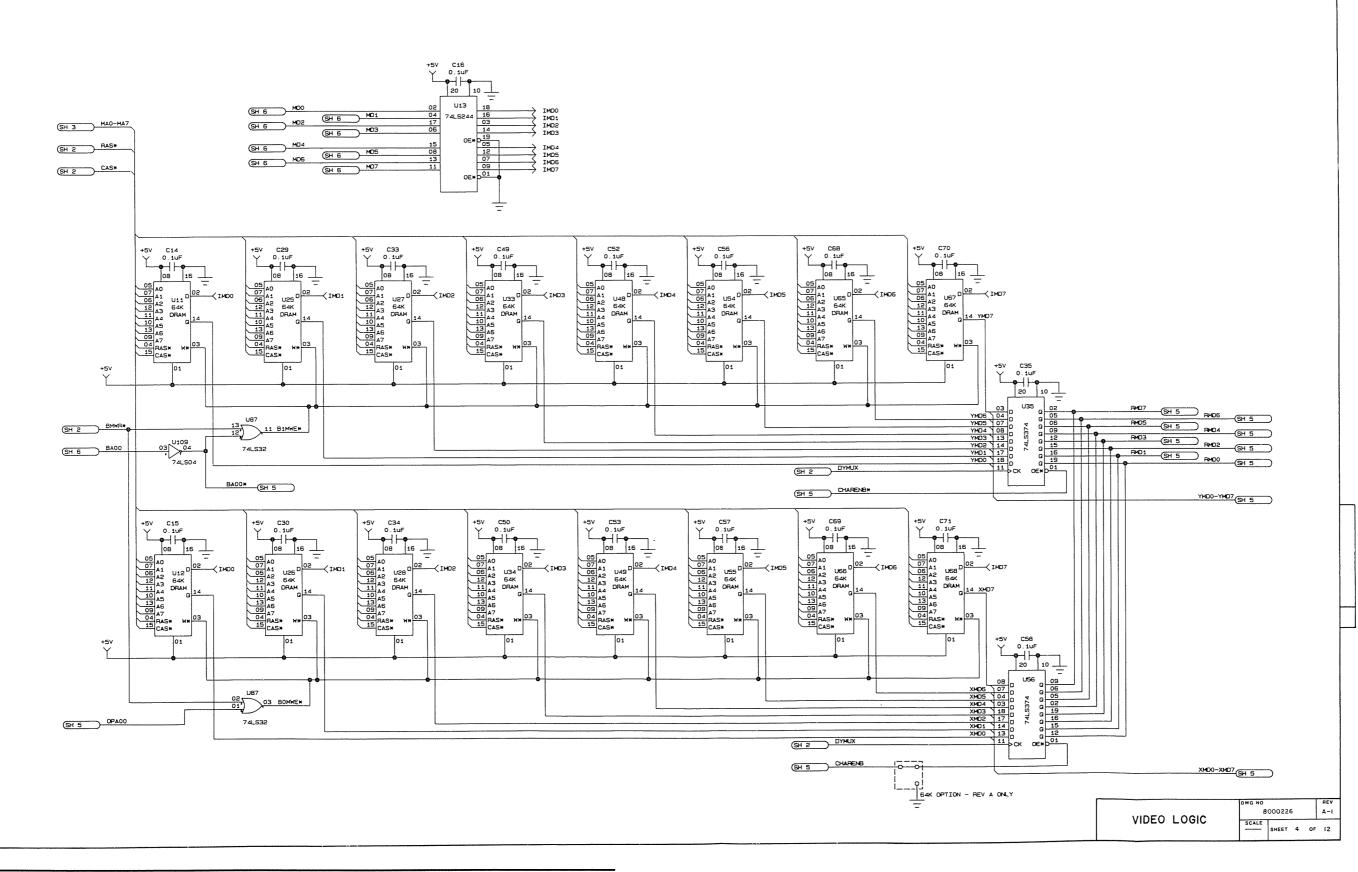

# Introduction to the Video System Logic

The Video System Logic is composed of three functional sections: Video Address Generation, Video Memory, and Video Data Processing.

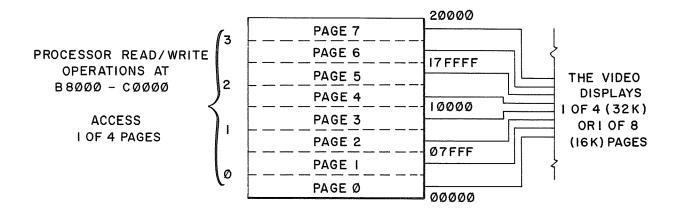

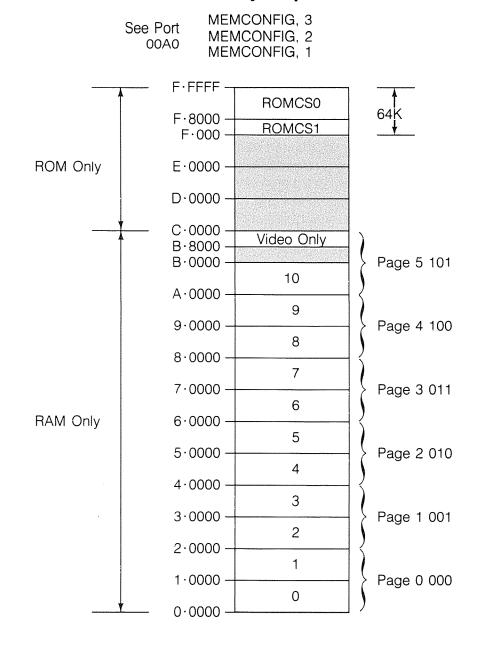

The Video Address Generation logic is composed of the MC6845, one control register U99, and six multiplexers. The MC6845 generates the video addresses and video timing signals for all modes of operation. The control register is used for paging the 128K system memory. The MC6845 has a maximum address range of 32K. Since the Video/System RAM size is 128K, the RAM is divided into 4 pages of 32K each. Selection of the page is determined by the Page Register U99, by the Page Multiplexer U89, U90, and by associated gates. The CPU has the option of addressing the RAM at two different locations, one as 32K window starting at B8000 or as System RAM at an assigned 128K page between 00000 and A0000. The top two bits of the control register U99 are used to select different addressing modes for high resolution graphics. For programming ease, any of the graphics modes requiring only 16K of memory will b∉ automatically selected by the addressing logic. Multiplexers U72 through U75 are used to select either the CPU or the video address and to switch between row and column addresses for the dynamic RAM chips.

The Video Memory is composed of two 8 bit rows of 64k dynamic RAMs (64K x 8 x 2) that is shared by the video and the CPU (8088). The video system sees the memory organized as 64K x 16 bits wide to allow a high video bit rate. See the RAM Timing Chart (page 43) for the RAM specifications. The CPU sees the memory as only 8 bits wide. During any read operation (either CPU or video), both banks of memory are accessed at the same time. The data is latched into U35 and U56 for the video or into U36 and U57 for the CPU. The video uses all 16 bits of memory; however, the CPU expects only 8 bits, and the extra bits are ignored. The CPU selects the 64K x 8 bank using address 00000; so the memory is organized as 128K x 8 to the CPU.

The RAM is located at an address determined by the rr emory configuration control port. In a 128K system that address is normally 00000 — 1FFFF. In ac dition this memory may be accessed at the 32K byte address from B8000 — BFFFF. A page register selects which of the 4 pages are available to the CPU. The CPU access is synchronized to the vicleo so that no adverse effects are observed at any time.

The processor can address any location in memory while the video is using only a 16K or 32K page. This allows one video page to be displayed while another is being changed by the CPU. Therefore, the displayed page can be switched during vertical retrace. A video system memory map is shown on the next page.

VIDEO SYSTEM MEMORY MAP

The third section of the video (Video Data Processing) is composed of only one 40-pin IC. However, a large amount of logic has been compressed into that single HCMOS custom IC. Figure 15 shows a block diagram of the logic. The multiplexed data input from the RAM is divided back into 16 bits of information. For the alphanumeric mode this is character byte and attribute byte data. In alphanumeric mode, the character data is used to address the character ROM. The character ROM output is loaded into a shift register controls the on/off selection of each video dot. The attribute byte defines foreground and background color. In graphics mode, the data bits are first rearranged depending on the mode, and then loaded into the shift register. The mode selection multiplexer selects alpha, 2 color, 4 color medium resolution, 4 color high resolution, or 16 color modes. The output of the mode selection multiplexer clocks the RGBI data before it goes to the palette RAM and then clocks it again after the palette. From this last register, the RGBI data passes through the border color mux and then through the output buffers as RGBI data. The RGB outputs are also used to generate the composite color signal.

The remaining logic of the Video Array consists of the timing logic, the control register logic and the timing delay logic. The timing logic provides the clocks and shift load signals for the latches and the shift registers. The control registers are loaded by the system software and provide the mode selection and color control bits. The timing delay logic synchronizes all the logic. See Figure 16 for the Video Array Block Diagram.

# Main System Board RAM Timing Specification

# **AC Operating Conditions and Characteristics**

| Parameter                                    | Symbol | Min. | Max. | Units |

|----------------------------------------------|--------|------|------|-------|

| Random Read or Write Cycle Time              | tRC    | 279  |      | ns    |

| Read Write Cycle Time                        | tRWC   | 279  |      | ns    |

| Access Time from Row Address<br>Strobe       | tRAC   |      | 200  | ns    |

| Access Time from Column<br>Address           | tCAC   |      | 100  | ns    |

| Output Buffer and Turn-Off Delay             | tOFF   | 0    | 30   | ns    |

| Row Address Strobe Precharge<br>Time         | tRP    | 100  |      | ns    |

| Row Address Strobe Pulse Width               | tRAS1  | 170  |      | ns    |

| Column Address Strobe Pulse<br>Width         | tCAS   | 130  |      | ns    |

| Row Address Setup Time                       | tASR   | 0    |      | ns    |

| Row Address Hold Time                        | tRAH   | 20   |      | ns    |

| Column Address Setup Time                    | tASC   | 0    |      | ns    |

| Column Address Hold Time                     | tCAH   | 35   |      | ns    |

| Transition Time (Rise and Fall)              | tT     |      | 50   | ns    |

| Read Command Setup Time                      | tRCS   | 0    |      | ns    |

| Read Command Hold Time                       | tRCH   | 0    | ·    | ns    |

| Read Command Hold Time<br>Referenced to RAS  | tRRH   | 0    |      | ns    |

| Write Command Hold Time                      | tWCH   | 35   |      | ns    |

| Write Command Hold Time<br>Referenced to RAS | tWCR   | 95   |      | ns    |

| Write Command Pulse Width                    | tWP    | 35   |      | ns    |

| Write Command to Row Strobe<br>Lead Time     | tRWL   | 45   |      | ns    |

| Write Command to Column<br>Strobe Lead Time  | tCWL   | 45   |      | ns    |

| Data in Setup Time                           | tDS    | 0    |      | ns    |

| Data in Hold Time                            | tDH    | 35   |      | ns    |

| Data in Hold Time Referenced to RAS          | tDHR   | 95   |      | ns    |

| Column to Row Strobe<br>Precharge Time       | tCRP   | 0    |      | ns    |

| RAS Hold Time                                | tRSH   | 85   |      | ns    |

| Refresh Period                               | tRFSH  |      | 2.0  | ms    |

| WRITE Command Setup Time                     | tWCS   | 0    |      | ns    |

| CAS to WRITE Delay                           | tCWD   | 45   |      | ns    |

| RAS to WRITE Delay                           | tRWD   | 120  |      | ns    |

| CAS Hold Time                                | tCSH   | 200  |      | ns    |

# VIDEO SYSTEM BLOCK DIAGRAM

VIDEO ARRAY BLOCK DIAGRAM

Figure 16

# Memory Map

# Video System Modes

#### **Display Modes**

The video circuitry is designed to operate with three types of display devices: a standard TV using an optional RF modulator, a composite monitor and an RGBI color monitor. To support these different display types, both a composite video output and a 9-pin RGBI connector are provided.

The video display system is very flexible and can be programmed for a number of video modes. These modes use varying numbers of colors (2, 4, or 16). These 16 colors are defined by combinations of the RGBI as shown in the color chart below and can be used for foreground, background, and character blinking. If you are using a black and white monitor. (These colors will appear as shades of gray for use as reverse video, highlighting, and blinking.) In addition any 1 of the 16 colors or shades of gray can be used for the screen border.

| Color         |   | R | G | В |

|---------------|---|---|---|---|

| Black         | 0 | 0 | 0 | 0 |

| Blue          | 0 | 0 | 0 | 1 |

| Green         | 0 | 0 | 1 | 0 |

| Cyan          | 0 | 0 | 1 | 1 |

| Red           | 0 | 1 | 0 | 0 |

| Magenta       | 0 | 1 | 0 | 1 |

| Brown         | 0 | 1 | 1 | 0 |

| Light Gray    | 0 | 1 | 1 | 1 |

| Dark Gray     | 1 | 0 | 0 | 0 |

| Light Blue    | 1 | 0 | 0 | 1 |

| Light Green   | 1 | 0 | 1 | 0 |

| Light Cyan    | - | 0 | 1 | 1 |

| Pink          | - | 1 | 0 | 0 |

| Light Magenta | - | 1 | 0 | 1 |

| Yellow        | - | 1 | 1 | 0 |

| White         | - | 1 | 1 | 1 |

Available Colors Table

# **Operating Modes**

The operating modes supported by the system software may be grouped into two categories: alphanumeric and graphic.

The alphanumeric mode has two basic types of operation: 80 character by 25 rows and 40 character by 25 rows. In both modes the characters are generated by a 256 character ROM. The character ROM is divided into the following groups:

- 96 Standard ASCII characters

- 48 Block Graphics characters

- 64 Foreign Language/Greek characters

- 16 Special Graphics characters

- 32 Word Processing/Scientific-Notation characters

In both modes all characters are 7 dots wide by 7 dots high and are placed in an 8 dot wide by 8 or 9 dot high matrix.

In both the 40 x 25 mode and the 80 x 25 mode, two bytes of data are used to define each character on the screen. The even address (0,2,4 etc.) is the character code and is used in addressing the character generator ROM. The odd address (1,3,5 etc.) is the attribute byte, that defines the foreground and background color of the character. The following chart shows how the attribute byte functions to control colors.

| ATTRIBUTE BYTE   |             |           |          |           |        |   |       |        |   |

|------------------|-------------|-----------|----------|-----------|--------|---|-------|--------|---|

| BIT              | 7           | 6         | 5        | 4         |        | 3 | 2     | 1      | 0 |

| 3D9 Bit 5        |             | Back      | ground   |           |        |   | Foreg | ground |   |

| = 0              |             | R         | G        | В         |        |   | R     | G      | В |

| 3D9 Bit 5<br>= 1 | Blink       | R         | G        | В         |        | 1 | R     | G      | В |

| Blink = A 1 i    | n bit 7 ena | bles blir | nking of | the foreg | round. |   |       |        |   |

## Graphics Mode

The Video Color/Graphics System can be programmed for a wide variety of modes. The Tandy 1000 and its system ROM BIOS supports the following Graphics Modes:

| Mocle                       | IMB PCjr | IBM PC |

|-----------------------------|----------|--------|

| 4-Color Meclium-Resolution  | X        | X      |

| 16-Color Meclium-Resolution | X        |        |

| 16-Color Low-Resolution     | X        |        |

| 2-Color High-Resolution     | X        | X      |

| 4-Color High Resolution     | X        |        |

Low and medium resolution modes work on all types of display devices. The high-resolution mode may require a monitor for correct operation.

#### Graphics Memory Usage

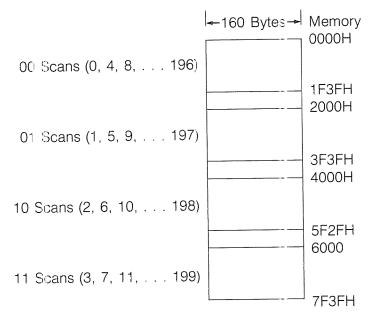

Graphics memory uses either two or four banks of 8000 bytes. In either case pixel information for the display's upper-left corner is found at address 0000. The 4-color high-resolution and 16-color medium-resolution graphics use four banks of 8000 bytes.

The following is a table of the graphics storage organization for four banks of 8000 bytes:

#### **Graphics Storage Organization**

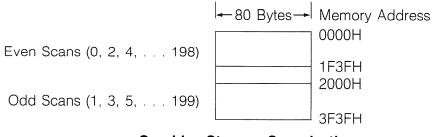

The 2-color high-resolution graphics, the 4-color medium-resolution graphics, and the 16-color low-resolution graphics use only two banks of 8000 bytes.

The following is a table of the graphics storage organization for two banks of 8000 bytes:

**Graphics Storage Organization**

## **High-resolution 2-Color Graphics**

The high-resolution 2-color mode may require a high-resolution monitor for correct operation. This mode can display 2 of 16 possible colors. It contains 200 rows of 640 pixels, requires 16K bytes of read/write memory, and formats 8 pixels per byte. This mode is available in the IBM PC and IBM PCjr

Byte 0 = eighth pixel Byte 1 = seventh pixel Byte 2 = sixth pixel Byte 3 = fifth pixel Byte 4 = fourth pixel Byte 5 = third pixel Byte 6 = second pixel Byte 7 = first pixel

## **High-Resolution 4-Color Graphics**

The high-resolution 4-color mode may require a high-resolution monitor for correct operation. This mode can display 4 out of 16 colors. (Each pixel selects 1 of 4 colors.) It contains 200 rows of 640 pixels, requires 32K bytes of read/write memory and formats 8 pixels per two bytes (1 even-byte and 1 odd-byte). This mode is only supported on the IBM PCjr.

|                       | Even Bytes | Odd Bytes |

|-----------------------|------------|-----------|

| First Display Pixel   | PA0 (7)    | PA1 (7)   |

| Second Display Pixel  | PA0 (6)    | PA1 (6)   |

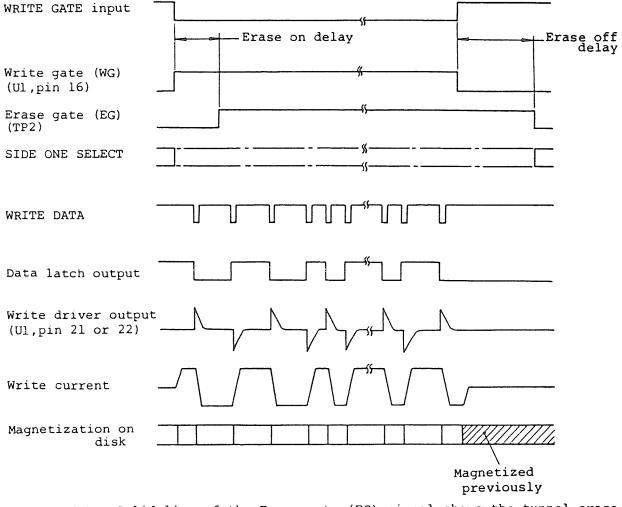

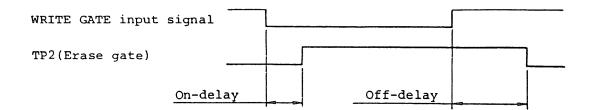

| Third Display Pixel   | PA0 (5)    | PA1 (5)   |