## **Computer Animation**

#### Other McGraw-Hill Titles of Interest

MCGOLDRICHK Video Technology for Personal Computers 0-07-045018-8

RIMMER Windows and OS/2 Bitmapped Graphics 0-07-911902-6

KAY, LEVINE Graphics File Formats, Second Edition 0-07-034025-0

RIMMER Advanced Multimedia Programming 0-07-911898-4

TELLO Multimedia Animation 0-07-063502-1

SZUPROWICZ Multimedia Networking 0-07-063108-5

SANCHEZ, CANTON Numerical Programming the 387, 486, and Pentium 0-07-911832-1

SANCHEZ, CANTON Graphics Programming Solutions 0-07-911464-4

SANCHEZ, CANTON High Resolution Video Graphics 0-07-911645-0

SANCHEZ, CANTON PC Programmer's Handbook, Second Edition 0-07-054948-6

# **Computer Animation**

## **Programming Methods and Techniques**

### **Julio Sanchez**

Montana State University, Northern

Maria P. Canton

Skipanon Software Co.

McGraw-Hill, Inc.

New York San Francisco Washington, D.C. Auckland Bogotá

Caracas Lisbon London Madrid Mexico City Milan

Montreal New Delhi San Juan Singapore

Sydney Tokyo Toronto

#### Library of Congress Cataloging-in-Publication Data

```

Sanchez, Julio, date.

Computer Animation: Programming Methods and Techniques / Julio Sanchez and Maria P. Canton.

Includes index.

ISBN 0-07-054964-8

1. Computer animation. 2. MS-DOS (Computer file) 3. Windows (Computer programs) I. Canton, Maria P. II. Title.

TR897.7.S36 1995

006.6--dc20

94-47025

```

Copyright © 1995 by McGraw-Hill, Inc. All rights reserved. Printed in the United States of America. Except as permitted under the United States Copyright Act of 1976, no part of this publication may be reproduced or distributed in any form or by any means, or stored in a data base or retrieval system, without the prior written permission of the publisher.

1234567890 AGM/AGM 90098765

ISBN 0-07-054964-8

The sponsoring editor for this book was Jerry Papke, the editing supervisor was David E. Fogarty, and the production supervisor was Suzanne W. B. Rapcavage.

Composition and line art by Skipanon Software Co. Printed and bound by Quebecor/Martinsburg.

McGraw-Hill books are available at special quantity discounts to use as premiums and sales promotions, or for use in corporate training programs. For more information, please write to the Director of Special Sales, McGraw-Hill, Inc., 11 West 19th Street, New York, NY 10011. Or contact your local bookstore.

#### LIMITS OF LIABILITY AND DISCLAIMER OF WARRANTY

The author and publisher have exercised care in preparing this book and the programs contained in it. They make no representation, however, that the programs are error-free or suitable for every application to which the reader may attempt to apply them. The author and publisher make no warranty of any kind, expressed or implied, including the warranties of merchantability or fitness for a particular purpose, with regards to these programs or the documentation or theory contained in this book, all of which is provided "as is." The author and publisher shall not be liable for damages in connection with, or arising out of the furnishing, performance, or use of these programs or the associated descriptions or discussions.

Readers should test any program on their own systems and compare results with those presented in this book. They should then construct their own test programs to verify that they fully understand the requisite calling conventions and data formats for each of the programs. Then they should test the specific application thoroughly.

## **Contents**

#### Preface xi

## **Part 1** Animation Fundamentals

| Chapter 1. |        | The Dynamics of Computer Graphics               | 3      |

|------------|--------|-------------------------------------------------|--------|

| 1.0        | Digita | I Simulation of Movement                        | 3      |

| 1.1        | Conve  | entional Animation                              | 4      |

|            | 1.1.1  | Historical Background                           | 4      |

|            |        | Cartoon Animation Techniques                    |        |

|            | 1.1.3  | Photographic Manipulations in Cartoon Animation | 5<br>7 |

| 1.2        | Comp   | uter Animation                                  | 8      |

|            | 1.2.1  | Animating in Real Time                          | 9      |

|            | 1.2.2  | Frame-by-Frame Animation                        | 10     |

|            | 1.2.3  | Interactive Animation                           | 11     |

|            | 1.2.4  | Random or Unpredictable Elements in Animation   | 11     |

| 1.3        | Motio  | n Control Techniques                            | 12     |

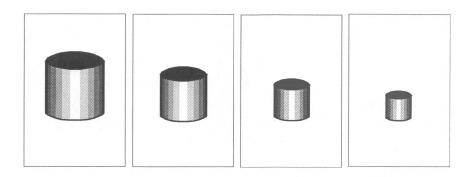

|            | 1.3.1  | Tweening and Morphing                           | 12     |

|            | 1.3.2  | Path-of-Motion Calculations                     | 13     |

|            | 1.3.3  | Color-Shift Animation                           | 15     |

|            | 1.3.4  | Object Rendering                                | 15     |

| 1.4        | Applic | cations of Computer Animation                   | 18     |

|            | 1.4.1  | Simulators and Trainers                         | 19     |

|            | 1.4.2  | Electronic Games                                | 19     |

|            |        | Business Presentations and Marketing            | 20     |

|            |        | Artificial Life                                 | 20     |

|            |        | Virtual Reality                                 | 21     |

|            |        | Fractal Graphics                                | 21     |

| 1.5        | The A  | nimator's Predicament                           | 23     |

| Chapter 2. |        | Graphical Image Structures                      | 25     |

| 2.0        | Image  | Storage for Animation                           | 25     |

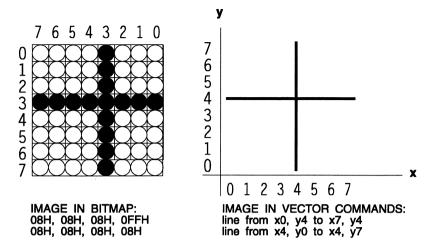

|            | 2.0.1  | Pixel Maps versus Vector Commands               | 25     |

| 2.1        | Devic  | e-Independent Graphics                          | 27     |

|            | 2.1.1  | Software Environment for PC Animation           | 28     |

| 2.2        |        | ual Graphics Machine                            | 29     |

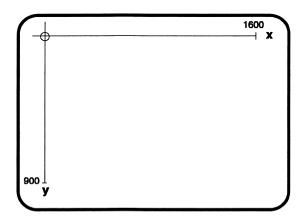

|            |        | The Virtual Graphics Device                     | 30     |

|            |        | The Graphics Primitives                         | 31     |

|            |        | Input Functions                                 | 32     |

|            |        | Display File Structure                          | 32     |

|            |        | Image Data in the Display File                  | 33     |

|            | 2.2.6  | Display File Commands                           | 34     |

vi Contents

| 2.3                                     | Graphics Software Standards                             | 35       |

|-----------------------------------------|---------------------------------------------------------|----------|

|                                         | 2.3.1 Graphics Support from System Software             | 35       |

| 2.4                                     | Storage of the Graphical Image                          | 36       |

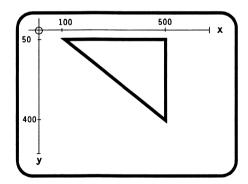

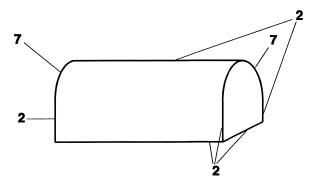

|                                         | 2.4.1 Geometrical Image Elements                        | 36       |

|                                         | 2.4.2 Nongeometrical Image Elements                     | 40       |

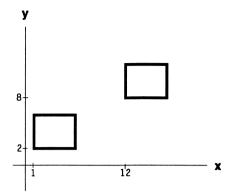

| 2.5                                     | Image Mapping                                           | 40       |

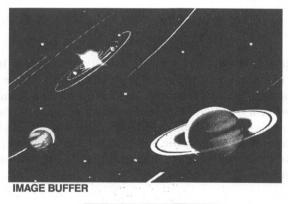

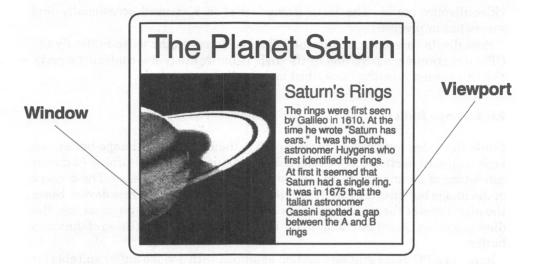

|                                         | 2.5.1 Video Buffer                                      | 40       |

|                                         | 2.5.2 Image Buffer                                      | 41       |

|                                         | 2.5.3 Viewport                                          | 42       |

|                                         | 2.5.4 Window                                            | 42       |

|                                         | 2.5.5 Graphics Modeling                                 | 42       |

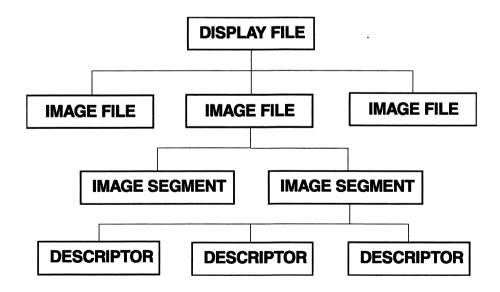

| 2.6                                     | The Display File                                        | 44       |

|                                         | 2.6.1 Image File                                        | 45       |

|                                         | 2.6.2 Image Segments                                    | 46       |

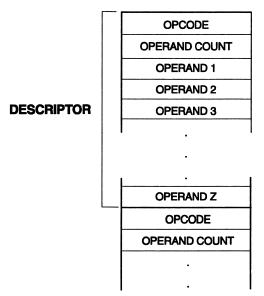

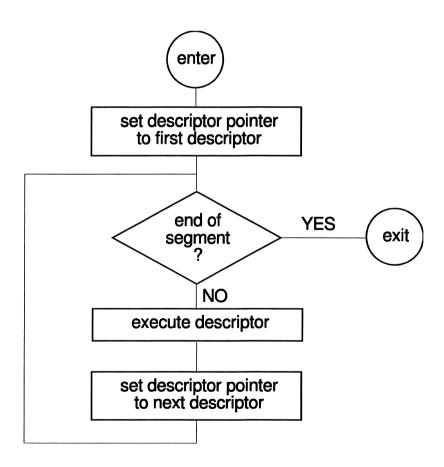

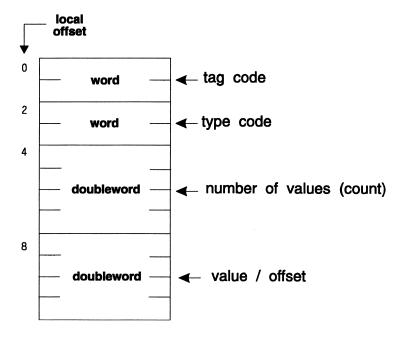

|                                         | 2.6.3 Image Descriptors                                 | 46       |

| Chapt                                   | ter 3. Operations on Geometrical Images                 | 49       |

| 20                                      | Operations on Segments                                  | 49       |

| 3.0                                     | Operations on Segments 3.0.1 Creating the Segment       | 49       |

|                                         | 3.0.2 Opening and Closing the Segment                   | 48<br>50 |

|                                         | 3.0.3 Renaming and Deleting the Segment                 | 50       |

| 21                                      | Segment Attributes                                      | 50       |

| 3.1                                     | 3.1.1 Visibility Attribute                              | 51       |

|                                         | 3.1.2 Line Color, Fill Color, and Line Style            | 51       |

|                                         | 3.1.3 Foreground Priority                               | 52       |

| 32                                      | Graphical Data Structures                               | 52       |

| 0.2                                     | 3.2.1 Display File Elements                             | 53       |

| 3.3                                     | Image Transformations                                   | 58       |

| 0.0                                     | 3.3.1 The Coordinates Matrix                            | 59       |

| 3.4                                     | Matrix Arithmetic                                       | 60       |

| • • • • • • • • • • • • • • • • • • • • | 3.4.1 Scalar-by-Matrix Operations                       | 61       |

|                                         | 3.4.2 Matrix Addition and Subtraction                   | 61       |

|                                         | 3.4.3 Matrix Multiplication                             | 61       |

| 3.5                                     | •                                                       | 63       |

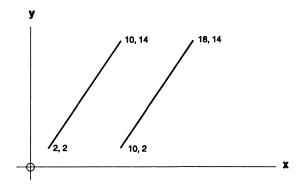

| 0.0                                     | 3.5.1 Translation                                       | 63       |

|                                         | 3.5.2 Scaling                                           | 64       |

|                                         | 3.5.3 Rotation                                          | 66       |

|                                         | 3.5.4 Homogeneous Coordinates                           | 68       |

|                                         | 3.5.5 Concatenation                                     | 70       |

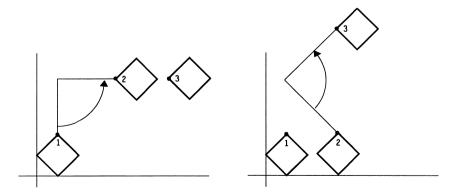

| 3.6                                     | Image Transformations in Animation                      | 72       |

|                                         | 3.6.1 Translation, Rotation, and Scaling Animation      | 72       |

|                                         | 3.6.2 Complex Animation                                 | 73       |

| Chapt                                   | er 4. Bitmap Image Acquisition and Encoding             | 75       |

| 40                                      |                                                         | 75       |

| 4.0                                     | Pixel-Coded Image Data 4.0.1 Raw Image Data             | 75<br>76 |

|                                         | 4.0.1 Haw image Data 4.0.2 Monochrome and Color Bitmaps | 76<br>77 |

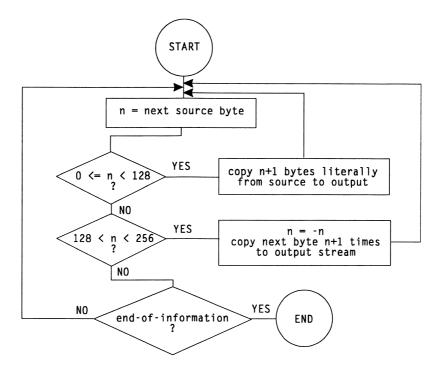

|                                         | 4.0.3 Image Data Compression                            |          |

|                                         | 4.0.4 Encoders and Decoders                             | 78<br>81 |

| 4.1                                     | The GIF Format                                          | 81       |

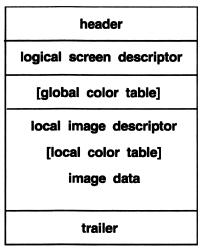

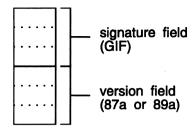

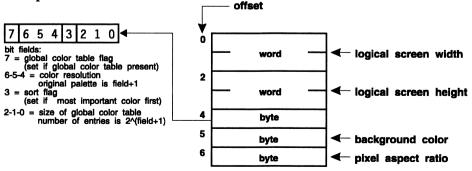

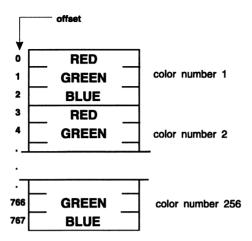

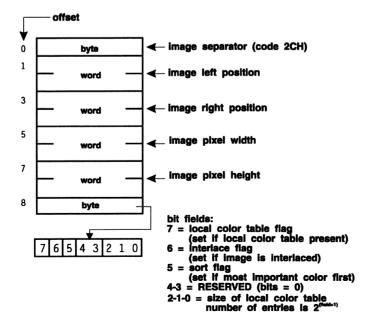

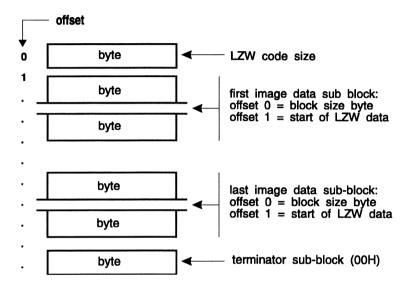

| ₩. 1                                    | 4.1.1 GIF File Structure                                | 82       |

| 4.2                                     | The TIFF Format                                         | 88       |

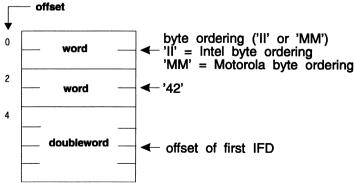

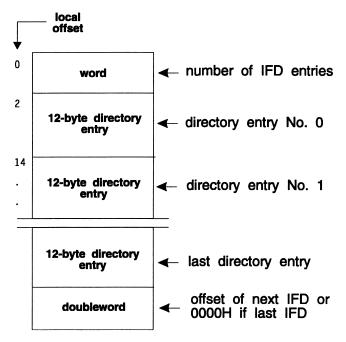

| 4.2                                     | 4.2.1 TIFF File Structure                               | 89       |

|                                         | 4.2.2 TIFF Tags for Bilevel Images                      | 93       |

|                                         |                                                         |          |

Contents

|      | 4.2.3 Locating TIFF Image Data           | 96  |

|------|------------------------------------------|-----|

|      | 4.2.4 Processing TIFF Image Data         | 96  |

|      | 4.2.5 TIFF Software                      | 98  |

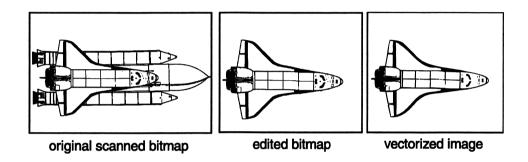

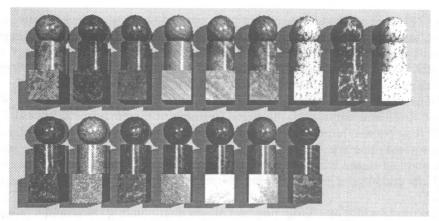

| 4.3  | Bitmap Image Acquisition                 | 109 |

|      | 4.3.1 Legal Considerations               | 110 |

| Part | 2 Animation Programming                  |     |

| Chap | ter 5. Animation in VGA Graphics         | 115 |

| 5.0  | The VGA Standard                         | 115 |

|      | 5.0.1 VGA Characteristics                | 116 |

|      | 5.0.2 VGA Standard Modes                 | 116 |

|      | 5.0.3 VGA Nonstandard Modes              | 117 |

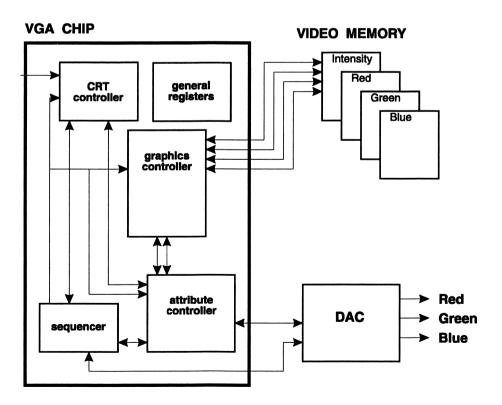

| 5.1  | VGA Architecture                         | 118 |

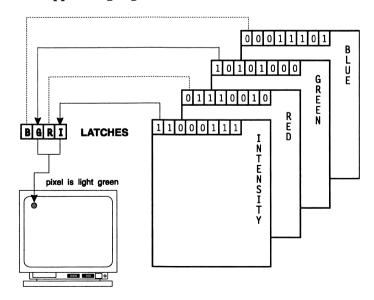

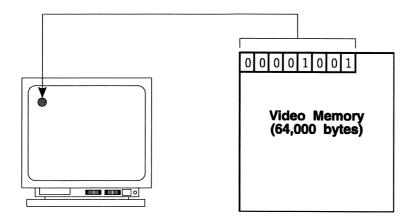

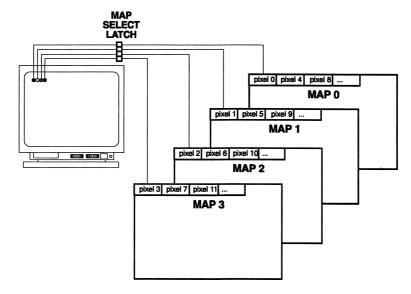

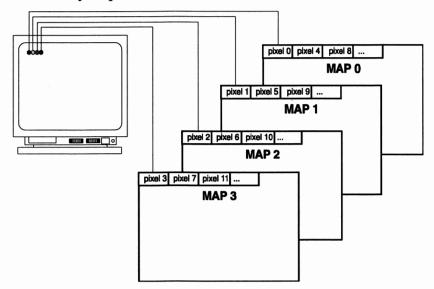

|      | 5.1.1 Video Memory                       | 119 |

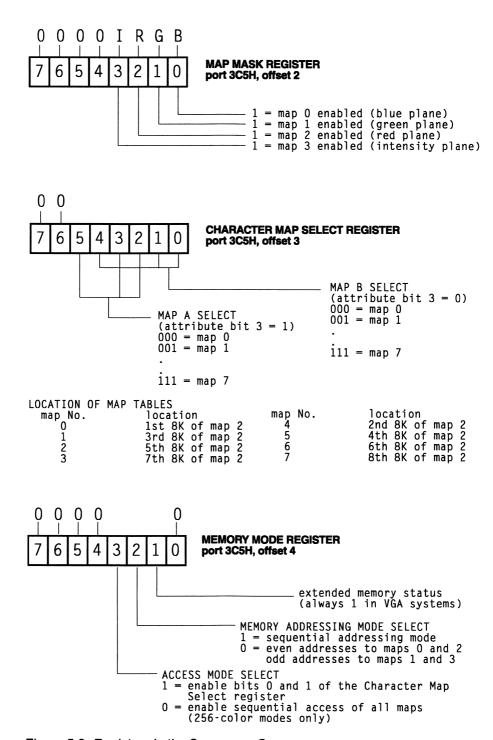

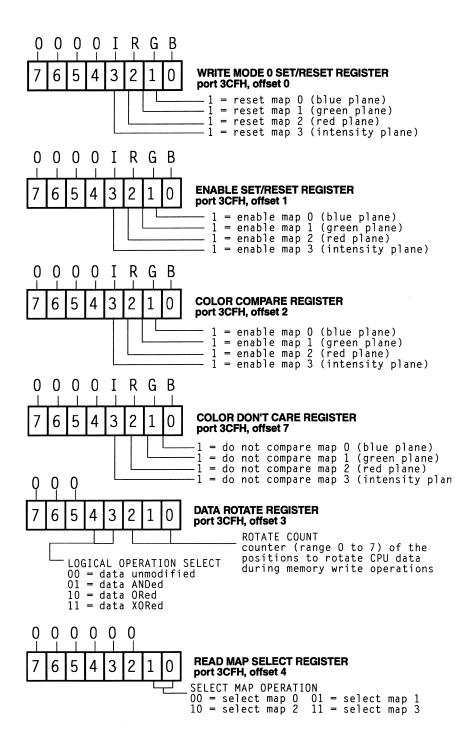

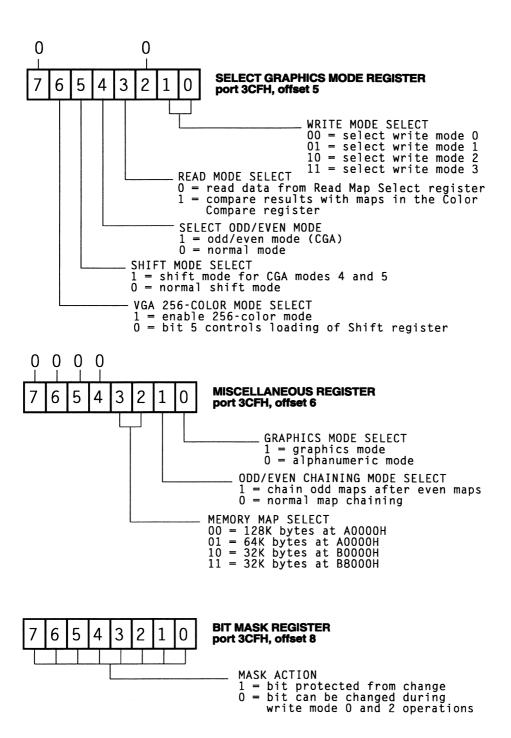

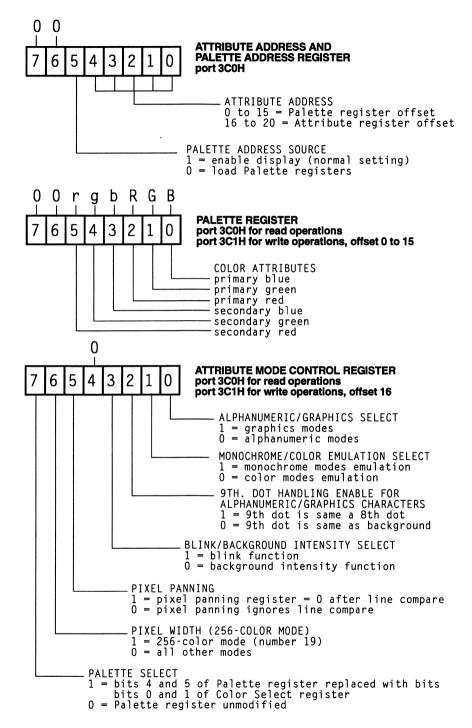

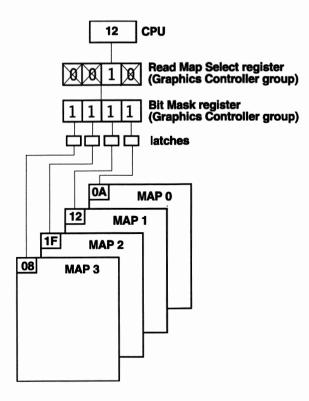

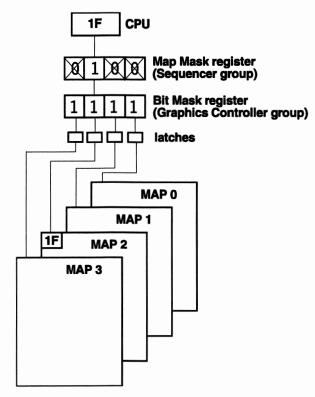

| 5.2  | The VGA Registers                        | 122 |

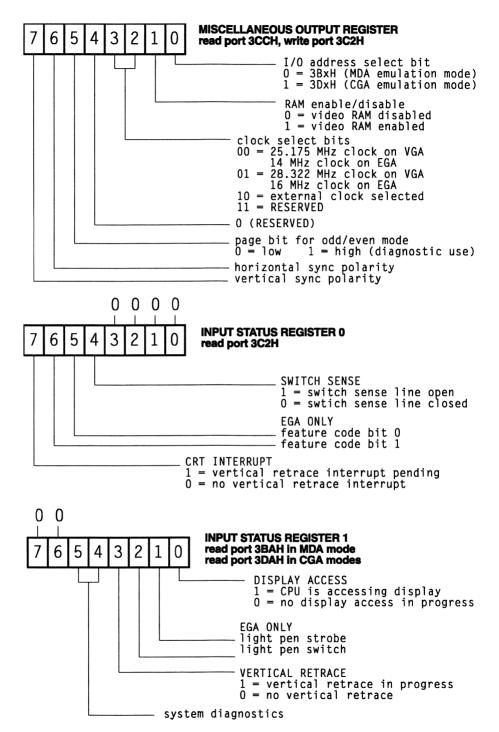

|      | 5.2.1 VGA General Registers              | 123 |

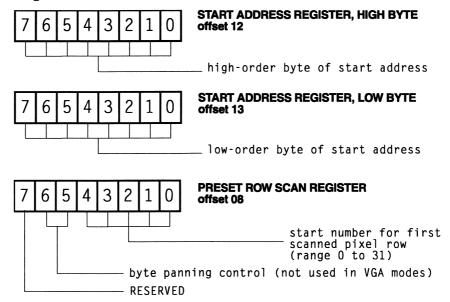

|      | 5.2.2 VGA CRT Controller                 | 125 |

|      | 5.2.3 VGA Sequencer                      | 127 |

|      | 5.2.4 VGA Graphics Controller            | 129 |

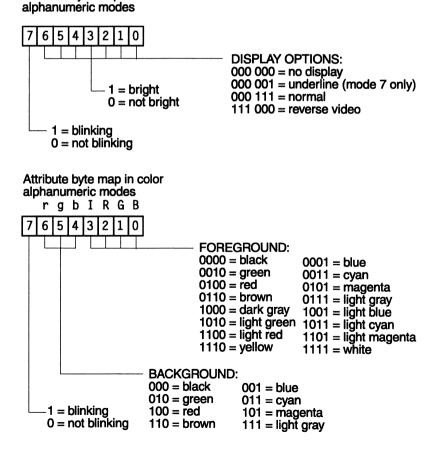

|      | 5.2.5 VGA Attribute Controller           | 137 |

| 5.3  | VGA Digital-to-Analog Converter (DAC)    | 142 |

| Chap | ter 6. VGA Drivers for Standard Modes    | 145 |

| 6.0  | VGA Device Drivers                       | 145 |

|      | 6.0.1 Standard Mode VGA Device Drivers   | 145 |

| 6.1  | VGA Programming Levels                   | 146 |

| 6.2  | Device Drivers and Primitives            | 146 |

|      | 6.2.1 VGA Device Drivers                 | 147 |

|      | 6.2.2 VGA Mode 18 Pixel Write Routines   | 149 |

|      | 6.2.3 VGA Mode 18 Pixel Read Routine     | 159 |

|      | 6.2.4 VGA Mode 19 Pixel Write Routines   | 161 |

|      | 6.2.5 VGA Mode 19 Pixel Read Routine     | 163 |

| 6.3  | Color Operations                         | 163 |

|      | 6.3.1 256-Color Modes                    | 164 |

|      | 6.3.2 16-Color Modes                     | 178 |

| 6.4  | Color Animation                          | 179 |

| Chap | ter 7. VGA Mode X Drivers and Primitives | 181 |

| 7.0  | A Nonstandard VGA Mode                   | 181 |

|      | 7.0.1 Mode X Characteristics             | 182 |

|      | 7.0.2 Mode X in Animation Programming    | 182 |

| 7.1  |                                          | 184 |

|      | 7.1.1 Pixel-Level Address Calculations   | 187 |

|      | 7.1.2 Tile-Level Address Calculations    | 189 |

|      | 7.1.3 The Video Buffer in Mode X         | 191 |

| 7.2  | Setting Mode X                           | 192 |

| 7.3  | Pixel-Level Device Drivers               | 195 |

|      | 7.3.1 VGA Mode X Write Pixel Procedure   | 195 |

|      | 7.3.2 VGA Mode X Read Pixel Procedure    | 197 |

| 7.4  | Tile-Level Device Drivers                | 198 |

|      | 7 / 1 VCA Mode Y Write Tile Procedure    | 100 |

viii Contents

|         | 7.4.2 Setting Multiple Tiles                          | 200 |

|---------|-------------------------------------------------------|-----|

| 7.5     | VGA Mode X Bitmap Primitives                          | 201 |

|         | 7.5.1 Pixel Transparency                              | 202 |

|         | 7.5.2 VGA Mode X Bitmap Display                       | 203 |

|         | 7.5.3 VGA Mode X Bitmap Acquisition                   | 207 |

| 7.6     | VGA Mode X BitBit Primitives                          | 210 |

|         | 7.6.1 Page-Level BitBit                               | 210 |

|         | 7.6.2 Tile-Level BitBit                               | 213 |

| 7.7     | Mode X Animation                                      | 216 |

| • • • • | 7.7.1 Intercepting the Vertical Retrace               | 216 |

|         | 7.7.2 Interval Timing                                 | 217 |

|         | 7.7.3 Video Paging in VGA Mode X                      | 219 |

|         | 7.7.4 VGA Mode X Panning Animation                    | 218 |

|         | 7.7.4 VGA Mode A Faining Ammation                     | 220 |

| Chapt   | ter 8. XGA Architecture and Initialization            | 223 |

| 8.0     | The IBM Extended Graphics Array Video System (XGA)    | 223 |

|         | 8.0.1 Technical Description                           | 225 |

|         | 8.0.2 XGA in VGA Modes                                | 225 |

|         | 8.0.3 Multiple XGA Systems                            | 225 |

|         | 8.0.4 XGA Extended Graphics Modes                     | 226 |

|         | 8.0.5 Alphanumeric Support                            | 227 |

|         | 8.0.6 The Adapter Interface                           | 227 |

|         | 8.0.7 Multidisplay Graphics Systems                   | 227 |

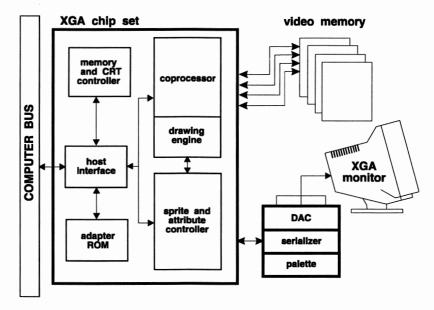

| 0.1     | XGA Architecture                                      | 228 |

| 0.1     | 8.1.1 XGA CRT Controller                              | 228 |

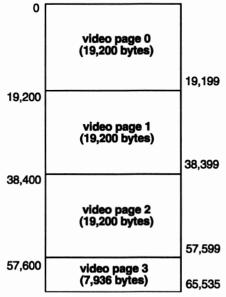

|         | 8.1.2 XGA Video Buffer                                | 229 |

|         | 8.1.3 The Serializer/Palette/Digital-Analog Converter | 229 |

|         | 8.1.4 The XGA Sprite/Attribute Controller             | 230 |

|         |                                                       |     |

| 8.2     | Access and Control of the XGA System                  | 231 |

|         | 8.2.1 Access to the XGA Graphics Coprocessor          | 232 |

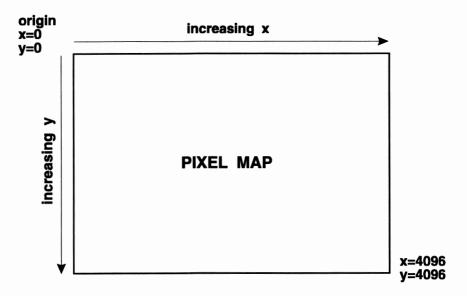

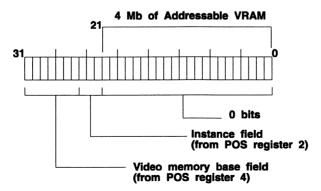

| 8.3     | XGA Video Memory                                      | 233 |

|         | 8.3.1 Video Memory Apertures                          | 233 |

|         | 8.3.2 Data Ordering                                   | 234 |

| 8.4     | XGA Detection and Initialization                      | 234 |

|         | 8.4.1 Programming the XGA Display Controller          | 235 |

|         | 8.4.2 XGA Hardware Initialization                     | 236 |

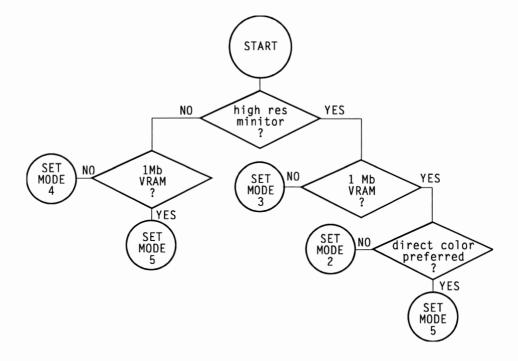

|         | 8.4.3 XGA Mode Selection and Setting                  | 253 |

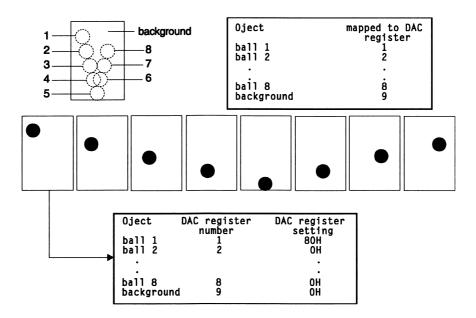

|         | 8.4.4 The XGA Palette                                 | 260 |

|         | 8.4.5 Switching from XGA to VGA Modes                 | 272 |

| 8.5     | Other Methods of XGA Initialization                   | 276 |

| Chapt   | ter 9. XGA Drivers and Primitives                     | 279 |

| •       |                                                       |     |

|         | XGA Hardware Programming                              | 279 |

| 9.1     | Accessing XGA Video Memory                            | 280 |

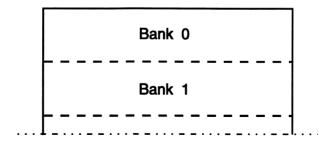

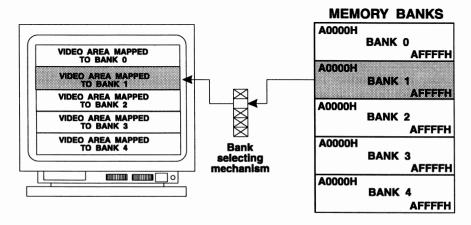

|         | 9.1.1 XGA Memory Banks                                | 280 |

|         | 9.1.2 Setting a Pixel                                 | 281 |

|         | 9.1.3 Clearing the XGA Screen                         | 282 |

|         | 9.1.4 Reading a Pixel                                 | 284 |

| 9.2     |                                                       | 285 |

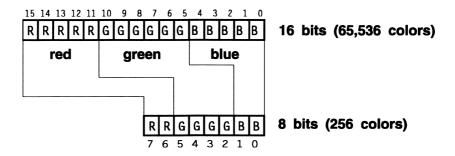

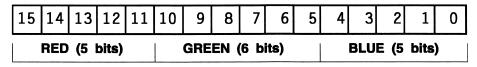

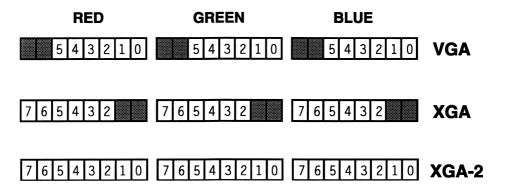

|         | 9.2.1 The Direct Color Palette                        | 286 |

|         | 9.2.2 Pixel Setting in Direct Color Mode              | 288 |

|         | 9.2.3 16-Bit Color Adjustments                        | 290 |

| 9.3     | XGA Graphics Coprocessor Architecture                 | 292 |

| 9.4     | Initializing the Coprocessor                          | 293 |

|         | 9.4.1 Obtaining the Coprocessor Base Address          | 293 |

|         | 9.4.2 Obtaining the Video Memory Address              | 295 |

Contents

|      | 9.4.3    | Selecting the Access Mode                  | 296 |

|------|----------|--------------------------------------------|-----|

|      | 9.4.4    | Initializing Coprocessor Registers         | 297 |

| 9.   | 5 Progra | amming Coprocessor Operations              | 298 |

|      |          | Synchronizing Coprocessor Access           | 298 |

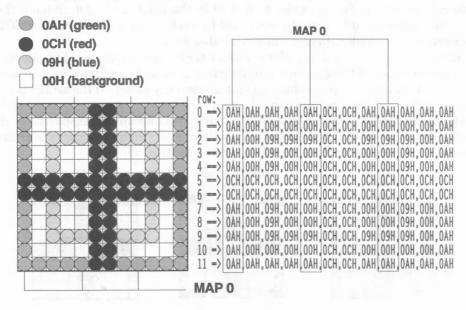

|      |          | General Purpose Maps A, B, and C           | 299 |

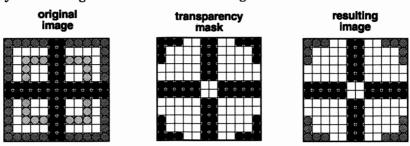

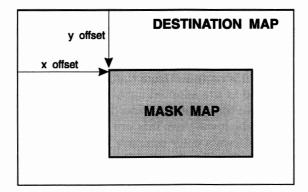

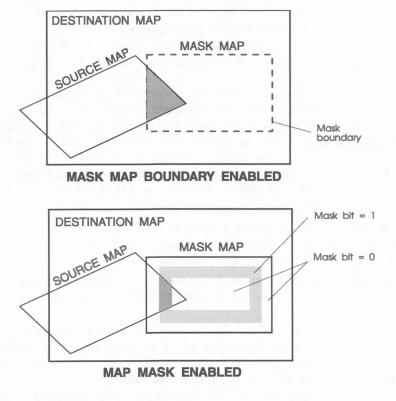

|      |          | The Mask Map                               | 301 |

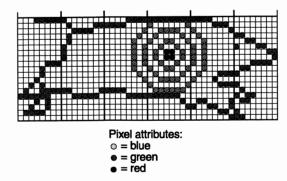

|      |          | Pixel Attributes                           | 303 |

|      |          | Pixel Masking and Color Compare Operations | 304 |

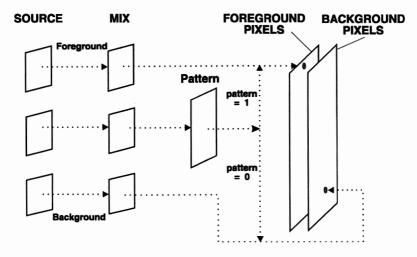

|      |          | Mixes                                      | 304 |

|      |          | Pixel Operations                           | 304 |

| 9.0  |          | PixBit Operations                          | 306 |

|      |          | Rectangular Fill PixBit                    | 306 |

|      |          | System Memory to Video Memory PixBits      | 309 |

|      |          | Pattern Map BitBit                         | 313 |

| 9.   |          | Drawing Operations                         | 317 |

|      |          | Reduction to the First Octant              | 317 |

|      |          | Calculating the Bresenham Terms            | 318 |

| 9.   |          | amming The XGA Sprite                      | 321 |

|      |          | The Sprite Image                           | 323 |

|      |          | Sprite Colors and Attributes               | 324 |

|      |          | Loading the Sprite                         | 324 |

|      | 9.8.4    | Sprite Manipulations                       | 328 |

| Cha  | pter 10. | . SuperVGA Graphics and Animation          | 331 |

|      | ).0 Supe |                                            | 331 |

| - 10 |          | SuperVGA in Animation Programming          | 332 |

| 10   |          | rVGA Memory Architecture                   | 332 |

| 10   | •        | SuperVGA Memory Banking                    | 333 |

|      |          | 2 SuperVGA 256-Color Extensions            | 334 |

|      |          | SuperVGA Pixel Addressing                  | 335 |

| 10   |          | rVGA Architecture                          | 335 |

|      |          | The VESA SuperVGA Standard                 | 335 |

|      |          | 2 VESA SuperVGA Modes                      | 335 |

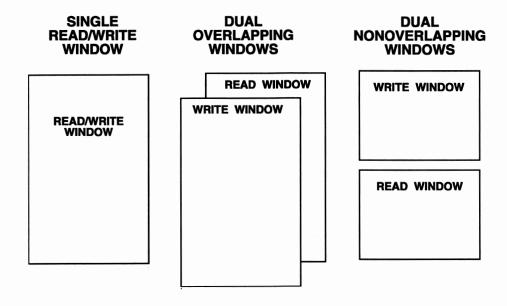

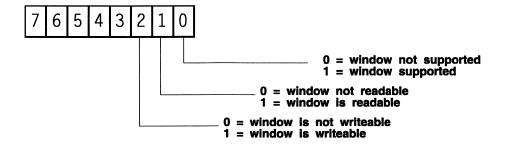

|      |          | B Memory Windows                           | 336 |

| 10   |          | /ESA BIOS                                  | 338 |

|      |          | Subservice 0 — System Information          | 339 |

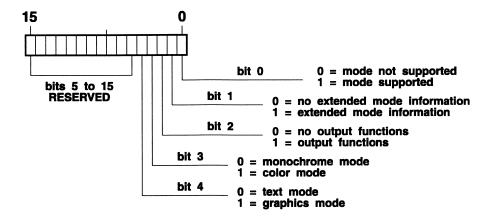

|      |          | 2 Subservice 1 — Mode Information          | 343 |

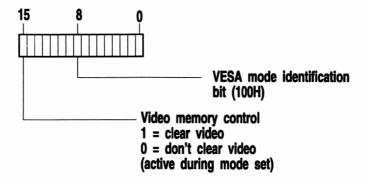

|      |          | S Subservice 2 — Set Video Mode            | 345 |

|      |          | Subservice 3 — Get Video Mode              | 346 |

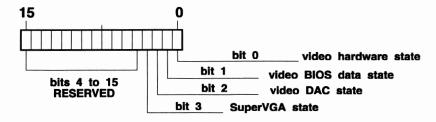

|      |          | Subservice 4 — Save/Restore Video State    | 347 |

|      |          | S Subservice 5 — Switch Bank               | 348 |

|      |          | Subservice 6 — Set/Get Logical Scan Line   | 349 |

|      | 10.3.8   | Subservice 7 — Set/Get Display Start       | 349 |

|      |          | Subservice 8 — Set/Get DAC Palette Control | 349 |

| 10   |          | rVGA Device Drivers                        | 349 |

|      |          | Address Calculations                       | 350 |

|      | 10.4.2   | Pank Switching Operations                  | 351 |

| 10   | .5 Super | rVGA Pixel Level Operations                | 352 |

|      | 10.5.1   | SuperVGA Pixel Write                       | 353 |

|      | 10.5.2   | 2 SuperVGA Pixel Read                      | 354 |

|      | 10.5.3   | Clearing the SuperVGA Screen               | 356 |

|      |          |                                            |     |

## Part 3 Animation Techniques

x Contents

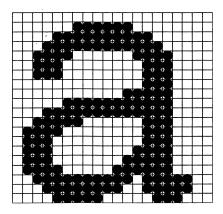

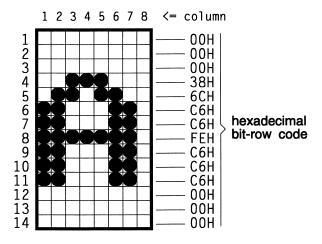

| 11.1   | Background Techniques Bitmap Backgrounds 11.1.1 Hand Bit-coding a Bitmap Background 11.1.2 Electronic Drawing Methods 11.1.3 Ray-tracing a Bitmap Background 11.1.4 Scanning a Bitmap Background 11.1.5 Multiple Image Manipulations Vectorized Background 11.2.1 Vector/Bitmap Background Operations on Text 11.3.1 Text Display Operations in BIOS 11.3.2 Developing a Character Generator 11.3.3 Text Animation | 361<br>361<br>362<br>362<br>364<br>364<br>366<br>386<br>387<br>390 |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Chapte | er 12. Time-Pulse and Color-Shift Techniques                                                                                                                                                                                                                                                                                                                                                                       | 399                                                                |

| 12.0   | The Animated Image Set                                                                                                                                                                                                                                                                                                                                                                                             | 399                                                                |

|        | 12.0.1 Visual Retention                                                                                                                                                                                                                                                                                                                                                                                            | 399                                                                |

|        | 12.0.2 Avoiding Interference                                                                                                                                                                                                                                                                                                                                                                                       | 400                                                                |

| 12.1   | XOR Animation                                                                                                                                                                                                                                                                                                                                                                                                      | 401                                                                |

|        | 12.1.1 Programming the Function Select Bits                                                                                                                                                                                                                                                                                                                                                                        | 403                                                                |

| 12.2   | Generating the Time Pulse                                                                                                                                                                                                                                                                                                                                                                                          | 404                                                                |

|        | 12.2.1 Looping Techniques                                                                                                                                                                                                                                                                                                                                                                                          | 404                                                                |

|        | 12.2.2 Reprogramming the System Timer                                                                                                                                                                                                                                                                                                                                                                              | 405                                                                |

|        | 12.2.3 Turning the Video Function On and Off                                                                                                                                                                                                                                                                                                                                                                       | 409                                                                |

|        | 12.2.4 Retrace Cycle Timing                                                                                                                                                                                                                                                                                                                                                                                        | 410                                                                |

|        | 12.2.5 VGA Vertical Retrace Interrupt                                                                                                                                                                                                                                                                                                                                                                              | 411                                                                |

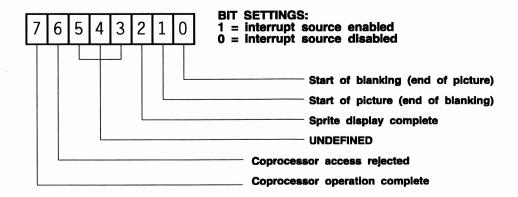

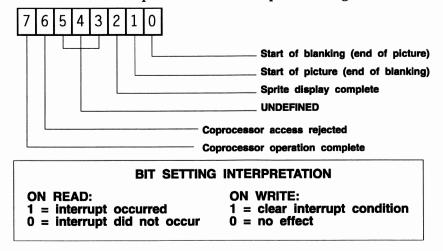

| 40.0   | 12.2.6 XGA Screen Blanking Interrupt                                                                                                                                                                                                                                                                                                                                                                               | 417                                                                |

| 12.3   | Color-Shift Animation                                                                                                                                                                                                                                                                                                                                                                                              | 422                                                                |

|        | 12.3.1 VGA DAC Primitives                                                                                                                                                                                                                                                                                                                                                                                          | 423                                                                |

|        | 12.3.2 Transformations by Color Shift                                                                                                                                                                                                                                                                                                                                                                              | 427                                                                |

|        | 12.3.3 Color-Shift Fade-Out                                                                                                                                                                                                                                                                                                                                                                                        | 429<br>431                                                         |

|        | 12.3.4 Color-Shift Fade-In                                                                                                                                                                                                                                                                                                                                                                                         | 431                                                                |

| Chapte | er 13. Interactive Animation                                                                                                                                                                                                                                                                                                                                                                                       | 435                                                                |

| 13.0   | User-Animated Objects                                                                                                                                                                                                                                                                                                                                                                                              | 435                                                                |

| 13.1   | PC Keyboard Hardware                                                                                                                                                                                                                                                                                                                                                                                               | 435                                                                |

|        | 13.1.1 Keyboard Controller                                                                                                                                                                                                                                                                                                                                                                                         | 436                                                                |

|        | 13.1.2 The Keyboard Scan Codes                                                                                                                                                                                                                                                                                                                                                                                     | 436                                                                |

| 13.2   | Keyboard Programming                                                                                                                                                                                                                                                                                                                                                                                               | 436                                                                |

|        | 13.2.1 Classification of Keys and Keystrokes                                                                                                                                                                                                                                                                                                                                                                       | 437                                                                |

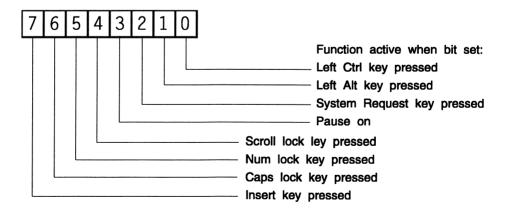

|        | 13.2.2 Keyboard Data in BIOS                                                                                                                                                                                                                                                                                                                                                                                       | 440                                                                |

|        | 13.2.3 Keyboard Status Bytes                                                                                                                                                                                                                                                                                                                                                                                       | 441                                                                |

|        | 13.2.4 Keyboard Buffers                                                                                                                                                                                                                                                                                                                                                                                            | 441                                                                |

| 13.3   | Programming the Mouse                                                                                                                                                                                                                                                                                                                                                                                              | 442                                                                |

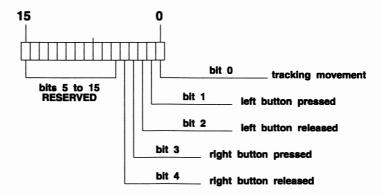

|        | 13.3.1 The Microsoft Mouse Interface                                                                                                                                                                                                                                                                                                                                                                               | 442<br>443                                                         |

|        | 13.3.2 Checking Mouse Installation 13.3.3 Subservices of Interrupt 33H                                                                                                                                                                                                                                                                                                                                             | 443<br>443                                                         |

| 10 4   | Cursor in VGA Graphics Mode                                                                                                                                                                                                                                                                                                                                                                                        | 443<br>450                                                         |

| 13.4   | 13.4.1 Intercepting the System Timer Interrupt                                                                                                                                                                                                                                                                                                                                                                     | 450<br>450                                                         |

|        | 13.4.2 The Timer Interrupt Handler                                                                                                                                                                                                                                                                                                                                                                                 | 451                                                                |

|        | 13.4.3 Keyboard Input Routine                                                                                                                                                                                                                                                                                                                                                                                      | 453                                                                |

|        | ionio itopouta input itoutino                                                                                                                                                                                                                                                                                                                                                                                      | 700                                                                |

Bibliography 459 Index 463

## **Preface**

This book is a presentation of practical methods and techniques for animation programming on the personal computer. It includes code samples of the fundamental device drivers and primitives for VGA, SuperVGA, and XGA video systems. It is also a tutorial on low-level animation programming which can be used both as a self-teaching tool and as a general technical reference in the field.

The book presents a low-level approach. The authors believe that in the field of PC animation the low-level approach is more a necessity than an option. This statement seems to contradict the implications of many animation titles currently on the shelves; however, it is our experience that the immense majority of animation programmers in the PC environment are forced, sooner or later, into low-level programming by considerations of performance and control. Every experienced programmer knows that a statement such as "high-performance animation in Basic" or "lighting-fast animation routines in Pascal" is an oxymoron.

Unfortunately the same can be said about animation programming using operating system services. The typical animator is usually engaged in squeezing the last performance drop out of the hardware. There is nothing to waste in the complications, inefficiency, and control limitations of the interface calls of operating system services. It is under DOS, where the code has unrestricted and direct access to the CPU, the video hardware, and the other programmable components, that the best animation results are obtained. Since OS/2 and Windows NT can multitask DOS programs, it is possible to develop DOS applications that execute in these environments with few penalties. In the near future there will be few reasons for animation programming at the operating system level.

This does not mean that animated programs must be coded entirely in assembly language, although this is the case regarding many of the best present-day examples. Once the fundamental primitives and device drivers are available to the code, it is possible to compose the program in a high-level language, achieving acceptable performance by referencing core processing routines coded in assembler. Since this book includes a listing of these core device drivers and primitives, it can be of assistance to the animation programmer working in a high-level environment.

Before attempting to move objects on the video screen, the animation programmer must gain elementary skills in the field of computer graphics. In fact, animation is a specialty field of graphics programming, which implies that many animation techniques require knowledge of computer graphics. For this reason this book includes enough about PC graphics programming to hopefully make the described animation techniques more understandable and useful. On the other hand, this book is not a tutorial in computer graphics and often assumes elementary knowledge in graphics programming. The reader in need of graphics programming information can consult one of our titles on this

xii Preface

subject: Graphics Programming Solutions and High Resolution Video Graphics, both published by McGraw-Hill.

## **Organization**

The book is divided into three parts: Part One (Animation Fundamentals) includes Chapters 1 through 4. This first part serves as a general introduction to computer animation and to the supporting elements in computer graphics. Part Two (Animation Programming) includes Chapters 5 through 10. This part is a tutorial on VGA, SuperVGA, and XGA graphics. It includes a detailed analysis of the architecture of these systems as it relates to graphics and animation programming. In Part II we also develop the fundamental device drivers and primitives that are necessary to the animation code. Part III (Animation Techniques) describes the methods and techniques most often required by the PC animator. It also contains programming examples.

#### Conflict of Interest

The authors believe that it is unethical for a writer to hold back information or to condition the use of the software furnished in a text to copyrights or to the payment of additional fees. Software developers have legal rights to secrecy, to copyright privileges, and to sell their products on the marketplace. However, in our opinion, a writer's loyalty is to the reader and it would be a conflict of interest to write a text while influenced by commercial considerations regarding the material discussed. Therefore, the software developed by the authors and listed in this book can be copied freely, used as furnished, or modified by the reader, without crediting the authors or paying any additional charges. This statement does not include the copyrights on the book itself, nor does it refer to Shareware software, both of which are subject to other rules.

## **Acknowledgments**

In our years of teaching at Montana State University, Northern, we have been fortunate to interest some students in the fields of graphics and animation programming. In preparing this book we have had access to code and commercial programs developed by students Dale Niemeyer and David Oard. We thank them for this kindness and wish them luck in their professional endeavors.

The authors would also like to thank the friends and associates who provided advice, support, and assistance in this project. At McGraw-Hill, Jerry Papke, David Fogarty, and Gemma Velten have been involved in the production of this book

At Montana State University, Northern, we owe thanks to Dr. Karen LaRoe, Vice Chancellor for Academic Affairs, Dr. Richard Fisher, Director of the Great Falls campus, and Virgil Hawkinson, Division Chair, for their continued support of our writing projects. Our colleagues Kevin Carlson, Wes Tucker, Roger Stone, and Jay Howland have also made us feel their enthusiasm. Our thanks also go to Sharon Lowman.

Great Falls, Montana

Julio Sanchez Maria P. Canton

## **SOFTWARE ONLINE**

The source code listed in the text can be downloaded from the Montana State University, Northern BBS, in Havre, MT.

The BBS phone number is (406) 265-4184

The file is a self-extracting archive named COM\_ANI.EXE.

## **Computer Animation**

**Part**

1

# **Animation Fundamentals**

|  | 를 하시다.<br>현 - 현교를 보고 하는 것이다. |  |  |

|--|------------------------------|--|--|

|  |                              |  |  |

|  |                              |  |  |

|  |                              |  |  |

|  |                              |  |  |

|  |                              |  |  |

|  |                              |  |  |

|  |                              |  |  |

|  |                              |  |  |

|  |                              |  |  |

|  |                              |  |  |

|  |                              |  |  |

|  |                              |  |  |

|  |                              |  |  |

|  |                              |  |  |

|  |                              |  |  |

|  |                              |  |  |

|  |                              |  |  |

|  |                              |  |  |

|  |                              |  |  |

|  |                              |  |  |

|  |                              |  |  |

|  |                              |  |  |

Chapter

1

## The Dynamics of Computer Graphics

## 1.0 Digital Simulation of Movement

Computer animation can be defined as the simulation of movement or of lifelike actions by the manipulation of digital objects. The notion of digital simulation of movement is the core of this definition; however, as Magnenat-Thalmann and Thalmann have pointed out, computer animation can exist without the simulation of movement (see Bibliography), for example, in morphing (change of one object into another one) and in transformations produced by changes in color or lighting. In any case, this simulation of life has added an exciting dimension to computer graphics and to graphics programming, so that today, computer animated imagery is frequently found in applications related to art, science, and technology.

In the simulation of movement the computer can play two different roles: it can serve as an assistant in the creation of imagery destined for display in other media, or it can itself be the destination of the animated action. In the first case we speak of computer-assisted animation. An example of computer-assisted animation is a transformation called *morphing*. In this case the animator inputs two images: one of the face of a man and another one of a wolf face. The machine is programmed to generate a set of intermediate drawings that gradually change the first image into the second one. All the consecutive images generated by the computer, as well as the original ones, can be stored in video tape or film. When the stored images are played back in sequence, the man's face appears to gradually change into a wolf. This interpolation technique is now a common special effect in television and motion pictures.

But perhaps a more familiar notion of computer animation is that in which the computer is both the generator and the display instrument. This is particularly true in microcomputers, which have been used seldom commercially in animation-assistant roles due to their limitations in storage and processing power. We speak of real-time animation when the computer is the tool, as well

as the media. In this sense the imagery is generated and displayed in the user's own time frame; there is no image storage for later playback. The animation is shown "live" as it happens. Often the user interacts with the system to determine or modify the result. For example, a flight simulator program consists of animated imagery of the aircraft's cockpit and of the pilot's view thorough the windshield. The actions performed by the user in the simulated flying of the digital aircraft determine changes in the cockpit instruments and in the landscape seen through the windshield. In this case all the changes required for the animation take place in the user's (pilot) time frame.

In this chapter we describe the general principles, theory, and applications of computer animation. The material serves both as an introduction and as general background for the rest of the book. In preparing it we have relied heavily on the books Computer Animation: Theory and Practice and New Trends in Animation and Visualization. Nadia Magnenat-Thalmann and Daniel Thalmann are the authors of the first title and the editors of the second one. (See Bibliography.)

#### 1.1 Conventional Animation

Conventional animation refers mostly to the techniques used in two-dimensional cartoons often associated with Walt Disney, Hannah-Barbera, and others. The method consists of photographing a series of progressive drawings. The photographs are typically developed as color transparencies and animation achieved by successively projecting the transparencies on the screen. Although microcomputers are not used often in the production of cartoons, the technique is interesting to the graphics programmer since similar methods can be applied to real-life animation problems.

#### 1.1.1 Historical background

In 1831 a Frenchman named Joseph Antoine Plateau was able to create the illusion of movement by means of a machine which he called a *phenakistoscope*. The device consisted of a disk with a series of progressive drawings and windows. When the disk was rotated the viewer would see the drawings in rapid sequence, which created an illusion of movement. Three years later an Englishman named Horner modified the phenakistoscope into a device which he called the *zoetrope*. The zoetrope consisted of drum with drawings on its inner walls. A series of slits allowed the viewer to see the different drawings as the drum rotated. Emile Reynaud, another Frenchman, further refined the zoetrope by replacing the viewing slits with mirrors. This device was named the *praxisnoscope*.

Emile Reynaud founded the first movie theater in 1892. It was located in Paris and called the *Theater Optique*, although the first animated film was not produced until 1906. By 1913 several American companies were regularly producing cartoons for the thriving motion picture theaters. *Felix the Cat*, by

Pat Sullivan, is possibly the best known cartoon character of this era. Walt Disney, who is usually considered the father of animated cartoons, produced a *Mickey Mouse* film in 1928. This film was the first one to incorporate sound. *Donald Duck* and other characters followed shortly thereafter. *Snow White and the Seven Dwarfs* was the first feature film-length cartoon.

### 1.1.2 Cartoon Animation Techniques

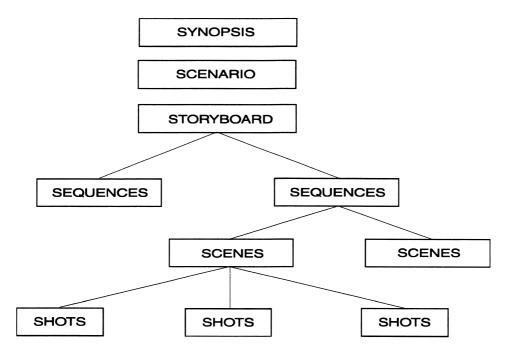

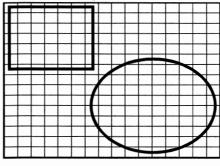

Computers are playing an expanding role in the commercial production of cartoons. Their use includes the coloring of drawings as well as the generation of intermediate images, an operation called *in-betweening* or *tweening*. Drawing and coloring and in-betweens are tedious and time-consuming operations when performed by hand. The organizational elements in the production of an animated cartoon can be seen in Figure 1.1.

The story told in the animated cartoon is developed in three progressively refined steps, shown in Figure 1.1. The *synopsis* is a short summary of the story, usually in less than one page. The *scenario* describes the story more completely and details the characters and the scenery. The *storyboard* consists of a series of drawings and captions that capture the most important moments depicted in the film.

Figure 1.1 Production Steps for an Animated Cartoon

From the storyboard it is possible to derive the film sequences. Each sequence refers to a film action and consists of one or more scenes, typically associated with a particular location and one or more characters. The units of cartoon execution are the individual shots that compose each scene. The production of each animated scene is performed by artists called animators who lay out, design, and draw the key images in each scene. At this time the sound track for the cartoon must have already been defined, since the motion of the animated figures takes place in relation to dialog and music.

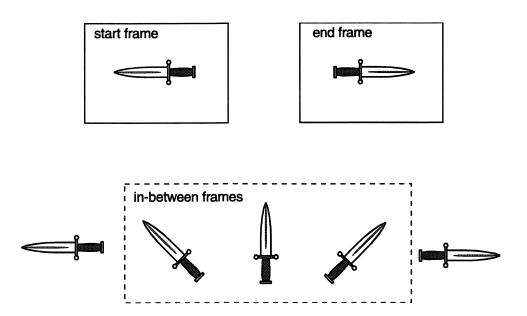

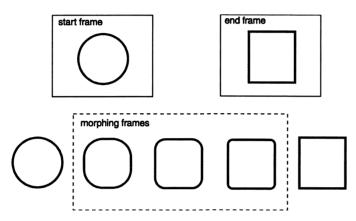

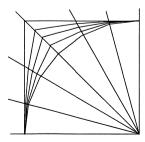

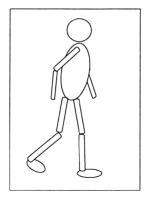

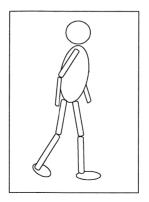

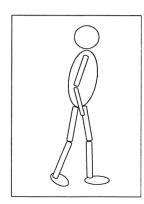

In the production of the actual drawings the artists use as reference two key positions, called frames. For example, Figure 1.2 represents the drawings used in a scene for an animated cartoon in which a dagger appears to travel from the hand of an imaginary thrower to an imaginary target. The key frames are the start frame and the end frame shown in Figure 1.2. The drawings that are necessary to animate the movement between both key frames are the in-between frames. In conventional animation in-betweening is a routine task usually performed by assistants to the animators.

In Figure 1.2 we have drawn three in-between frames. In reality the number of progressions between the start frame and the end frame of a sequence depends on the time assigned to the frame and the display rate. For example, if the animation of the clock sphere in Figure 1.2 is to take 1.5 seconds and the display rate is of 24 frames per second, then 36 frames are required for the animation, of which 34 are in-between frames.

Figure 1.2 Progressive Drawings in Cartoon Animation

Figure 1.3 Diagram of a Multiplane Camera

### 1.1.3 Photographic Manipulations in Cartoon Animation

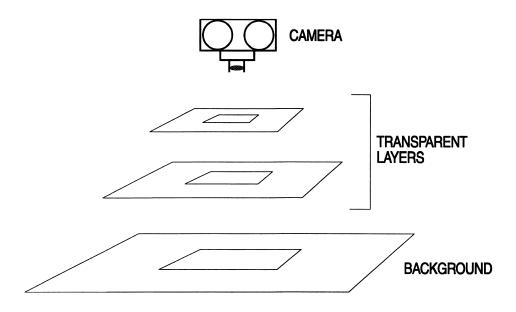

In addition to the progressive drawings that simulate movement, cartoonists can enhance the animation by means of photographic manipulations. The drawings for cartoon animation are made on a transparent plastic film. Therefore the clear portions of the drawing are invisible to the camera. The equipment used in the production of cartoons is a specialized motion picture camera called a *multiplane*. The animation surface consists of several glass layers at varying distances from the camera lens. Figure 1.3 is a schematic diagram of a multiplane camera.

The multiplane camera is used in creating various special effects. For example, the camera can be moved horizontally to pan an image or moved along the optic axis to enlarge or reduce the apparent size of an object (zooming). An effect called spin is created by rotating the camera. Several fade and dissolve effects are used in providing a soft transition between scenes. The fade-in is a progressive transition of the image from black and the fade-out a transition to black. The fade-in is typically used at the start of a scene and the fade-out at the conclusion.

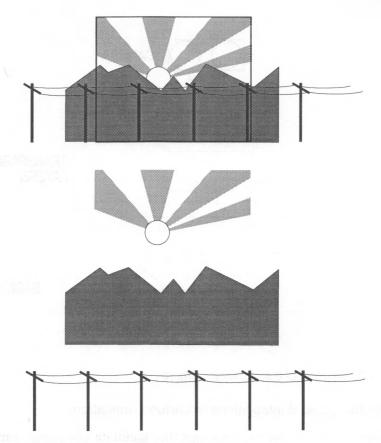

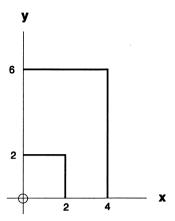

In multiplane animation the image is separated into several elements according to their distance from the viewer. For example, in animating the scenery visible from a moving train it is possible to divide the image into several strips, as shown in Figure 1.4.

Figure 1.4 Assembly of a Multiple-Plane Image

The landscape in Figure 1.4 is animated by moving the three image strips at different rates under the multiplane camera. In this case the image strip that depicts the rising sun remains stationary. The strip depicting the mountain range is moved slowly under the lens while the strip with the telephone poles is moved at a faster rate. The resulting animation would simulate the apparent movement of these objects as viewed by an observer on a train or automobile. Notice that the length of the images is proportional to their rate of movement during animation. Also that more image planes could be used to enhance the realism. The multiple-plane animation technique is quite suited to computer animation, as will be shown later in the book.

## 1.2 Computer Animation

Regarding animation the computer can assume one of two roles: it can assist in the creation of animated imagery (computer-assisted animation) or it can both generate and portray the animated action (real-time animation). The most

time-consuming and tedious task of cartoon animation is the generation of the many intermediate images required by the process (tweening). The computer plays the following assistant roles:

- During the drawing stage the computer is used to scan and digitize image elements and to create drawings or parts of drawings by means of draw or paint software.

- 2. In the animation process the computer is used to generate in-betweens and to color drawings.

- 3. During the photography stage the computer controls the multiplane camera and assists in the creation of special effects.

- 4. In the production stage the computer is used in editing and in adding sound to the animated film.

This list is by no means final. Every day animators find new uses for computers, new technologies are developed which create novel possibilities and applications in animated graphics. Computer technology is being used in the creation of spectacular special effects based on the digitization of screen objects, which are later manipulated by the software. Original efforts in this type of computer-assisted animation are found in the film *TRON*, produced by Walt Disney Studios, as well as in *Return of the Jedi*, by Lucasfilm. In recent years animation by image digitization has become the rule, rather than the exception. It can be found often in science fiction, action, and even conventional films.

### 1.2.1 Animating in Real Time

Real-time animation is found in arcade machines, simulators and trainers, electronic game machines such as those manufactured by Nintendo and Sega, and in interactive programs mainly intended for microcomputers. In real-time animation the computing machine serves both as image generator and as display media.

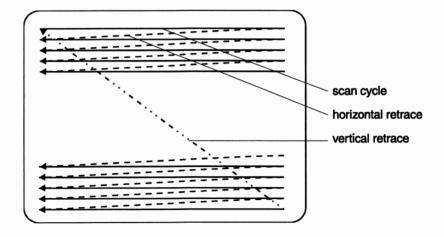

Animation is based on the physiological fact that the image of an object perceived by the human eye persists in the brain for a brief period of time after the object no longer exists in the real world. This phenomena, called *visual retention*, is related to the chemistry of the retina and to the structure of cells and neurons in the eye. Smooth animation is achieved in cinematography and television by consecutively displaying images at a faster rate than the period of visual retention. This operation, by which a new image replaces the old one before the period of retention has expired, creates in our minds the illusion of a smoothly moving object.

The period of visual retention is a few hundreds of a second. The critical image update rate for smooth animation has been determined to be between 22 and 30 images per second. Modern day moving picture films are recorded and displayed at a rate of 24 images per second. Commercial television takes place at a slightly faster rate. In general, the threshold rate, subject to individual variations, is estimated at 18 images per second. This means that if the consecutive images are projected at a rate slower than this threshold, the

average individual perceives a certain jerkiness in the animation. On the other hand, when the image rate equals or exceeds the threshold, our brains merge the images together and we perceive a smoothly animated action.

If we assume that computer animation must take place at an image rate of approximately 20 images per second, then each image must be updated and displayed in a maximum period of one-twentieth of a second. Furthermore, many forms of animation require that the old image be erased from the display before a new one is drawn; otherwise the animation would leave a visible track of objects on the video display. For this reason the image update sequence is a series of redraw, erase, redraw operations, which means that the critical display rate must be calculated from one redraw cycle to the next one. Consequently, the allotted time for the redraw or the erase operation is one-half the display rate, in this case one-fortieth of a second.

These constraints determine that computer animation is often a battle against time: the program is allowed a limited interval in which to update and redraw the image. The animation programmer resorts to every known trick and stratagem in order to squeeze the maximum performance while executing the image update and the display operations. However, quite frequently, even the most imaginative programming cannot overcome the system's limitations. In this case the result is a bumpy and coarse real-time animation that is but a remote likeness of cinematography and television.

As microcomputer systems and video display hardware become more efficient and powerful, the possibilities of real-time animation expand. In our tests we have found that in a 486-based microcomputer with XGA display hardware it is possible to smoothly animate an image that is 40 times larger than the one that could be handled in a 286-based VGA system. On the other hand, commercial software products must aim at the largest possible group of potential customers. This means that the designers of animated programs often aim at ensuring satisfactory execution even in the more primitive systems. For this practical reason, animated programs that squeeze the maximum performance out of state-of-the-art systems are not readily available, since their customer base would be considerably restricted.

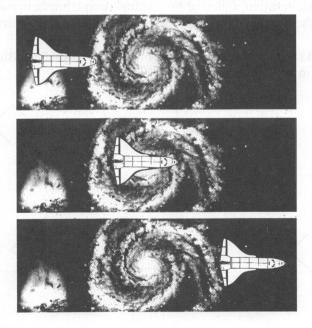

#### 1.2.2 Frame-by-Frame Animation

Many of the techniques used in computer-assisted animation can be described as frame-by-frame operations. In frame-by-frame animation the computer generates the required images, which are recorded or stored for playback at a later time. This playback can take place in the same machine that generated the image set or in another media. For example, a computer can be used to manipulate the image strips in Figure 1.4 so as to generate a set of 100 progressive pictures. As the images are generated, they are recorded in video tape. When the image set is complete, the animation can be viewed by playing back the video tape. Alternatively the images can be stored in computer memory or disk and played back in the same machine that generated them. In either case the animation is less demanding of machine processing power since the

image creation step need not take place in real time. However, if the computer is used to play back the image set, then this operation is subject to the real-time constraints mentioned in the preceding section.

#### 1.2.3 Interactive Animation

Interactive animation refers to computer objects that are moved at the user's desire. At present, the most common interactive devices in microcomputers are the keyboard and the mouse, although joysticks and other devices are often used with the more sophisticated games and simulations. In general, the notion of interactive animation includes any technology in which the user exercises some level of control over computer-animated action. By today's standards the ultimate level of interactive animation is called *virtual reality*, a topic discussed in Section 1.4.5.

### 1.2.4 Random or Unpredictable Elements in Animation

Conventionally, the computer simulation of movement is based on programmable or predictable stages. In this manner, the cartoon animator knows beforehand (from the storyboard) all the actions and interactions that will be portrayed in the final rendition. Even in most implementations of virtual reality, every result can be predicted from the user's interaction with the device. Therefore we can say that the system is, by nature, deterministic.

However, many natural systems are of a different nature. Biology students often observe that colonies of bacteria developing in identical media show different patterns of growth. This is due to the fact that in a complex biological system many development factors cannot be determined a priori. In other words, random or unpredictable elements often influence the development of a biosystem. Some modern geologists claim that the disappearance of the dinosaurs was caused by the collision of an asteroid with the earth. If this hypothesis is true, then a small change in the trajectory of the asteroid would have made it miss our planet. Consequently, the evolution of life on earth would have followed an entirely different path.

We have used the terms random or unpredictable regarding biosystems due to the fact that the preference of one or another term would imply a philosophical judgment. For example, during reproduction, the genes in the male and female chromosomes combine to form the genetic structure of the offspring. If these genes combined according to fixed rules, all siblings would be identical. This is certainly not the case; furthermore, we have no way of knowing beforehand the offspring's exact genetic makeup. Therefore, the mechanics of gene exchange during reproduction can be considered as a random action.

Statistics often serve to describe the unpredictable behavior of a biosystem. For example, in the above-mentioned gene exchange it is often possible to determine, according to their location in the chromosome, that certain genes are more or less likely to be transmitted. However, anything less than absolute certainty implies randomness or unpredictability. If a computer were to simu-

late the reproduction of a biosystem, it would have to take into consideration these random or unpredictable factors.

## 1.3 Motion Control Techniques

If computer animation is roughly equated with the screen simulation of movement, the methodology for producing the animated effect can be described as a set of motion control techniques. In this respect Allan and Mark Watt, in their book *Advanced Animation and Rendering Techniques* (see Bibliography), refer to procedural, representational, stochastic, and behavioral as the main categories of the animation hierarchy.

From a programmer's viewpoint, animation is implemented by applying one of many low-level methods of motion simulation and control. Some of these methods have been passed on by cartoon animators, while others are digital in nature and, therefore, unique products of the computer environment.

The computer animator is confronted by many limitations and constraints. The most common approach is based on the axiom "whatever works, works." Very often the animation is produced by means of mathematical transformations on the parameters that define one or more screen images. Since movement is a function of time, the laws of physics are often taken into account. For example, in representing a falling object the animator may use the formula that expresses acceleration in a gravitational field to determine the rate of in-betweening that most naturally represents the action. On the other hand, artistic considerations could determine an intentional variation from the physical laws of motion. J. E. Gomez mentions in an article titled "Comments on Event Driven Animation" that the animator is not constrained to obey physical laws; Wily Coyote walks on air for a few seconds before beginning to fall.

## 1.3.1 Tweening and Morphing

The cartoon animator proceeds from two key positions, known as frames, and creates a set of in-between drawings (see Figure 1.2). The entire sequence is photographed and projected to create an illusion of movement. The depiction of animated action by creating and projecting a set of in-between drawings is often called *tweening*; in this sense the intermediate drawings are the *tweens*. Computer animators have successfully borrowed the tweening technique from cartoon animators. Furthermore, in a computer environment the machine can often aid in the creation of the in-between frames by performing geometrical transformations on the key frames.

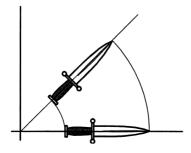

The tweening required for representing the flight of the dagger shown in Figure 1.2 can be obtained by rotating and translating the start frame. If the image of the dagger is stored in a specific manner, then the animation is produced by mathematical manipulations of a single image file. In Chapter 2 we begin discussing the storage of graphics images in data structures that

permit their mathematical manipulations at display time. This subject is revisited on many occasions throughout the book.

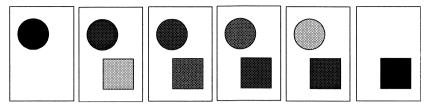

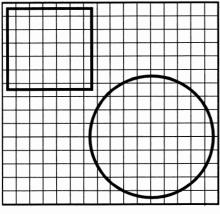

Another technique that originated in cartoon animation is called *morphing*. The term relates to the notion of metamorphosis: a transformation in shape, form, or substance that takes place by biological change or by magic and sorcery. Morphing techniques are being extensively used in motion pictures. We are all familiar with the image of an actor or actress transforming into a wolf or a cat. Figure 1.5 shows the morphing of a circle into a square.

Figure 1.5 Morphing Animation

#### 1.3.2 Path-of-Motion Calculations

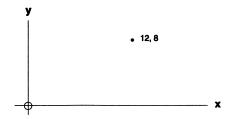

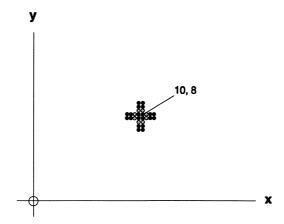

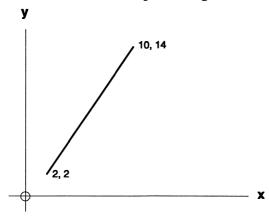

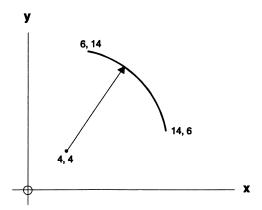

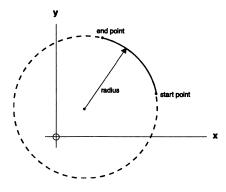

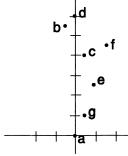

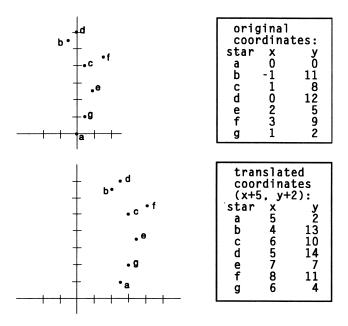

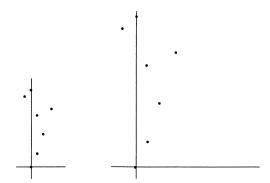

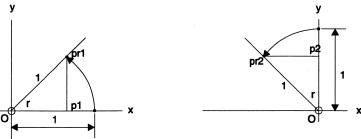

The rules for path-of-motion calculations in animation depend on the image file encoding and on the transformation to be performed. If the coordinate points that define the image are stored in matrix form, then it is possible to perform certain transformations by means of matrix arithmetic. For example, a translation transformation consists of adding a constant value to each coordinate point that defined the object, while a rotation transformation consists of moving all of the object's coordinate points along circular arcs with a common center. Figure 1.6 shows the rotation transformation of the dagger depicted earlier in this chapter.

Figure 1.6 A Rotation Transformation

Figure 1.7 Path of Motion in a Morphing Transformation

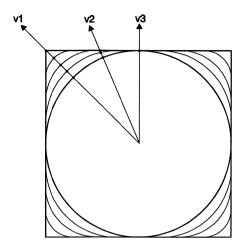

As in tweening, some morphing transformations can be assisted by manipulations of the image file. On the other hand, in morphing, the intermediate frames are determined according to different rules than in tweening. For example, the morphing transformation of a circle into a square shown in Figure 1.5 cannot be made by simple rotation and translation, as is the case in the tweening shown in Figure 1.2. Figure 1.7 shows the path, along a 45-degree vector, that a point on the circle would follow in the process of morphing into a square.

In Figure 1.7, points along different vectors follow different paths. For this reason, morphing usually requires more complicated processing than simple geometrical transformations. Notice that the path of motion along vector  $\mathbf{v1}$  in Figure 1.7 requires three intermediate steps in the transformation of a circle into a square. Along vector  $\mathbf{v2}$  only one intermediate step is necessary, while there is no motion along vector  $\mathbf{v3}$ .

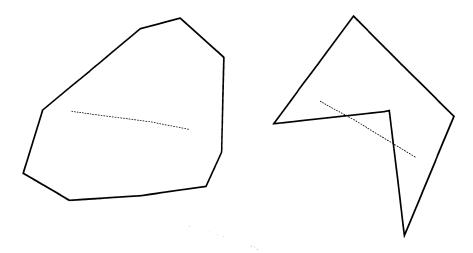

Path-of-motion calculations in tweening and morphing can be rationalized and simplified by using straight lines to approximate geometrical curves. A polygon can be used instead of the circles and curves in the morphing transformation of a circle into a square. This approximation is shown in Figure 1.8.

Figure 1.8 Polygon Approximations in Morphing

Figure 1.9 Simultaneous Fade-in and Fade-out

#### 1.3.3 Color-Shift Animation

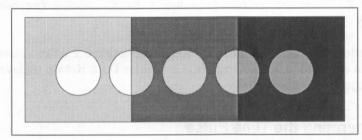

Objects on the computer screen are furnished with display attributes. In color video systems one category of attributes is the object's color. The animator can manipulate the color attributes of screen objects to create the illusion of movement or change. One common application of this technique is in *fading*. An object or scene is faded-in when its color is progressively changed so as to make it slowly appear on the screen. A fade-out takes place when the object or scene is made to slowly disappear from the screen. Fade-in operations are typically used in cinematography at the beginning of a scene and fade-out at the end of a scene. A cross-dissolve operation takes place when one scene or object is faded-out while another one is faded-in. Figure 1.9 shows the simultaneous fade-in of a rectangle and fade-out of a circle.

In some computer system fade operations can be implemented by progressively changing the hue or saturation of one or more objects or of the entire scene. A screen fade-out can be accomplished by progressively increasing the white saturation of all the objects until the entire screen is white. In some systems (including IBM video systems) the fades can be performed by modifying the color palette itself, instead of the color attributes of individual objects. Palette animation, as these methods are sometimes called, is relatively easy to implement and often generates satisfactory results at a low processing cost.

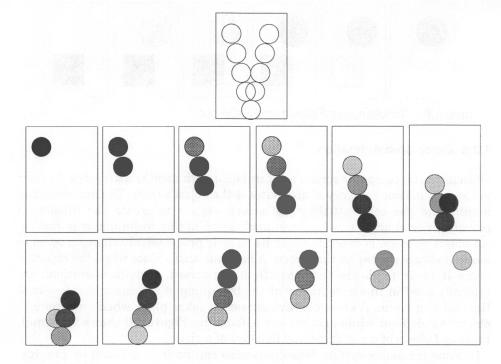

Color animation is also used in many other creative manipulations. For example, a sunset scene can be created by increasing the black, red, and orange color saturation of selected screen objects. Or the illusion of movement can be enhanced by having the moving object leave tracks of its image with a decreasing color saturation. This effect, sometimes called a motion blur, is depicted by the bouncing ball shown in Figure 1.10.

### 1.3.4 Object Rendering

In the creation of the image set the animator is often confronted with a modeling problem. As the number of dimensions of the representation and the complexity of the objects increase, so do the difficulties in obtaining the in-between images or the mathematical transformations required for the animation. As a general rule it can be stated that two-dimensional objects are easier to model than three-dimensional ones, symmetrical objects are easier than asymmetrical ones, and geometrical entities are easier than living organisms. However, notice that there are exceptions to these rules.

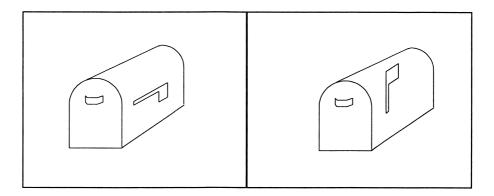

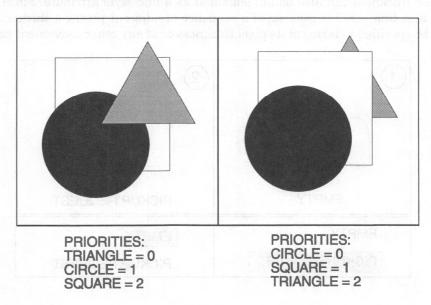

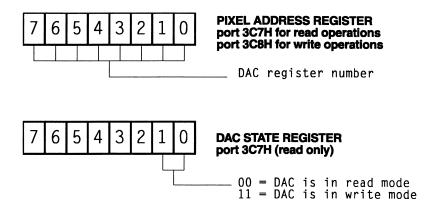

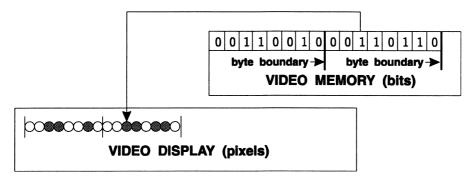

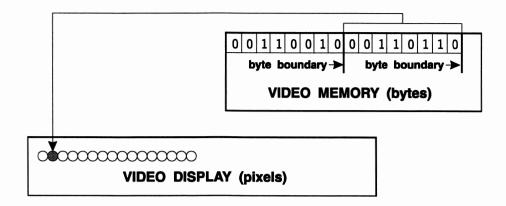

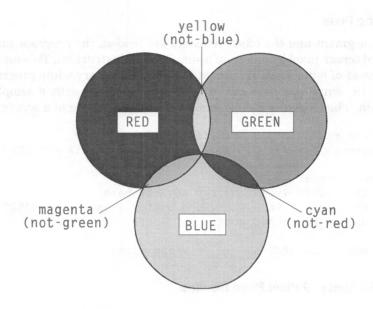

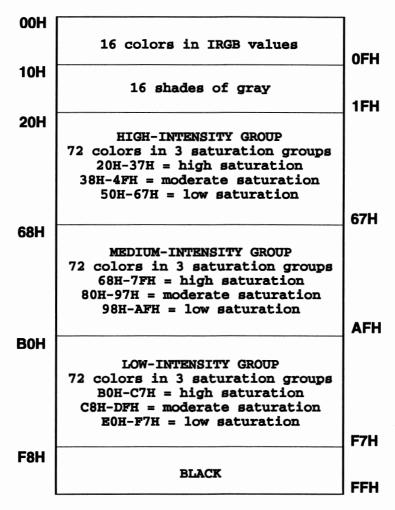

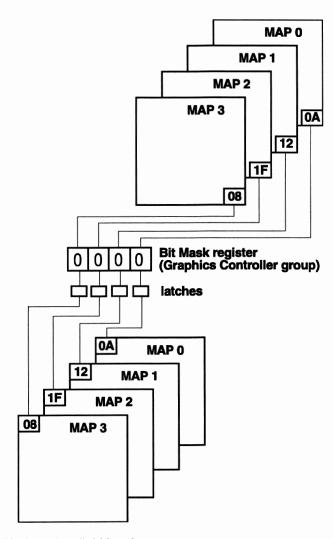

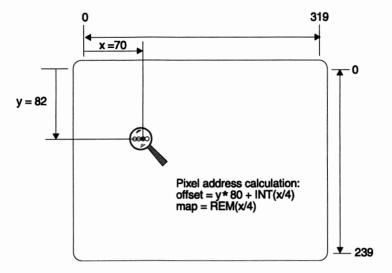

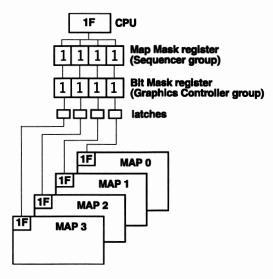

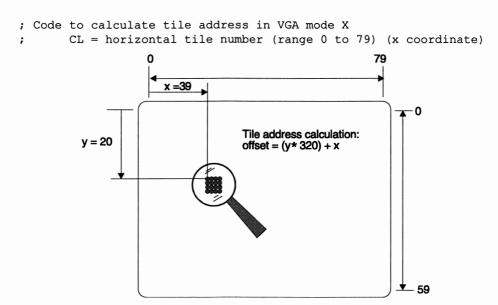

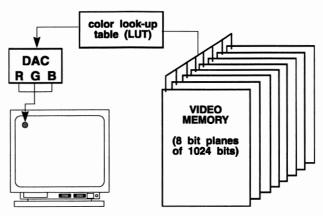

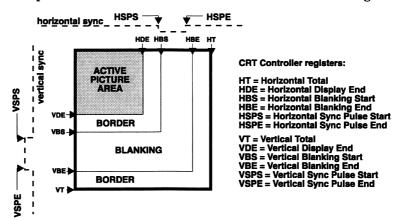

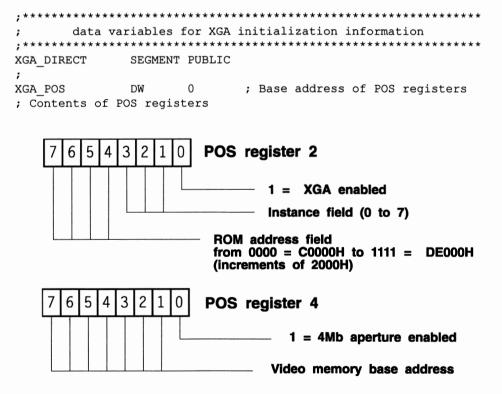

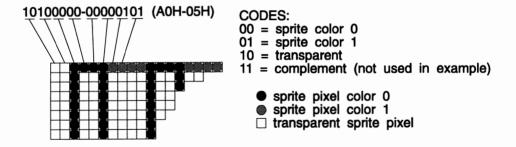

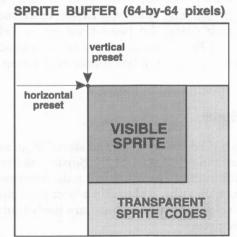

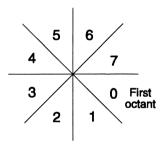

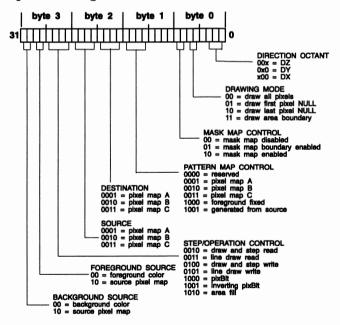

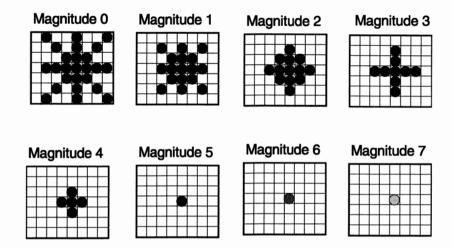

Figure 1.10 Motion Blur Effect